电平移位器、选通驱动电路和显示装置的制作方法

1.本公开涉及一种电平移位器(level shifter)、选通驱动电路和显示装置。

背景技术:

2.随着信息社会的到来,对用于显示图像的显示装置的需求不断增长。为了满足这样的需求,近来,已经开发和广泛使用了诸如液晶显示(lcd)装置、包括量子点发光显示装置的电致发光显示(eld)装置和有机发光显示(例如,oled)装置等的各种类型的显示装置。

3.通常,显示装置对设置在显示面板上布置的多个子像素中的每一个中的电容器进行充电,并且将经充电的电容用于显示驱动。然而,在这种典型的显示装置中,每个子像素中的这种电容器可能充电不足,并且由此导致图像质量劣化。

4.在典型的显示装置中,如果能够减小显示面板的非显示区域的尺寸,则可以增加显示装置的设计自由度并且可以提高设计质量。然而,由于在显示面板的非显示区域内布置了各种线路和电路元件,实际上,减小显示面板的非显示区域的尺寸并不容易。

5.另外,在这种典型的显示装置的情况下,充电时间不足可能会导致图像质量变差,并且此外,由于选通信号特性的差异,选通驱动可能会出现故障,从而导致图像质量变差。

技术实现要素:

6.本公开的实施方式提供了一种能够减小选通信号之间的特性差异,并且因此提高图像质量的电平移位器、选通驱动电路和显示装置。

7.本公开的实施方式提供了一种能够对时钟信号的上升特性和下降特性进行各种控制的电平移位器、以及使用该电平移位器的选通驱动电路和显示装置。

8.本公开的实施方式提供了一种即使在选通驱动电路作为嵌入类型嵌入显示面板中时,也能够减小其中设置选通驱动电路的区域的尺寸,并且减小选通信号之间的特性差异的电平移位器、选通驱动电路和显示装置。

9.根据本公开的各方面,提供了一种显示装置,该显示装置包括:基板;m条选通线,该m条选通线设置在基板上,其中,m为2或更大的自然数;以及选通驱动电路,该选通驱动电路设置在基板上或连接到基板,并且能够基于输入的m个时钟信号向m条选通线提供m个选通信号。

10.选通驱动电路可以包括能够基于m个时钟信号输出m个选通信号的m个输出缓冲器电路,以及能够控制m个输出缓冲器电路的控制电路。

11.m个输出缓冲器电路中的每一个可以包括上拉晶体管和下拉晶体管,并且上拉晶体管和下拉晶体管连接所在的点可以与m条选通线中的对应选通线电连接。

12.包括在m个输出缓冲器电路中的各个上拉晶体管的所有栅极节点可以电连接在一起,并且包括在m个输出缓冲器电路中的各个下拉晶体管的所有栅极节点可以电连接在一起。

13.m个时钟信号中的至少一个时钟信号的信号波形可以与m个时钟信号中的另一个

时钟信号的信号波形不同。

14.m个选通信号可以包括在最早定时具有导通电平电压持续时间的第一选通信号和在最晚定时具有导通电平电压持续时间的第m选通信号。

15.m个时钟信号可以包括与第一选通信号相对应的第一时钟信号和与第m选通信号相对应的第m时钟信号。

16.第一时钟信号的下降长度可以长于第m时钟信号的下降长度。在这种情况下,第一选通信号的下降长度与第m选通信号的下降长度之间的差可以小于第一时钟信号的下降长度与第m时钟信号的下降长度之间的差。

17.第m时钟信号的上升长度可以长于第一时钟信号的上升长度。在这种情况下,第一选通信号的上升长度与第m选通信号的上升长度之差可以小于第一时钟信号的上升长度与第m时钟信号的上升长度之差。

18.根据本公开的各方面的显示装置还可以包括用于根据时钟差异控制信号输出m个时钟信号的电平移位器。

19.在根据本公开的各方面的显示装置中,m可以是2或4。

20.根据本公开的各方面,提供一种包括能够基于m个时钟信号输出m个选通信号的m个输出缓冲器电路和能够控制m个输出缓冲器电路的控制电路的选通驱动电路。

21.m个输出缓冲器电路中的每一个可以包括上拉晶体管和下拉晶体管,并且上拉晶体管和下拉晶体管连接所在的点可以与m条选通线中的对应选通线电连接。

22.包括在m个输出缓冲器电路中的各个上拉晶体管的所有栅极节点可以电连接。

23.包括在m个输出缓冲器电路中的各个下拉晶体管的所有栅极节点可以电连接。

24.m个时钟信号中的至少一个时钟信号的信号波形可以与另一时钟信号的信号波形不同。

25.根据本公开的各方面,提供了一种包括用于输出m个时钟信号的m个时钟输出缓冲器的电平移位器。

26.在电平移位器中,m可以是2或更大的自然数,并且m个时钟信号可以包括第一时钟信号至第m时钟信号。

27.第一时钟信号的高电平电压持续时间和第二时钟信号的高电平电压持续时间可以部分交叠。

28.m个时钟信号中的第一时钟信号的信号波形可以与第m时钟信号的信号波形不同。

29.m个时钟输出缓冲器可以包括用于输出第一时钟信号的第一时钟输出缓冲器和用于输出第m时钟信号的第m时钟输出缓冲器。

30.第一时钟输出缓冲器可以包括第一上升控制电路和第一下降控制电路,第一上升控制电路包括电连接在高电平电压节点和第一时钟输出端子之间的n个第一上升控制晶体管(n是2或更大的自然数),并且第一下降控制电路包括电连接在低电平电压节点和第一时钟输出端子之间的n个第一下降控制晶体管。

31.第m时钟输出缓冲器可以包括第m上升控制电路和第m下降控制电路,第m上升控制电路包括电连接在高电平电压节点和第m时钟输出端子之间的n个第m上升控制晶体管,并且第m下降控制电路包括电连接在低电平电压节点和第m时钟输出端子之间的n个第m下降控制晶体管。

32.包括在第一上升控制电路、第一下降控制电路、第m上升控制电路和第m下降控制电路中的至少一个中的n个控制晶体管的相应导通和截止可以被独立控制。

33.第一时钟信号的下降长度可以大于第m时钟信号的下降长度。在这种情况下,n个第一下降控制晶体管当中的导通的下降控制晶体管的数量可以小于n个第m下降控制晶体管当中的导通的下降控制晶体管的数量。

34.第m时钟信号的上升长度可以大于第一时钟信号的上升长度。在这种情况下,n个第m上升控制晶体管当中的导通的上升控制晶体管的数量可以小于n个第一上升控制晶体管当中的导通的上升控制晶体管的数量。

35.根据本公开的实施方式,可以提供一种能够减小选通信号之间的特性差异并且因此提高图像质量的电平移位器、选通驱动电路和显示装置。

36.根据本公开的实施方式,可以提供一种能够对时钟信号的上升特性和下降特性进行各种控制的电平移位器以及使用该电平移位器的选通驱动电路和显示装置。

37.根据本公开的实施方式,可以提供即使当选通驱动电路作为嵌入类型嵌入显示面板中时,也能够减小其中设置选通驱动电路的区域的尺寸并且减小选通信号之间的特性差异的电平移位器、选通驱动电路和显示装置。

附图说明

38.附图被包括在内以提供对本公开的进一步理解并且被并入并构成本公开的一部分,附图例示了本公开的各方面并且与描述一起用于解释本公开的原理。在附图中:

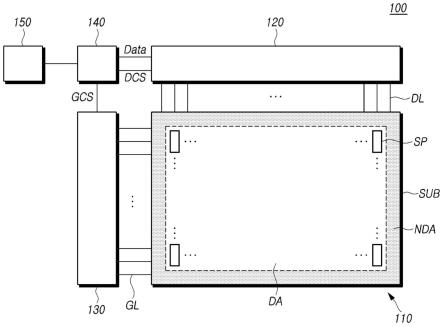

39.图1例示了根据本公开的各方面的显示装置的系统配置;

40.图2a和图2b例示了根据本公开的各方面的显示装置的子像素的等效电路;

41.图3例示了根据本公开的各方面的显示装置的示例系统实现;

42.图4a例示了根据本公开的各方面的显示装置的示例选通信号输出系统;

43.图4b例示了根据本公开的各方面的显示装置的示例选通驱动电路;

44.图4c例示了根据本公开的各方面的显示装置中的时钟信号和q节点处的电压;

45.图4d例示了根据本公开的各方面的显示装置中的选通信号之间的特性差异;

46.图4e例示了根据本公开的各方面的显示装置中的对选通信号之间的特性差异的补偿;

47.图5例示了根据本公开的各方面的显示装置的示例选通信号输出系统;

48.图6a和图6b例示了根据本公开的各方面的显示装置的示例选通驱动电路;

49.图7例示了根据本公开的各方面的显示装置中的特性差异;

50.图8a至图8c例示了根据本公开的各方面的在显示装置中补偿选通信号之间的特性差异的功能;

51.图9是根据本公开的各方面的显示装置的电平移位器的框图;

52.图10a至图10d是例示根据本公开的各方面的显示装置的电平移位器的第一时钟输出缓冲器的示例电路;

53.图11a至图11d是例示根据本公开的各方面的显示装置的电平移位器的第二时钟输出缓冲器的示例电路;

54.图12是根据本公开的各方面的用于补偿显示装置中的选通信号之间的下降特性

差异的电平移位器的详细示图;

55.图13例示了根据图12的电平移位器的n个第一下降控制晶体管当中导通的第一下降控制晶体管的数量的第一时钟信号的下降长度;

56.图14是根据本公开的各方面的用于补偿显示装置中的选通信号之间的下降特性差异和上升特性差异的电平移位器的详细示图;

57.图15例示了根据图14的电平移位器的n个第一下降控制晶体管当中导通的下降控制晶体管的数量的第一时钟信号的下降长度和根据其n个第二上升控制晶体管当中导通的上升控制晶体管的数量的第二时钟信号的上升长度;

58.图16例示了根据本公开的各方面的显示装置的示例选通信号输出系统;

59.图17例示了图16的选通信号输出系统中的示例选通驱动电路;

60.图18例示了图16的选通信号输出系统中的选通信号之间的特性差异;

61.图19例示了对图16的选通信号输出系统中的选通信号之间的特性差异的补偿;

62.图20是图16的选通信号输出系统中的电平移位器的框图;

63.图21是图19的电平移位器的详细示图;

64.图22例示了根据本公开的各方面的在显示装置中使用电阻器对选通信号之间的特性差异的补偿;

65.图23a至图23e例示了根据本公开的各方面的包括在显示装置中的通过电阻器的控制来控制和输出时钟信号的电平移位器;

66.图24是例示了根据本公开的各方面的用于控制包括在显示装置中的电平移位器中的开关的电阻水平的控制信号;

67.图25例示了根据本公开的各方面在显示装置中在如图6a和图6b中的q节点共享结构的情况下对选通信号之间的特性差异的补偿效果;以及

68.图26例示了根据本公开的各方面在显示装置中在如图17中的q节点共享结构的情况下对选通信号之间的特性的差异的补偿效果。

具体实施方式

69.在以下对本公开的示例或实施方式的描述中,将参照附图,其中通过说明的方式示出可以实现的具体示例或实施方式,并且其中即使在彼此不同的附图中示出,相同的附图标记和符号可以用于表示相同或相似的组件。此外,在本公开的示例或实施方式的以下描述中,当确定描述可能使本公开的一些实施方式中的主题变得不清楚时,将省略对在本文中结合的公知功能和组件的详细描述。除非与术语“仅”一起使用,否则本文中使用的诸如“包括”、“具有”、“包含”、“构成”、“组成”和“形成”等术语通常旨在允许添加其它组件。如本文所使用的,除非上下文另有明确指示,否则单数形式旨在包括复数形式。

70.诸如“第一”、“第二”、“a”、“b”、“(a)”或“(b)”的术语可以在本文中用于描述本公开的元件。这些术语中的每一个都不用于定义元件的本质、顺序、次序或数量等,而仅用于将对应元件与其它元件区分开来。

71.当提到第一元件“连接或联接到”第二元件、与第二元件“接触或交叠”等时,应当理解为,第一元件不仅可以“直接连接或联接到”第二元件或与第二元件“直接接触或交叠”,而且第三元件也可以“插置”在第一元件和第二元件之间,或者第一元件和第二元件可

以经由第四元件彼此“连接或联接”、“接触或交叠”等。这里,第二元件可以包括在彼此“连接或联接”、“接触或交叠”等的两个或更多个元件中的至少一个中。

72.当诸如“之后”、“随后”、“接下来”、“之前”等与时间相对术语用于描述元件或配置的过程或操作或者操作、处理、制造方法中的流程或步骤时,除非与术语“直接”或“立即”一起使用,否则这些术语可以用于描述非连续或非顺序的过程或操作。

73.此外,当提到任何尺寸、相对尺寸等时,应当认为,即使没有指定相关描述,针对元件或特征的数值,或对应信息(例如,级别、范围等)包括可能由各种因素(例如,过程因素、内部或外部影响、噪声等)引起的容差或误差范围。此外,术语“可以”完全包含术语“可能”的所有含义。

74.图1例示了根据本公开的各方面的显示装置100的系统配置。

75.参照图1,根据本公开的各方面的显示装置100包括显示面板110和用于驱动显示面板110的驱动电路。

76.驱动电路可以包括数据驱动电路120、选通驱动电路130等,并且还包括用于控制数据驱动电路120和选通驱动电路130的控制器140。

77.显示面板110可以包括基板sub和设置在基板sub上的诸如多条数据线dl、多条选通线gl等的信号线。显示面板110可以包括连接到多条选通线gl和多条数据线dl的多个子像素sp。

78.显示面板110可以包括其中显示图像的显示区域da和其中不显示图像的非显示区域nda。在显示面板110中,用于显示图像的多个子像素sp可以被设置在显示区域da中,并且驱动电路120、130和140可以电连接到或安装在非显示区域nda中。连接到集成电路或印刷电路的焊盘部分可以设置在显示面板110的非显示区域nda中。

79.数据驱动电路120是用于驱动多条数据线dl的电路,并且可以向多条数据线dl提供数据信号。选通驱动电路130是用于驱动多条选通线gl的电路,并且可以向多条选通线gl提供选通信号。控制器140可以向数据驱动电路120提供数据控制信号dcs以控制数据驱动电路120的操作定时。控制器140可以向选通驱动电路130提供选通控制信号gcs以控制选通驱动电路130的操作定时。

80.控制器140根据在每一帧中调度的定时开始扫描操作,将从其它装置或其它图像提供源(例如,主机系统)输入的图像数据转换为数据驱动电路120中使用的数据信号形式并然后将经转换的图像数据data提供给数据驱动电路120,并且根据扫描定时控制在预先配置的时间将数据加载到至少一个像素。

81.除了输入图像数据之外,控制器140可以从其它装置、网络或系统(例如,主机系统150)接收包括垂直同步信号vsync、水平同步信号hsync、输入数据使能信号de、时钟信号clk等的多种类型的定时信号。

82.为了控制数据驱动电路120和选通驱动电路130,控制器140可以接收诸如垂直同步信号vsync、水平同步信号hsync、输入数据使能信号de、时钟信号clk等的定时信号中的一个或更多个,生成多种类型的控制信号dcs和gcs并且将所生成的信号输出到数据驱动电路120和选通驱动电路130。

83.例如,为了控制选通驱动电路130,控制器140可以输出包括选通起始脉冲gsp、选通移位时钟gsc、选通输出使能信号goe等的多种类型的选通控制信号gcs。

84.此外,为了控制数据驱动电路120,控制器140可以输出包括源极起始脉冲ssp、源极采样时钟ssc、源极输出使能(soe)信号等的多种类型的数据控制信号dcs。

85.控制器140可以被实现为与数据驱动电路120分离的组件或者与数据驱动电路120集成,并且被实现在集成电路中。

86.数据驱动电路120可以通过从控制器140接收图像数据data并且向多条数据线dl提供数据电压来驱动多条数据线dl。这里,数据驱动电路120也可以被称为源极驱动电路。

87.数据驱动电路120可以包括一个或更多个源极驱动器集成电路sdic。

88.每个源极驱动器集成电路sdic可以包括移位寄存器、锁存电路、数模转换器dac、输出缓冲器等。在一些情况下,每个源极驱动器集成电路sdic还可以包括模数转换器adc。

89.在一些实施方式中,每个源极驱动电路sdic可以以带式自动接合(tab)类型连接到显示面板110,或者以玻璃上芯片(cog)类型或面板上芯片(cop)类型连接到显示面板110的导电焊盘(例如,接合焊盘),或者以膜上芯片(cof)类型连接到显示面板110。

90.选通驱动电路130可以根据控制器140的控制输出导通电平电压的选通信号或截止电平电压的选通信号。选通驱动电路130可以通过向多条选通线gl依次提供导通电平电压的选通信号来依次驱动多条选通线gl。

91.在一些实施方式中,选通驱动电路130可以以带式自动接合(tab)类型连接到显示面板110,或者以玻璃上芯片(cog)类型或面板上芯片(cop)类型连接到显示面板110的导电焊盘(例如,接合焊盘),或者以膜上芯片(cof)类型连接到显示面板110。在另一实施方式中,选通驱动电路130可以以面板内栅极(gip)类型位于显示面板110的非显示区域nda中。选通驱动电路130可以设置在基板sub上或上方,或者连接到基板sub。也就是说,在gip类型的情况下,选通驱动电路130可以被设置在基板sub的非显示区域nda中。在玻璃上芯片(cog)类型、膜上芯片(cof)类型等的情况下,选通驱动电路130可以连接到基板sub。

92.数据驱动电路120和选通驱动电路130中的至少一个可以被设置在显示区域da中。例如,数据驱动电路120和选通驱动电路130中的至少一个可以被设置为不与子像素sp交叠,或者设置为与子像素sp中的一个或更多个或全部交叠。

93.当特定的选通线被选通驱动电路130选择性地驱动时,数据驱动电路120可以将从控制器140接收的图像数据data转换为模拟形式的数据电压,并且将经转换的数据电压提供给多条数据线dl。

94.数据驱动电路120可以位于但不限于显示面板110的仅一部分(例如,上部部分或下部部分)上。在一些实施方式中,根据驱动方案、面板设计方案等,数据驱动电路120可以位于但不限于面板110的两个部分(例如,上部部分和下部部分)或面板110的四个部分(例如,上部部分、下部部分、左侧和右侧)中的至少两个部分上。

95.选通驱动电路130可以位于但不限于显示面板110的仅一部分(例如,左侧或右侧)上。在一些实施方式中,根据驱动方案、面板设计方案等,选通驱动电路130可以位于但不限于面板110的两个部分(例如,左侧或右侧)或面板110的四个部分(例如,上部部分、下部部分、左侧和右侧)中的至少两个部分上。

96.控制器140可以是在典型的显示器技术中使用的定时控制器或者除了定时控制器的典型功能之外能够另外执行其它控制功能的控制设备/装置。在一些实施方式中,控制器140可以是与定时控制器不同的一个或更多个其它控制电路,或者是控制设备/装置中的电

路或组件。控制器140可以使用诸如集成电路(ic)、现场可编程门阵列(fpga)、专用集成电路(asic)和/或处理器等的各种电路或电子组件来实现。

97.控制器140可以安装在印刷电路板、柔性印刷电路等上,并且可以通过印刷电路板、柔性印刷电路等电连接到数据驱动电路120和选通驱动电路130。

98.控制器140可以经由一个或更多个预定接口向数据驱动电路120发送信号和从数据驱动电路120接收信号。在一些实施方式中,这种接口可以包括低压差分信令(lvds)接口、epi(嵌入式始终点对点接口)接口、串行外围接口(spi)等。

99.控制器140可以包括诸如一个或更多个寄存器的储存介质。

100.根据本公开的各方面的显示装置100可以是诸如液晶显示装置等的包括背光单元的显示器,或者可以是诸如有机发光二极管(oled)显示器、量子点(qd)显示器、微型发光二极管(m-led)显示器等的自发光显示器。

101.在根据本公开的各方面的显示装置100是oled显示器的情况下,每个子像素sp可以包括oled,其中oled本身作为发光元件发光。在根据本公开的各方面的显示装置100是qd显示器的情况下,每个子像素sp可以包括发光元件,该发光元件包括作为自发光半导体晶体的量子点。在根据本公开的各方面的显示装置100是微型led显示器的情况下,每个子像素sp可以包括微型led,其中微型oled本身发光并且基于作为发光元件的无机材料。

102.图2a和图2b例示了根据本公开的各方面的针对显示装置100的子像素sp的示例等效电路。

103.参照图2a,根据本公开的各方面,设置在显示装置100的显示面板110中的多个子像素sp中的每一个可以包括发光元件ed、驱动晶体管drt、扫描晶体管sct和储存电容器cst。

104.参照图2a,发光元件ed可以包括像素电极pe和公共电极ce,并且包括位于像素电极pe和公共电极ce之间的发光层el。

105.发光元件ed的像素电极pe可以是设置在每个子像素sp中的电极,并且公共电极ce可以是公共地设置在子像素sp中的全部或一些的电极。这里,像素电极pe可以是阳极电极,并且公共电极ce可以是阴极电极。在另一实施方式中,像素电极pe可以是阳极电极,并且公共电极ce可以是阴极电极。

106.在一个实施方式中,发光元件ed可以是有机发光二极管(oled)、发光二极管(led)、量子点发光元件等。

107.驱动晶体管drt可以是用于驱动发光元件ed的晶体管,并且可以包括第一节点n1、第二节点n2和第三节点n3等。

108.驱动晶体管drt的第一节点n1可以是驱动晶体管drt的栅极节点,并且可以电连接到扫描晶体管sct的源极节点或漏极节点。驱动晶体管drt的第二节点n2可以是驱动晶体管drt的源极节点或漏极节点。第二节点n2可以连接到发光元件ed的像素电极pe。驱动晶体管drt的第三节点n3可以电连接到用于提供驱动电压evdd的驱动电压线dvl。

109.扫描晶体管sct可以由作为一种选通信号的扫描信号scan控制,并且可以连接在驱动晶体管drt的第一节点n1和数据线dl之间。换句话说,扫描晶体管sct可以根据通过作为一种选通线gl的扫描信号线scl提供的扫描信号scan来导通或截止,并且控制数据线dl与驱动晶体管drt的第一节点n1之间的电连接。

110.扫描晶体管sct可以由具有导通电平电压的扫描信号scan导通,并且将通过数据线dl提供的数据电压vdata传递到驱动晶体管drt的第一节点。

111.在一个实施方式中,当扫描晶体管sct为n型晶体管时,扫描信号scan的导通电平电压可以为高电平电压。在另一实施方式中,当扫描晶体管sct为p型晶体管时,扫描信号scan的导通电平电压可以为低电平电压。

112.储存电容器cst可以连接在驱动晶体管drt的第一节点n1和第二节点n2之间。储存电容器cst可以存储与两个端子之间的电压差相对应的电荷量并且在预定的帧时间内保持两个端子之间的电压差。因此,对应子像素sp可以在预定的帧时间内发光。

113.参照图2b,根据本公开的各方面,设置在显示装置100的显示面板110中的多个子像素sp中的每一个还可以包括感测晶体管sent。

114.感测晶体管sent可以由作为一种选通信号的感测信号sense控制,并且可以连接在驱动晶体管drt的第二节点n2和参考电压线rvl之间。换句话说,感测晶体管sent可以根据通过作为另一种的选通线gl的感测信号线senl提供的感测信号sense而导通或截止,并且控制参考电压线rvl与驱动晶体管drt的第二节点n2之间的电连接。

115.感测晶体管sent可以通过具有导通电平电压的感测信号sense导通,并且将通过参考电压线rvl传输的参考电压vref传递到驱动晶体管drt的第二节点。

116.此外,感测晶体管sent可以通过具有导通电平电压的感测信号sense导通,并且将驱动晶体管drt的第二节点n2处的电压传输到参考电压线rvl。

117.在一个实施方式中,当感测晶体管sent为n型晶体管时,感测信号sense的导通电平电压可以是高电平电压。在另一实施方式中,当感测晶体管sent为p型晶体管时,感测信号sense的导通电平电压可以是低电平电压。

118.当被驱动以感测子像素sp的至少一个特征值时,可以使用感测晶体管sent将驱动晶体管drt的第二节点n2处的电压传输到参考电压线rvl的功能。在这种情况下,传输到参考电压线rvl的电压可以是用于计算子像素sp的至少一个特征值的电压或者其中反映了子像素sp的至少一个特征值的电压。

119.在本文中,子像素sp的至少一个特征值可以是驱动晶体管drt或发光元件ed的特征值。驱动晶体管drt的特征值可以包括驱动晶体管drt的阈值电压和/或迁移率。发光元件ed的特征值可以包括发光元件ed的阈值电压。

120.驱动晶体管drt、扫描晶体管sct和感测晶体管sent可以是n型晶体管、p型晶体管或其组合。在本文中,为了便于描述,假设驱动晶体管drt、扫描晶体管sct和感测晶体管sent为n型晶体管。

121.储存电容器cst可以是有意设计为位于驱动晶体管drt外部的外部电容器,而不是可以形成在驱动晶体管drt的栅极节点和源极节点(或漏极节点)之间的诸如寄生电容器(例如,cgs、cgd)的内部电容器。

122.扫描信号线scl和感测信号线senl可以是不同的选通线gl。在一些实施方式中,扫描信号scan和感测信号sense可以是分开的选通信号,并且一个子像素sp中的扫描晶体管sct的通断定时和感测晶体管sent的通断定时可以是独立的。也就是说,一个子像素sp中的扫描晶体管sct的通断定时和感测晶体管sent的通断定时可以彼此相同或不同。

123.在另一实施方式中,扫描信号线scl和感测信号线senl可以是同一条选通线gl。也

就是说,一个子像素sp中的扫描晶体管sct的栅极节点和感测晶体管sent的栅极节点可以连接到一条选通线gl。在该实施方式中,扫描信号scan和感测信号sense可以是相同的选通信号,并且一个子像素sp中的扫描晶体管sct的通断定时和感测晶体管sent的通断定时可以是相同的。

124.应当理解,图2a和图2b中所示的子像素结构仅仅是便于讨论的可能的子像素结构的示例,并且本公开的实施方式可以根据需要以各种结构中的任何一种来实现。例如,子像素sp还可以包括至少一个晶体管和/或至少一个电容器。

125.此外,尽管已经基于显示装置100是自发光显示装置的假设对图2a和图2b中的子像素结构进行了讨论,但是当显示装置100为液晶显示器时,每个子像素sp可以包括晶体管、像素电极等。

126.图3例示了根据本公开的各方面的显示装置100的示例系统实现。

127.参照图3,显示面板110可以包括其中显示图像的显示区域da和其中不显示图像的非显示区域nda。

128.参照图3,当数据驱动电路120包括一个或更多个源极驱动器集成电路sdic并且以膜上芯片(cof)类型实现时,每个源极驱动器集成电路sdic可以安装在连接到显示面板110的非显示区域nda的电路膜sf上。

129.参照图3,选通驱动电路130可以以面板内栅极(gip)类型来实现。在该实施方式中,选通驱动电路130可以位于显示面板110的非显示区域nda中。在另一实施方式中,与图3中的图示不同,选通驱动电路130可以以膜上芯片(cof)类型来实现。

130.显示装置100可以包括用于一个或更多个源极驱动器集成电路sdic与其它装置、组件等之间的电路连接的至少一个源极印刷电路板spcb,以及其上安装有控制元件和各种类型的电气装置或元件的控制印刷电路板cpcb。

131.其上安装有源极驱动器集成电路sdic的电路膜sf可以连接到至少一个源极印刷电路板spcb。也就是说,其上安装有源极驱动器集成电路sdic的电路膜sf的一侧可以电连接到显示面板110并且其另一侧可以电连接到源极印刷电路板spcb。

132.控制器140和电源管理集成电路pmic 310可以安装在控制印刷电路板cpcb上。控制器140可以执行与显示面板110的驱动以及数据驱动电路120和选通驱动电路130的控制操作相关的整体控制功能。电源管理集成电路310可以向数据驱动电路120和选通驱动电路130提供各种类型的电压或电流,或者控制要提供的各种类型的电压或电流。

133.至少一个源极印刷电路板spcb和控制印刷电路板cpcb之间的电路连接可以通过至少一条连接线缆cbl来执行。连接线缆cbl可以是例如柔性印刷电路fpc、柔性扁平线缆ffc等。

134.至少一个源极印刷电路板spcb和控制印刷电路板cpcb可以集成并实现为一个印刷电路板。

135.根据本公开的各方面的显示装置100还可以包括用于调整电压电平的电平移位器300。在一个实施方式中,电平移位器300可以被设置在控制印刷电路板cpcb或源极印刷电路板spcb上。

136.在根据本公开的各方面的显示装置100中,电平移位器300可以向选通驱动电路130提供选通驱动所需的信号。在一个实施方式中,电平移位器300可以向选通驱动电路130

提供多个时钟信号。因此,选通驱动电路130可以基于从电平移位器300输入的多个时钟信号向多条选通线gl提供多个选通信号。多条选通线gl可以将选通信号承载到设置在基板sub的显示区域da中的子像素sp。

137.图4a例示了根据本公开的各方面的显示装置100的示例选通信号输出系统。

138.参照图4a,电平移位器300可以向选通驱动电路130输出m个时钟信号(clk1至clkm)。选通驱动电路130可以基于m个时钟信号(clk1至clkm)生成m个选通信号(vgate1至vgatem),并将所生成的选通信号(vgate1至vgatem)输出至m条选通线(gl1至glm)。

139.m条选通线(gl1至glm)可以将m个选通信号(vgate1至vgatem)承载到设置在基板sub上的显示区域da中的子像素sp。

140.例如,m条选通线(gl1至glm)可以是如图2a或图2b所示的连接到扫描晶体管sct的栅极节点的扫描信号线scl,并且m个选通信号(vgate1至vgatem)可以是施加到扫描晶体管sct的栅极节点的扫描信号scan。m个选通信号(vgate1至vgatem)中的第一选通信号vgate1可以是施加到包括在设置在第一子像素行中的子像素sp中的每一个中的扫描晶体管sct的相应栅极节点的扫描信号scan。m个选通信号(vgate1至vgatem)中的第二选通信号vgate2可以是施加到包括在设置在与第一子像素行不同的第二子像素行中的子像素sp中的每一个的扫描晶体管sct的相应栅极节点的扫描信号scan。

141.在另一示例中,m条选通线(gl1至glm)可以是如图2b所示的连接到感测晶体管sent的栅极节点的感测信号线senl,并且m个选通信号(vgate1至vgatem)可以是施加到感测晶体管sent的栅极节点的感测信号sense。m个选通信号(vgate1至vgatem)中的第一选通信号vgate1可以是施加到包括在设置在第一子像素行中的子像素sp中的每一个中的感测晶体管sent的相应栅极节点的感测信号sense。m个选通信号(vgate1至vgatem)中的第二选通信号vgate2可以是施加到包括在设置在与第一子像素行不同的第二子像素行中的子像素sp中的每一个中的感测晶体管sent的相应栅极节点的感测信号sense。

142.图4b例示了根据本公开的各方面的显示装置的示例选通驱动电路130。

143.参照图4b,选通驱动电路130可以包括m个输出缓冲器电路(gbuf1至gbufm)和能够控制m个输出缓冲器电路(gbuf1至gbufm)的控制电路400,其中m可以是2或更大的自然数。

144.m个输出缓冲器电路(gbuf1至gbufm)可以接收多个时钟信号中的m个时钟信号(clk1至clkm),并且将多个选通信号中的m个选通信号(vgate1至vgatem)输出到多条选通线gl中的m条选通线(gl1至glm)。

145.m个输出缓冲器电路(gbuf1至gbufm)中的每一个可以包括上拉晶体管tu和下拉晶体管td。

146.在m个输出缓冲器电路(gbuf1至gbufm)中的每一个中,上拉晶体管tu和下拉晶体管td的连接的点可以连接到m条选通线(gl1至glm)中的对应选通线。

147.包括在m个输出缓冲器电路(gbuf1至gbufm)中的相应上拉晶体管tu的栅极节点可以共同连接到控制电路400中的一个q节点q。由此,其中包括在m个输出缓冲器电路(gbuf1至gbufm)中的相应上拉晶体管tu的栅极节点共同连接到一个q节点q的结构被称为q节点共享结构。

148.当选通驱动电路130形成为面板内栅极(gip)类型并且被设计为具有q节点共享结构时,可以减小其中设置有选通驱动电路130的非显示区域nda的尺寸。这里,面板内栅极类

型也称为嵌入类型。

149.在q节点共享结构中,根据一个q节点q的电压,包括在m个输出缓冲器电路(gbuf1至gbufm)中的相应上拉晶体管tu可以同时或几乎同时导通或截止。

150.包括在m个输出缓冲器电路(gbuf1至gbufm)中的相应下拉晶体管td的栅极节点可以共同连接到控制电路400中的一个qb节点qb。由此,包括在m个输出缓冲器电路(gbuf1至gbufm)中的相应下拉晶体管td的栅极节点共同连接到一个qb节点qb的结构被称为qb节点共享结构。

151.在qb节点共享结构中,根据一个qb节点qb的电压,包括在m个输出缓冲器电路(gbuf1至gbufm)中的相应下拉晶体管td可以同时或几乎同时导通或截止。

152.图4c例示了根据本公开的各方面的显示装置100中的时钟信号(clk1至clk4)和q节点处的电压。图4d例示了根据本公开的各方面的显示装置100中的选通信号之间的特性差异。

153.图4c是例示当m为4时第一时钟信号至第四时钟信号(clk1至clk4)和q节点处的电压的示图。

154.m个时钟信号(clk1至clkm)的相应高电平电压持续时间位于时间中的不同的时间,并且m个选通信号(vgate1至vgatem)的相应导通电平电压持续时间(例如,相应高电平电压持续时间)位于不同的时间。然而,为了在信号波形方面解释根据本公开的各方面的显示装置的特性,在图4d中,m个时钟信号(clk1至clkm)的相应高电平电压持续时间在相同的定时被移位并在相同的定时显示,并且m个选通信号(vgate1至vgatem)的相应导通电平电压持续时间(例如,相应高电平电压持续时间)在相同的定时被移位并在相同的定时显示。

155.参照图4c和图4d,电平移位器300可以输出具有相等信号波形的m个时钟信号(clk1至clkm)。选通驱动电路130可以使用具有相等信号波形的m个时钟信号(clk1至clkm)输出m个选通信号(vgate1至vgatem)。也就是说,m个时钟信号(clk1至clkm)的相应上升长度可以相等或在一定范围内不同。m个时钟信号(clk1至clkm)的相应下降长度可以相等或在一定范围内不同。

156.参照图4c,在根据本公开的各方面的显示装置100中,选通驱动电路130可以执行交叠选通驱动(overlap gate driving)。

157.参照图4c,当选通驱动电路130执行交叠选通驱动时,两个时钟信号的相应高电平电压持续时间可以部分交叠。因此,对应于连续驱动定时的两个选通信号的相应导通电平电压持续时间可以部分交叠。

158.例如,参照图4c,第一选通信号vgate1的导通电平电压持续时间和第二选通信号vgate2的导通电平电压持续时间可以部分交叠。第二选通信号vgate2的导通电平电压持续时间和第三选通信号vgate3的导通电平电压持续时间可以部分交叠。

159.m个选通信号(vgate1、vgate2、

……

、vgatem)的导通电平电压持续时间可以是高电平电压持续时间或低电平电压持续时间。

160.例如,参照图4c,m个选通信号(vgate1、vgate2、

……

、vgatem)的导通电平电压持续时间可以具有2h的时间段。两个选通信号的相应导通电平电压持续时间的交叠长度可以为1h的时段。

161.参照图4d,当选通驱动电路130具有q节点共享结构(如图4b)并执行交叠选通驱动

(如图4c)时,m个选通信号(vgate1至vgatem)中的至少一个的信号波形可以与一个或更多个其它选通信号的一个或更多个信号波形不同。这里,信号波形可以包括上升长度和下降长度中的至少一种。

162.参照图4d,m个选通信号(vgate1至vgatem)中的至少一个的下降长度可以与一个或更多个其它选通信号的一个或更多个下降长度不同。m个选通信号(vgate1至vgatem)中的至少一个的上升长度可以与一个或更多个其它选通信号的一个或更多个上升长度不同。

163.参照图4d,从具有q节点共享结构的选通驱动电路130输出的m个选通信号(vgate1、vgate2、

……

、vgatem)可以包括在最早定时具有导通电平电压持续时间的第一选通信号vgate1,以及在最晚定时具有导通电平电压持续时间的第m选通信号vgatem。

164.参照图4d,m个时钟信号(clk1至clkm)可以包括与第一选通信号vgate1相对应的第一时钟信号clk1和与第m选通信号vgatem相对应的第m时钟信号clkm。

165.参照图4d,在第一选通信号vgate1至第m选通信号vgatem中,在最晚定时具有导通电平电压持续时间的第m选通信号vgatem可能具有最差的下降特性。因此,在最晚定时具有导通电平电压持续时间的第m选通信号vgatem的下降长度变为大于在最早定时具有导通电平电压持续时间的第一选通信号vgate1的下降长度。

166.参照图4d,在最早定时具有导通电平电压持续时间的第一选通信号vgate1可能具有最差的上升特性。因此,在最早定时具有导通电平电压持续时间的第一选通信号vgate1的上升长度变为大于在最晚定时具有导通电平电压持续时间的第m选通信号vgatem的上升长度。

167.与第m选通信号vgatem的上升长度相比第一选通信号vgate1的上升长度更大意指选通信号(vgate1和vgatem)之间的上升特性不同,并且与第一选通信号vgate1的下降长度相比第m选通信号vgatem的下降长度更大意指选通信号(vgate1和vgatem)的下降特性不同。

168.选通信号(vgate1至vgatem)之间的特性差异(上升特性差异和下降特性差异)可能导致施加有选通信号(vgate1至vgatem)的晶体管(例如,扫描晶体管sct和/或感测晶体管sent)出现故障,这导致图像质量下降。

169.为了解决这些问题,通过由根据本公开的各方面的显示装置100执行的交叠选通驱动,提供了一种补偿方案,以用于提供通过增加每个子像素中可能充电不充分的充电时间来提高图像质量的效果以及通过q节点共享结构减小显示面板110的边框区域(非显示区域nda)的尺寸的效果两者,并且用于减少可能引起的选通信号之间的特性差异。在下文中,将对此进行详细描述。

170.图4e例示了根据本公开的各方面的对显示装置100中的选通信号之间的特性差异的补偿。

171.参照图4e,根据本公开的各方面的显示装置100可以执行时钟信号控制功能以便补偿参照图4d描述的选通信号之间的特性差异。据此,m个时钟信号(clk1至clkm)中的至少一个的信号波形可以与一个或更多个其它时钟信号的一个或更多个信号波形不同。

172.参照图4e,当执行时钟信号控制功能以补偿显示装置100中的选通信号之间的特性差异时,第一时钟信号clk1的下降长度可以变为大于第m时钟信号clkm的下降长度。

173.继而,相关联的第一选通信号vgate1的下降长度与相关联的第m选通信号vgatem

的下降长度之间的差异可以很小或非常小,或者小于第一时钟信号clk1的下降长度与第m时钟信号clkm的下降长度的差异。

174.当执行时钟信号控制功能以补偿显示装置100中的选通信号之间的特性差异时,第m时钟信号clkm的上升长度可以变为大于第一时钟信号clk1的上升长度。

175.继而,第一选通信号vgate1的上升长度与第m选通信号vgatem的上升长度之间的差异可以很小或非常小,或者小于第一时钟信号clk1的上升长度与第m时钟信号clkm的上升长度的差异。

176.电平移位器300可以根据时钟差异控制信号输出m个时钟信号(clk1至clkm)。

177.电平移位器300可以包括用于分别输出m个时钟信号(clk1至clkm)的m个时钟输出缓冲器,其中m可以是2或更大的自然数。

178.m个时钟信号(clk1至clkm)可以是第一至第m时钟信号(clk1至clkm)。

179.由于交叠选通驱动,第一时钟信号clk1的高电平电压持续时间和第二时钟信号clk2的高电平电压持续时间可以部分交叠。

180.m个时钟信号(clk1至clkm)中的第一时钟信号clk1的信号波形可以与第m时钟信号clkm的信号波形不同。这里,信号波形可以包括下降长度和上升长度,并且第一时钟信号clk1的信号波形的下降长度和上升长度中的至少一个可以与第m时钟信号clkm的信号波形的下降长度和上升长度中的至少一个不同。

181.m个时钟输出缓冲器(cbuf1至cbufm)可以包括用于输出第一时钟信号clk1的第一时钟输出缓冲器cbuf1和用于输出第m时钟信号clkm的第m时钟输出缓冲器cbufm。

182.第一时钟输出缓冲器cbuf1可以包括第一上升控制电路和第一下降控制电路,第一上升控制电路包括电连接在高电平电压节点和第一时钟输出端子之间的n个(n是2或更大的自然数)第一上升控制晶体管,以及包括电连接在低电平电压节点和第一时钟输出端子之间的n个第一下降控制晶体管的第一下降控制电路。

183.第m时钟输出缓冲器cbufm可以包括第m上升控制电路和第m下降控制电路,第m上升控制电路包括电连接在高电平电压节点和第m时钟输出端子之间的n个第m上升控制晶体管,并且第m下降控制电路包括电连接在低电平电压节点与第m时钟输出端子之间的n个第m下降控制晶体管。

184.包括在第一上升控制电路、第一下降控制电路、第m上升控制电路和第m下降控制电路中的至少一个中的n个控制晶体管的相应导通和/或截止可以被独立控制。

185.第一时钟信号clk1的下降长度可以大于第m时钟信号clkm的下降长度。在这种情况下,n个第一下降控制晶体管当中导通的下降控制晶体管的数量可以小于n个第m下降控制晶体管当中导通的下降控制晶体管的数量。

186.第m时钟信号clkm的上升长度可以大于第一时钟信号clk1的上升长度。在这种情况下,n个第m个上升控制晶体管当中导通的上升控制晶体管的数量可以小于n个第一上升控制晶体管当中导通的上升控制晶体管的数量。

187.包括在电平移位器300中的m个时钟输出缓冲器(cbuf1至cbufm)将在后面参照图9进行详细描述,其中作为示例,m为2。

188.在qb节点共享结构中,根据一个qb节点qb处的电压,包括在m个输出缓冲器电路(gbuf1至gbufm)中的相应下拉晶体管td可以同时或几乎同时导通或截止。在选通驱动电路

130中,m是表示q节点q的共享程度的值,并且可以是共享一个q节点q的输出缓冲器电路(gbuf1至gbufm)的数量。

189.例如,m可以是2或4。在下文中,将更详细地描述当m为2时对选通信号之间的特性差异的补偿,并且然后,将更详细地描述其中m为4时对选通信号之间的特性差异的补偿。

190.图5例示了根据本公开的各方面的显示装置100的示例选通信号输出系统。图6a和图6b例示了根据本公开的各方面的显示装置100的示例选通驱动电路130。

191.参照图5、图6a和图6b,当m为2时,两个输出缓冲器电路(gbuf1和gbuf2)共享一个q节点q。

192.当m为2时,m个时钟信号(clk1至clkm)包括第一时钟信号和第二时钟信号(clk1和clk2),并且m个选通信号(vgate1到vgatem)包括第一选通信号和第二选通信号(vgate1和vgate2)。

193.参照图5、图6a和图6b,电平移位器300可以输出多个时钟信号中的两个时钟信号(clk1和clk2)。这里,两个时钟信号(clk1和clk2)可以是第一时钟信号clk1和第二时钟信号clk2。

194.参照图5、图6a和图6b,选通驱动电路130可以接收两个时钟信号(clk1和clk2)并且输出两个选通信号(vgate1和vgate2)。也就是说,选通驱动电路130可以接收第一时钟信号clk1并将第一选通信号vgate1输出到第一选通线gl1,并且接收第二时钟信号clk2并将第二选通信号vgate2输出到第二选通线gl2。

195.参照图6a,选通驱动电路130可以包括第一输出缓冲器电路gbuf1、第二输出缓冲器电路gbuf2、能够控制第一输出缓冲器电路gbuf1和第二输出缓冲器电路gbuf2的控制电路400等。

196.第一输出缓冲器电路gbuf1可以响应于(基于)输入到第一时钟输入端子nc1的第一时钟信号clk1,通过第一选通输出端子ng1将第一选通信号vgate1输出到第一选通线gl1。

197.第二输出缓冲器电路gbuf2可以响应于(基于)输入到第二时钟输入端子nc2的第二时钟信号clk2,通过第二选通输出端子ng2将第二选通信号vgate2输出到第二选通线gl2。

198.控制电路400可以接收起始信号vst和复位信号rst并且控制第一输出缓冲器电路gbuf1和第二输出缓冲器电路gbuf2的操作。

199.第一输出缓冲器电路gbuf1可以包括第一上拉晶体管tu1和第一下拉晶体管td1,第一上拉晶体管tu1电连接在第一时钟输入端子nc1和第一选通输出端子ng1之间,并由q节点q中的电压控制,并且第一下拉晶体管td1电连接在第一选通输出端子ng1和输入有基础电压(base voltage)vss1的基础输入端子ns之间,并由qb节点qb处的电压控制。

200.第二输出缓冲器电路gbuf2可以包括第二上拉晶体管tu2和第二下拉晶体管td2,第二上拉晶体管tu2电连接在第二时钟输入端子nc2和第二选通输出端子ng2之间,并由q节点q中的电压控制,并且第二下拉晶体管td2电连接在第二选通输出端子ng2与基础输入端子ns之间,并由qb节点qb的电压控制。

201.参照图6a,第一输出缓冲器电路gbuf1的第一上拉晶体管tu1的栅极节点和第二输出缓冲器电路gbuf2的第二上拉晶体管tu2的栅极节点电连接到同一q节点q。

202.通过q节点q处的电压,第一输出缓冲器电路gbuf1的第一上拉晶体管tu1和第二输出缓冲器电路gbuf2的第二上拉晶体管tu2可以同时或几乎同时导通或截止。

203.第一输出缓冲器电路gbuf1的第一下拉晶体管td1的栅极节点和第二输出缓冲器电路gbuf2的第二下拉晶体管td2的栅极节点电连接到同一qb节点qb。

204.第一输出缓冲器电路gbuf1的第一下拉晶体管td1和第二输出缓冲器电路gbuf2的第二下拉晶体管td2可以根据共享qb节点qb处的电压同时或几乎同时导通或截止。

205.在图6b的例示中,当与图6a的例示相比较时,第一输出缓冲器电路gbuf1可以包括第一附加下拉晶体管td1a,并且第二输出缓冲器电路gbuf2可以包括第二附加下拉晶体管td2a。

206.第一附加下拉晶体管td1a可以电连接在第一选通输出端子ng1和基础输入端子ns之间,并且由与qb节点qb不同的另一qb节点qba处的电压控制。

207.第二附加下拉晶体管td2a可以电连接在第二选通输出端子ng2和基础输入端子ns之间,并且由另一qb节点qba处的电压控制。

208.第一附加下拉晶体管td1a和第一下拉晶体管td1可以彼此独立地控制。第二附加下拉晶体管td2a和第二下拉晶体管td2可以彼此独立地控制。

209.第一附加下拉晶体管td1a和第一下拉晶体管td1可以交替操作。第二附加下拉晶体管td2a和第二下拉晶体管td2可以交替操作。

210.例如,第一下拉晶体管td1的栅极节点和第二下拉晶体管td2的栅极节点共同连接到的qb节点qb可以是具有能够在奇数编号定时中导通第一下拉晶体管td1和第二下拉晶体管td2的导通电平电压的奇数编号qb节点qb_o。

211.例如,第一附加下拉晶体管td1a的栅极节点和第二附加下拉晶体管td2a的栅极节点共同连接到的qb节点qba可以是具有能够在偶数编号定时中导通第一附加下拉晶体管td1a和第二附加下拉晶体管td2a的导通电平电压的偶数编号qb节点qb_e。

212.图7例示了根据本公开的各方面的显示装置100中的选通信号之间的特性差异。

213.参照图7,电平移位器300可以向选通驱动电路130输出第一时钟信号clk1和第二时钟信号clk2。选通驱动电路130可以接收第一时钟信号clk1并将相关联的第一选通信号vgate1输出到第一选通线gl1,并且接收第二时钟信号clk2并将相关联的第二选通信号vgate2输出到第二选通线gl2。

214.图7所示的第一选通信号vgate1呈现其导通电平电压持续时间,并且图7所示的第二选通信号vgate2呈现其导通电平电压持续时间。

215.参照图7,第一时钟信号clk1和第二时钟信号clk2可以具有相同的信号波形。也就是说,第一时钟信号clk1的上升长度cr1和第二时钟信号clk2的上升长度cr2可以相等或近似相等,或者在一定范围内不同。第一时钟信号clk1的下架长度cf1和第二时钟信号clk2的下降长度cr2可以相等或近似相等,或者在一定范围内不同。

216.在从具有q节点共享结构的选通驱动电路130输出的两个(m=2)选通信号(vgate1和vgate2)中,其中m表示共享程度为2,第一选通信号vgate1在最早定时具有导通电平电压持续时间,并且第二选通信号vgate2在最晚定时具有导通电平电压持续时间。

217.根据上述交叠选通驱动,第一选通信号vgate1的导通电平电压持续时间和第二选通信号vgate2的导通电平电压持续时间可以部分交叠。例如,第一选通信号vgate1的导通

电平电压持续时间和第二选通信号vgate2的导通电平电压持续时间中的每一个可以是2个水平时间(h)的时段,并且第一选通信号vgate1的导通电平电压持续时间的后一半(1h)可以与第二选通信号vgate2的导通电平电压持续时间的前一半(1h)交叠。

218.当选通驱动电路130执行交叠选通驱动并具有q节点共享结构时(如图6a和图6b中所示),如果第一时钟信号clk1和第二时钟信号clk2根据传统方案具有相等的信号波形,则第一选通信号vgate1的信号波形可能变为与第二选通信号vgate2的信号波形不同。

219.第一选通信号vgate1和第二选通信号vgate2之间生成不同的信号波形指示第一选通信号vgate1和第二选通信号vgate2之间存在特性差异。

220.第一选通信号vgate1和第二选通信号vgate2之间的特性差异的出现可以意指存在第一选通信号vgate1和第二选通信号vgate2之间的上升特性差异,或者第一选通信号vgate1和第二选通信号vgate2之间的下降特性差异。

221.当选通驱动电路130执行交叠选通驱动并且具有q节点共享结构时(如图6a和图6b所示),如果根据传统方案第一时钟信号clk1和第二时钟信号clk2具有相等的信号波形,则第一选通信号vgate1的上升长度r1可以变为大于第二选通信号vgate2的上升长度r2,并且第二选通信号vgate2的下降长度f2可以变为大于第一选通信号vgate1的下降长度f1。

222.选通信号(vgate1和vgate2)之间的特性差异(上升特性差异和下降特性差异)可能会导致施加有选通信号(vgate1和vgate2)的晶体管(例如,扫描晶体管sct和/或感测晶体管sent)发生故障,这会导致图像质量下降。

223.为了解决这些问题,可以向根据本公开的各方面的显示装置100提供补偿选通信号之间的特性差异的功能,并且在下文中,在一些实施方式中,将结合附图详细描述用于补偿显示装置100中选通信号之间的特性差异的功能。

224.图8a至图8c例示了根据本公开的各方面的在显示装置100中补偿选通信号之间的特性差异的功能。

225.参照图8a至图8c,为了补偿选通信号之间的特性差异,电平移位器300可以控制第一时钟信号和第二时钟信号(clk1和clk2)中的一个或更多个的上升特性和下降特性中的一个或更多个,从而生成并输出更新后的第一时钟信号clk1和更新后的第二时钟信号clk2。

226.继而,第一时钟信号clk1的下降长度cf1和第二时钟信号clk2的下降长度cf2可以不同,或者第一时钟信号clk1的上升长度cr1和第二时钟信号clk2的上升长度cr2可以不同。

227.参照图8a,电平移位器300可以通过下降控制使第一时钟信号clk1的第一下降长度cf1变为大于第二时钟信号clk2的第二下降长度cf2。尽管图8a示出第一选通信号vgate1和第二选通信号vgate2的上升时间相等,但这只是为了便于描述,并且在实际实现中,第一选通信号vgate1在比第二选通信号vgate2更早的定时从低电平电压上升到高电平电压,并从高电平电压下降到低电平电压。在这种情况下,通过电平移位器300的下降控制,作为用于生成第一选通信号vgate1的基础的第一时钟信号clk1的下降长度cf1可以变为大于作为用于生成第二选通信号vgate2的基础的第二时钟信号clk2的下降长度cf2。换句话说,当第一选通信号vgate1是施加到以比第二选通信号vgate2更早的定时扫描的选通线的选通信号时,为了解决q节点共享结构下第二选通信号vgate2的下降长度f2相对更大并且第一选

通信号vgate1的下降长度f1相对更小的情况(下降特性的差异),电平移位器300可以有意延长作为用于生成第一选通信号vgate1的基础的第一时钟信号clk1的下降长度cf1,从而导致第一选通信号vgate1的更新后的下降长度f1被有意延长。因此,第一选通信号vgate1的延长的下降长度f1可以等于或几乎等于第二选通信号vgate2的原始下降长度f2。

228.通过电平移位器300的下降控制,第一选通信号vgate1的下降长度f1和第二选通信号vgate2的下降长度f2相等或近似相等,或者在预定范围内相似。

229.通过电平移位器300的下降控制,第一选通信号vgate1的下降长度f1与第二选通信号vgate2的下降长度f2之间的差异与不进行下降控制的情况(如图7)相比可以减小。

230.通过电平移位器300的下降控制,第一选通信号vgate1的下降长度f1与第二选通信号vgate2的下降长度f2的差异可以变为小于第一时钟信号clk1的下降长度cf1与第二时钟信号clk2的下降长度cf2之间的差异。

231.结果,可以补偿第一选通信号和第二选通信号(vgate1和vgate2)之间的下降特性的差异,从而能够提高图像质量。

232.参照图8b,电平移位器300可以通过上升控制使第二时钟信号clk2的第二上升长度cr2变为大于第一时钟信号clk1的第一上升长度cr1。

233.因此,当第一选通信号vgate1是比第二时钟信号vgate2在更早的时间从低电平电压上升到高电平电压并从高电平电压下降到低电平电压的选通信号时,第二时钟信号clk2的更新后的上升长度cr2可以变为大于第一时钟信号clk1的上升长度cr1。换句话说,当第一选通信号vgate1是施加到以比第二选通信号vgate2的更早的定时扫描的选通线的选通信号时,为了解决q节点共享结构下第一选通信号vgate1的上升长度r1相对更大并且第二选通信号vgate2的上升长度r2相对更小的情况(上升特性的差异),电平移位器300可以有意延长用作用于生成第二选通信号vgate2的基础的第二时钟信号clk2的上升长度cr2,从而导致第二选通信号vgate2的更新后的上升长度r2被有意延长。因此,第二选通信号vgate2的延长的上升长度r2可以等于或几乎等于第一选通信号vgate1的原始上升长度r1。

234.通过电平移位器300的上升控制,第一选通信号vgate1的上升长度r1和第二选通信号vgate2的上升长度r2可以相等或近似相等,或者在预定范围内相似。

235.通过电平移位器300的上升控制,第一选通信号vgate1的上升长度r1与第二选通信号vgate2的上升长度r2之间的差异与不进行上升控制的情况(如图7)相比可以减小。

236.通过电平移位器300的上升控制,第一选通信号vgate1的上升长度r1和第二选通信号vgate2的上升长度r2之间的差可以变为小于第二时钟信号clk2的上升长度cr2和第一时钟信号clk1的上升长度cr1之间的差。

237.结果,可以补偿第一选通信号和第二选通信号(vgate1和vgate2)之间的上升特性的差异,从而能够提高图像质量。

238.参照图8c,电平移位器300可以通过下降控制使第一时钟信号clk1的第一下降长度cf1变为大于第二时钟信号clk2的第二下降长度cf2,并且通过上升控制使第二时钟信号clk2的第二上升长度cr2大于第一时钟信号clk1的第一上升长度cr1。

239.通过电平移位器300的上升控制和下降控制,第一时钟信号clk1的下降长度cf1可以变为大于第二时钟信号clk2的下降长度cf2,并且第二时钟信号clk2的上升长度cr2可以变为大于第一时钟信号clk1的上升长度cr1。

240.通过电平移位器300的下降控制和上升控制,第一选通信号vgate1的下降长度f1和第二选通信号vgate2的下降长度f2可以变为相等或近似相等,或在预定范围内相似,并且第一选通信号vgate1的上升长度r1和第二选通信号vgate2的上升长度r2可以变为相等或近似相等,或在预定范围内相似。

241.通过电平移位器300的下降控制和上升控制,第一选通信号vgate1的下降长度f1与第二选通信号vgate2的下降长度f2之间的差异与不进行下降控制的情况(如图7)相比可以减小,并且第一选通信号vgate1的上升长度r1与第二选通信号vgate2的上升长度r2之间的差异与不进行上升控制的情况(如图7)相比可以减小。

242.通过电平移位器300的下降控制和上升控制,第一选通信号vgate1的下降长度f1和第二选通信号vgate2的下降长度f2之间的差异可以变为小于第一时钟信号clk1的下降长度cf1和第二时钟信号clk2的下降长度cf2之间的差异,并且第一选通信号vgate1的上升长度r1和第二选通信号vgate2的上升长度r2之间的差异可以变为小于第二时钟信号clk2的上升长度cr2和第一时钟信号clk1的上升长度cr1之间的差异。

243.结果,可以补偿第一选通信号和第二选通信号(vgate1和vgate2)之间的上升特性差异和下降特性差异两者,从而能够显着提高图像质量。

244.图9是根据本公开的各方面的显示装置100的电平移位器300的框图。

245.如上所述,电平移位器300可以包括m个时钟输出缓冲器(cbuf1、cbuf2、

……

)。然而,为了描述方便,在图9中,作为示例,将讨论能够生成和输出两个时钟信号(clk1和clk2)的两个时钟输出缓冲器(cbuf1和cbuf2),其中m是2或更大的自然数。

246.参照图9,电平移位器300可以包括用于生成第一时钟信号clk1并将所生成的第一时钟信号clk1输出到第一时钟输出端子nclk1的第一时钟输出缓冲器cbuf1,以及用于生成第二时钟信号clk2并将所生成的第二时钟信号clk2输出到第二时钟输出端子nclk2的第二时钟输出缓冲器cbuf2。

247.第一时钟输出缓冲器cbuf1可以包括第一上升控制电路rcc1和第一下降控制电路fcc1,并且可以通过响应时钟差异控制信号cdcs[1:n]来控制第一上升控制电路rcc1和第一下降控制电路fcc1而控制第一时钟信号clk1的上升特性和下降特性中的至少一个。

[0248]

第二时钟输出缓冲器cbuf2可以包括第二上升控制电路rcc2和第二下降控制电路fcc2,并且可以通过响应时钟差异控制信号cdcs[1:n]来控制第二上升控制电路rcc2和第二下降控制电路fcc2而控制第二时钟信号clk2的上升特性和下降特性中的至少一个。

[0249]

这里,时钟差异控制信号cdcs[1:n]可以由电源管理集成电路310或控制器140提供给电平移位器300。

[0250]

图10a至图10d是根据本公开的各方面的显示装置100的电平移位器300的第一时钟输出缓冲器cbuf1中的示例电路,并且图11a至图11d是根据本公开的各方面的显示装置100的电平移位器300的第二时钟输出缓冲器cbuf2中的示例电路。

[0251]

参照图10a至图10d,第一时钟输出缓冲器cbuf1可以包括第一上升控制电路rcc1和第一下降控制电路fcc1,第一上升控制电路rcc1包括电连接在施加有高电平电压hv的高电平电压节点nhv和第一时钟输出端子nclk1之间的n个第一上升控制晶体管(rct1-1至rct1-n),并且第一下降控制电路fcc1包括电连接在施加有低电平电压lv的低电平电压节点nlv与第一时钟输出端子nclk1之间的n个第一下降控制晶体管(fct1-1至fct1-n),其中n

为2或更大的自然数。

[0252]

参照图11a至图11d,第二时钟输出缓冲器cbuf2可以包括第二上升控制电路rcc2和第二下降控制电路fcc2,第二上升控制电路rcc2包括电连接在施加有高电平电压hv的高电平电压节点nhv和第二时钟输出端子nclk2之间的n个第二上升控制晶体管(rct2-1至rct2-n),并且第二下降控制电路fcc2包括电连接在施加有低电平电压lv的低电平电压节点nlv和第二时钟输出端子nclk2之间的n个第二下降控制晶体管(fct2-1至fct2-n)。

[0253]

这里,高电平电压hv可以与时钟信号(clk1和clk2)的高电平电压相对应并且与选通信号(vgate1和vgate2)的高电平电压(导通电平电压)相对应。低电平电压lv可以与时钟信号(clk1和clk2)的低电平电压相对应并且与选通信号(vgate1和vgate2)的低电平电压(截止电平电压)相对应。

[0254]

参照图10a至图11d,包括在第一上升控制电路rcc1、第一下降控制电路fcc1、第二上升控制电路rcc2和第二下降控制电路fcc2中的至少一个中的n个控制晶体管的相应导通或/和截止可以独立控制。

[0255]

可以将截止电平选通电压施加到包括在第一上升控制电路rcc1、第一下降控制电路fcc1、第二上升控制电路rcc2和第二下降控制电路fcc2中的至少一个中的n个控制晶体管的相应栅极节点中的一个或更多个。包括在第一上升控制电路rcc1、第一下降控制电路fcc1、第二上升控制电路rcc2和第二下降控制电路fcc2中的至少一个中的n个控制晶体管中的一个或更多个可以被截止。

[0256]

参照图10a至图11d,响应于从电源管理集成电路310或控制器140输入的时钟偏差控制信号cdcs[1:n],在电平移位器300中,包括在第一上升控制电路rcc1、第一下降控制电路fcc1、第二上升控制电路rcc2和第二下降控制电路fcc2中的至少一个中的n个控制晶体管中的一个或更多个可以导通,除了导通的控制晶体管之外的剩余控制晶体管中的全部或一些可以截止。

[0257]

参照图10a,在第一时钟输出缓冲器cbuf1中,n个第一上升控制晶体管(rct1-1至rct1-n)的全部相应栅极节点可以电连接并且共同接收一个第一上升控制信号rcs1,并且n个第一下降控制晶体管(fct1-1至fct1-n)的全部相应栅极节点可以电连接并且共同接收一个第一下降控制信号fcs1。在这种情况下,n个第一上升控制晶体管(rct1-1至rct1-n)可以同时或基本同时导通或截止,并且n个第一下降控制晶体管(fct1-1至fct1-n)可以同时或基本同时导通或截止。

[0258]

参照图10b,在第一时钟输出缓冲器cbuf1中,n个第一上升控制晶体管(rct1-1至rct1-n)的全部相应栅极节点均可以电连接并且共同接收一个第一上升控制信号rcs1,并且n个第一下降控制信号fcs1[1:n]可以单独施加到n个第一下降控制晶体管(fct1-1至fct1-n)的栅极节点。在这种情况下,n个第一上升控制晶体管(rct1-1至rct1-n)可以同时或基本同时导通或截止,并且n个第一下降控制晶体管(fct1-1至fct1-n)可以独立导通和截止。

[0259]

参照图10c,在第一时钟输出缓冲器cbuf1中,n个第一上升控制信号rcs1[1:n]可以单独施加到n个第一上升控制晶体管(rct1-1至rct1-n)的栅极节点,并且n个第一下降控制晶体管(fct1-1至fct1-n)的全部相应栅极节点可以电连接并且共同接收一个第一下降控制信号fcs1。在这种情况下,n个第一上升控制晶体管(rct1-1至rct1-n)可以独立导通和

截止,并且n个第一下降控制晶体管(fct1-1至fct1-n)可以同时或基本同时导通或截止。

[0260]

参照图10d,在第一时钟输出缓冲器cbuf1中,n个第一上升控制信号rcs1[1:n]可以单独施加到n个第一上升控制晶体管(rct1-1至rct1-n)的栅极节点,并且n个第一下降控制信号fcs1[1:n]可以单独施加到n个第一下降控制晶体管(fct1-1至fct1-n)的栅极节点。在这种情况下,n个第一上升控制晶体管(rct1-1至rct1-n)可以独立导通和截止,并且n个第一下降控制晶体管(fct1-1至fct1-n)可以独立导通和截止。

[0261]

参照图11a,在第二时钟输出缓冲器cbuf2中,n个第二上升控制晶体管(rct2-1至rct2-n)的全部相应栅极节点可以电连接并且共同接收一个第二上升控制信号rcs2,并且n个第二下降控制晶体管(fct2-1至fct2-n)的全部相应栅极节点可以电连接并且共同接收一个第二下降控制信号fcs2。在这种情况下,n个第二上升控制晶体管(rct2-1至rct2-n)可以同时或基本同时导通或截止,并且n个第二下降控制晶体管(fct2-1至fct2-n)可以同时或基本同时导通或截止。

[0262]

参照图11b,在第二时钟输出缓冲器cbuf2中,n个第二上升控制晶体管(rct2-1至rct2-n)的全部相应栅极节点可以电连接并且共同接收一个第二上升控制信号rcs2,并且n个第二下降控制信号fcs2[1:n]可以单独施加到n个第二下降控制晶体管(fct2-1至fct2-n)的栅极节点。在这种情况下,n个第二上升控制晶体管(rct2-1至rct2-n)可以同时或基本同时导通或截止,并且n个第二下降控制晶体管(fct2-1至fct2-n)可以独立导通和截止。

[0263]

参照图11c,在第二时钟输出缓冲器cbuf2中,n个第二上升控制信号rcs2[1:n]可以单独施加到n个第二上升控制晶体管(rct2-1至rct2-n)的栅极节点,并且n个第二下降控制晶体管(fct2-1至fct2-n)的全部相应栅极节点可以电连接并且共同接收一个第二下降控制信号fcs2。在这种情况下,n个第二上升控制晶体管(rct2-1至rct2-n)可以独立导通和截止,并且n个第二下降控制晶体管(fct2-1至fct2-n)可以同时或基本同时导通或截止。

[0264]

参照图11d,在第二时钟输出缓冲器cbuf2中,n个第二上升控制信号rcs2[1:n]可以单独施加到n个第二上升控制晶体管(rct2-1至rct2-n)的栅极节点,并且n个第二下降控制信号fcs2[1:n]可以单独施加到n个第二下降控制晶体管(fct2-1至fct2-n)的栅极节点。在这种情况下,n个第二上升控制晶体管(rct2-1至rct2-n)可以独立导通和截止,并且n个第二下降控制晶体管(fct2-1至fct2-n)可以独立导通和截止。

[0265]

在一些实施方式中,可以通过选择性地组合图10a至图10d所示的四种类型的第一时钟输出缓冲器cbuf1中的一种和图11a至图11d中所示的四种类型的第二时钟输出缓冲器cbuf2中的一种来配置一个电平移位器300。

[0266]

在下文中,将参照图12描述由图10b的第一时钟输出缓冲器cbuf1和图11a的第二时钟输出缓冲器cbuf2的组合配置的电平移位器300,并且将参照图14描述由图10b的第一时钟输出缓冲器cbuf1和图11c的第二时钟输出缓冲器cbuf2的组合配置的电平移位器300。

[0267]

图12是根据本公开的各方面的用于补偿显示装置100中的选通信号之间的下降特性差异的电平移位器300的详细示图。图13例示了根据图12的电平移位器300的n个第一下降控制晶体管(fct1-1至fct1-n)当中的导通的第一下降控制晶体管的数量的第一时钟信号clk1的下降长度cf1。

[0268]

参照图12,在选通信号之间的下降特性的差异是图像质量劣化等的主要因素的情况下,电平移位器300可以执行补偿选通信号之间的下降特性差异的控制功能,而不是执行

补偿选通信号之间的上升特性差异的控制功能。

[0269]

参照图12,电平移位器300可以由图10b的第一时钟输出缓冲器cbuf1和图11a的第二时钟输出缓冲器cbuf2的组合配置。

[0270]

参照图12,包括在电平移位器300中的第一时钟输出缓冲器cbuf1可以执行第一时钟信号clk1的下降控制并且可以不执行第一时钟信号clk1的上升控制。在包括在电平移位器300中的第一时钟输出缓冲器cbuf1中,包括在第一下降控制电路fcc1中的n个第一下降控制晶体管(fct1-1至fct1-n)可以被控制为独立地导通或截止,并且包括在第一上升控制电路rcc1中的n个第一上升控制晶体管(rct1-1至rct1-n)可以同时或几乎同时导通或截止。

[0271]

参照图12,包括在电平移位器300中的第二时钟输出缓冲器cbuf2可以不执行第二时钟信号clk2的下降和上升控制。在包括在电平移位器300中的第二时钟输出缓冲器cbuf2中,包括在第二上升控制电路rcc2中的n个第二上升控制晶体管(rct2-1至rct2-n)可以同时或几乎同时导通或截止,并且包括在第二下降控制电路fcc2中的n个第二下降控制晶体管(fct2-1至fct2-n)可以同时或几乎同时导通或截止。

[0272]

参照图12,n个第一下降控制晶体管(fct1-1至fct1-n)当中的一个至(n-1)个第一下降控制晶体管可以通过n个第一下降控制信号fcs1[1:n]导通,并且全部n个第二下降控制晶体管(fct2-1至fct2-n)都可以通过一个第二下降控制信号fcs2导通。

[0273]

从第一时钟输出缓冲器cbuf1输出的第一时钟信号clk1的下降长度cf1可以大于从第二时钟输出缓冲器cbuf2输出的第二时钟信号clk2的下降长度cf2。

[0274]

相关联的第一选通信号vgate1的下降长度f1与相关联的第二选通信号vgate2的下降长度f2之间的差异可以小于第一时钟信号clk1的下降长度cf1和第二时钟信号clk2的下降长度cf2之间的差异。

[0275]

参照图12,当第一时钟信号clk1的下降长度cf1大于第二时钟信号clk2的下降长度cf2时,n个第一下降控制晶体管(fct1-1至fct1-n)当中导通的下降控制晶体管的数量可以小于n个第二下降控制晶体管(fct2-1至fct2-n)当中导通的下降控制晶体管的数量。

[0276]

参照图12和图13,在包括在电平移位器300中的第一时钟输出缓冲器cbuf1中,当包括在第一下降控制电路fcc1中的n个第一下降控制晶体管(fct1-1至fct1-n)全部导通时,第一时钟信号clk1在最早定时处下降。因此,第一时钟信号clk1的下降长度cf1可以变为最小。参照图13,当包括在第一下降控制电路fcc1中的n个第一下降控制晶体管(fct1-1至fct1-n)全部导通时,第一时钟信号clk1的电压可以几乎没有时间延迟地从高电平电压下降到低电平电压。也就是说,当包括在第一下降控制电路fcc1中的n个第一下降控制晶体管(fct1-1至fct1-n)全部导通时,第一时钟信号clk1的下降长度cf1可以变为接近于0(零)。

[0277]

参照图12和图13,在包括在电平移位器300中的第一时钟输出缓冲器cbuf1中,当包括在第一下降控制电路fcc1中的n个第一下降控制晶体管(fct1-1至fct1-n)中的一个导通时,第一时钟信号clk1在最晚定时处下降。因此,第一时钟信号clk1的下降长度cf1可以变为最大。

[0278]

图14是根据本公开的各方面的用于补偿显示装置100中的选通信号之间的下降特性差异和上升特性差异的电平移位器300的详细示图。图15例示了根据图14的电平移位器

300的n个第一下降控制晶体管(fct1-1至fct1-n)当中导通的第一下降控制晶体管的数量的第一时钟信号clk1的下降长度cf1和根据其n个第二上升控制晶体管(rct2-1至rct2-n)当中导通的第二上升控制晶体管的数量的第二时钟信号clk2的上升长度cr2。

[0279]

参照图14,当选通信号之间的下降特性的差异和上升特性的差异二者都是图像质量劣化等的主要因素时,电平移位器300可以执行补偿选通信号之间的下降特性差异和上升特性差异二者的控制功能。

[0280]

参照图14,电平移位器300可以由图10b的第一时钟输出缓冲器cbuf1和图11c的第二时钟输出缓冲器cbuf2的组合配置。

[0281]

参照图14,包括在电平移位器300中的第一时钟输出缓冲器cbuf1可以执行第一时钟信号clk1的下降控制并且可以不执行第一时钟信号clk1的上升控制。在包括在电平移位器300中的第一时钟输出缓冲器cbuf1中,包括在第一下降控制电路fcc1中的n个第一下降控制晶体管(fct1-1至fct1-n)可以被控制为独立导通或截止,并且包括在第一上升控制电路rcc1中的n个第一上升控制晶体管(rct1-1至rct1-n)可以同时或几乎同时导通或截止。

[0282]

参照图14,包括在电平移位器300中的第二时钟输出缓冲器cbuf2可以不执行第二时钟信号clk2的下降控制并且可以执行第二时钟信号clk2的上升控制。在包括在电平移位器300中的第二时钟输出缓冲器cbuf2中,包括在第二上升控制电路rcc2中的n个第二上升控制晶体管(rct2-1至rct2-n)可以被控制为独立导通或截止,并且包括在第二下降控制电路fcc2中的n个第二下降控制晶体管(fct2-1至fct2-n)可以同时或几乎同时导通或截止。

[0283]

参照图14,n个第一下降控制晶体管(fct1-1至fct1-n)当中的一个至(n-1)个第一下降控制晶体管可以通过n个第一下降控制信号fcs1[1:n]导通。全部n个第二下降控制晶体管(fct2-1至fct2-n)都可以通过一个第二下降控制信号fcs2导通。

[0284]

从第一时钟输出缓冲器cbuf1输出的第一时钟信号clk1的下降长度cf1可以大于从第二时钟输出缓冲器cbuf2输出的第二时钟信号clk2的下降长度cf2。

[0285]

相关联的第一选通信号vgate1的下降长度f1与相关联的第二选通信号vgate2的下降长度f2之间的差异可以小于第一时钟信号clk1的下降长度cf1和第二时钟信号clk2的下降长度cf2之间的差异。

[0286]

参照图14,当第一时钟信号clk1的下降长度cf1大于第二时钟信号clk2的下降长度cf2时,n个第一下降控制晶体管(fct1-1至fct1-n)当中导通的下降控制晶体管的数量可以小于n个第二下降控制晶体管(fct2-1至fct2-n)当中导通的下降控制晶体管的数量。

[0287]

参照图14,n个第二上升控制晶体管(rct2-1至rct2-n)当中的一个至(n-1)个第二控制晶体管可以通过n个第二上升控制信号rcs2[1:n]导通。全部n个第一上升控制晶体管(rct1-1至rct1-n)都可以通过一个第一上升控制信号rcs1导通。

[0288]

从第二时钟输出缓冲器cbuf2输出的第二时钟信号clk2的上升长度cr2可以大于从第一时钟输出缓冲器cbuf1输出的第一时钟信号clk1的上升长度cr1。

[0289]

相关联的第一选通信号vgate1的上升长度r1与相关联的第二选通信号vgate2的上升长度r2之间的差异可以小于第一时钟信号clk1的上升长度cr1和第二时钟信号clk2的上升长度cr2之间的差异。

[0290]

参照图14,当第二时钟信号clk2的上升长度cr2大于第一时钟信号clk1的上升长度cr1时,n个第二上升控制晶体管(rct2-1至rct2-n)当中导通的上升控制晶体管的数量可

以小于n个第一上升控制晶体管(rct1-1至rct1-n)当中导通的上升控制晶体管的数量。

[0291]

参照图14和图15,在包括在电平移位器300中的第一时钟输出缓冲器cbuf1中,当包括在第一下降控制电路fcc1中的全部n个第一下降控制晶体管(fct1-1至fct1-n)都导通时,第一时钟信号clk1在最早定时处下降。因此,第一时钟信号clk1的下降长度cf1可以变为最小。参照图15,当包括在第一下降控制电路fcc1中的全部n个第一下降控制晶体管(fct1-1至fct1-n)都导通时,第一时钟信号clk1的电压可以几乎没有时间延迟地从高电平电压下降到低电平电压。也就是说,当包括在第一下降控制电路fcc1中的全部n个第一下降控制晶体管(fct1-1至fct1-n)都导通时,第一时钟信号clk1的下降长度cf1可以变为接近0(零)。

[0292]

参照图14和图15,在包括在电平移位器300中的第一时钟输出缓冲器cbuf1中,当包括在第一下降控制电路fcc1中的n个第一下降控制晶体管(fct1-1至fct1-n)中的一个导通时,第一时钟信号clk1在最晚定时处下降。因此,第一时钟信号clk1的下降长度cf1可以变为最大。

[0293]

参照图14和图15,在包括在电平移位器300中的第二时钟输出缓冲器cbuf2中,当包括在第二上升控制电路rcc2中的全部n个第二上升控制晶体管(rct2-1至rct 2-n)都导通时,第二时钟信号clk2在最早定时处上升。因此,第二时钟信号clk2的上升长度cr2可以变为最小。参照图15,当包括在第二上升控制电路rcc2中的全部n个第二上升控制晶体管(rct2-1至rct2-n)都导通时,第二时钟信号clk2的电压可以几乎没有时间延迟地从低电平电压上升到高电平电压。也就是说,当包括在第二上升控制电路rcc2中的全部n个第二上升控制晶体管(rct2-1至rct2-n)都导通时,第二时钟信号clk2的上升长度cr2可以变为接近0(零)。

[0294]

参照图14和图15,在包括在电平移位器300中的第二时钟输出缓冲器cbuf2中,当包括在第二上升控制电路rcc2中的n个第二上升控制晶体管(rct2-1至rct2-n)中的一个导通时,第二时钟信号clk2在最晚定时处上升。因此,第二时钟信号clk2的上升长度cf2可以变为最大。

[0295]

图16例示了根据本公开的各方面的显示装置100的示例选通信号输出系统。图17例示了图16的选通信号输出系统中的示例选通驱动电路130。

[0296]

参照图16,当m为4时,四个输出缓冲器电路(gbuf1至gbuf4)可以共享一个q节点q。

[0297]

当m为4时,四个时钟信号(clk1至clk4)可以是第一时钟信号clk1、第二时钟信号clk2、第三时钟信号clk3和第四时钟信号clk4,并且相关联的四个选通信号(vgate1至vgate4)可以是第一选通信号vgate1、第二选通信号vgate2、第三选通信号vgate3和第四选通信号vgate4。

[0298]

参照图16,电平移位器300可以输出多个时钟信号中的四个时钟信号(clk1至clk4)。这里,四个时钟信号(clk1至clk4)可以是第一时钟信号clk1、第二时钟信号clk2、第三时钟信号clk3和第四时钟信号clk4。

[0299]

参照图16,选通驱动电路130可以接收四个时钟信号(clk1至clk4)并输出四个选通信号(vgate1至vgate4)。也就是说,选通驱动电路130可以接收第一时钟信号clk1并将第一选通信号vgate1输出到第一选通线gl1,接收第二时钟信号clk2并将第二选通信号vgate2输出到第二选通线gl2,接收第三时钟信号clk3并将第三选通信号vgate3输出到第

三选通线gl3,并且接收第四时钟信号clk4并将第四选通信号vgate4输出到第四选通线gl4。

[0300]

参照图17,选通驱动电路130可以包括第一至第四输出缓冲器电路(gbuf1至gbuf4)和用于控制第一至第四输出缓冲器电路(gbuf1至gbuf4)的控制电路400。

[0301]

第一输出缓冲器电路gbuf1可以响应于(基于)输入到第一时钟输入端子nc1的第一时钟信号clk1,通过第一选通输出端子ng1将第一选通信号vgate1输出到第一选通线gl1。

[0302]

第一输出缓冲器电路gbuf1可以包括电连接在第一时钟输入端子nc1和第一选通输出端子ng1之间并且由q节点q中的电压控制的第一上拉晶体管tu1,以及电连接在第一选通输出端子ng1与输入有基础电压vss1的基础输入端子ns之间并且由qb节点qb的电压控制的第一下拉晶体管td1。

[0303]

第二输出缓冲器电路gbuf2可以响应于(基于)输入到第二时钟输入端子nc2的第二时钟信号clk2,通过第二选通输出端子ng2将第二选通信号vgate2输出到第二选通线gl2。

[0304]

第二输出缓冲器电路gbuf2可以包括电连接在第二时钟输入端子nc2和第二选通输出端子ng2之间并且由q节点q中的电压控制的第二上拉晶体管tu2,以及电连接在第二选通输出端子ng2与基础输入端子ns之间并且由qb节点qb的电压控制的第二下拉晶体管td2。

[0305]

第三输出缓冲器电路gbuf3可以响应于(基于)输入到第三时钟输入端子nc3的第三时钟信号clk3,通过第三选通输出端子ng3将第三选通信号vgate3输出到第三选通线gl3。

[0306]

第三输出缓冲器电路gbuf3可以包括电连接在第三时钟输入端子nc3和第三选通输出端子ng3之间并且由q节点q中的电压控制的第三上拉晶体管tu3,以及电连接在第三选通输出端子ng3与基础输入端子ns之间并且由qb节点qb的电压控制的第三下拉晶体管td3。

[0307]

第四输出缓冲器电路gbuf4可以响应于(基于)输入到第四时钟输入端子nc4的第四时钟信号clk4,通过第四选通输出端子ng4将第四选通信号vgate4输出到第四选通线gl4。

[0308]

第四输出缓冲器电路gbuf4可以包括电连接在第四时钟输入端子nc4和第四选通输出端子ng4之间并且由q节点q中的电压控制的第四上拉晶体管tu4,以及电连接在第四选通输出端子ng4与基础输入端子ns之间并且由qb节点qb的电压控制的第四下拉晶体管td4。

[0309]

图18例示了图16的选通信号输出系统(在m=4的情况下的q节点共享结构)中的选通信号之间的特性差异。图19例示了针对图16的选通信号输出系统(在m=4的情况下的q节点共享结构)中的选通信号之间的特性差异的补偿。

[0310]

参照图18,当m为4时,m个时钟信号(clk1至clkm)可以包括第一时钟信号clk1、第二时钟信号clk2、第三时钟信号clk3和第四时钟信号clk4,并且m个相关联的选通信号(vgate1至vgatem)可以包括第一选通信号vgate1、第二选通信号vgate2、第三选通信号vgate3和第四选通信号vgate4。

[0311]

参照图18,电平移位器300可以输出第一时钟信号至第四时钟信号(clk1至clk4),并且选通驱动电路130可以使用第一时钟信号至第四时钟信号(clk1至clk4)输出第一选通信号至第四选通信号(vgate1至vgate4)。

[0312]

如上所述,当不执行时钟信号控制功能以补偿选通信号之间的特性差异时,如果选通驱动电路130执行交叠选通驱动并且具有q节点共享结构,则可能出现选通信号之间的特性差异。

[0313]

不执行时钟信号控制功能以补偿选通信号之间的特性差异意指第一时钟信号至第四时钟信号(clk1至clk4)具有相等的信号波形。配置第一时钟信号至第四时钟信号(clk1至clk4)以具有相等的信号波形意指第一时钟信号至第四时钟信号(clk1至clk4)具有相同的上升特性(上升长度)和下降特性(下降长度)。

[0314]

参照图18,当m=4时,假设在第一选通信号至第四选通信号(vgate1至vgate4)当中第一选通信号vgate1的导通电压电平持续时间在最早定时进行并且第四选通信号vgate4的导通电压电平持续时间在最晚定时进行,则第一选通信号至第四选通信号(vgate1至vgate4)当中的第一选通信号vgate1的导通电压电平持续时间的上升长度r1最大。也就是说,第一选通信号至第四选通信号(vgate1至vgate4)当中的第一选通信号vgate1的上升特性最差。

[0315]

第一选通信号至第四选通信号(vgate1至vgate4)当中的第四选通信号vgate4的导通电压电平持续时间中的下降长度f4最大。也就是说,第一选通信号至第四选通信号(vgate1至vgate4)当中的第四选通信号vgate4的下降特性最差。

[0316]

比较第一选通信号至第四选通信号(vgate1至vgate4)的相应上升特性(上升长度),第一选通信号vgate1具有最差的上升特性,并且剩余选通信号的相应上升特性的差的程度可以按照第二选通信号vgate2、第三选通信号vgate3和第四选通信号vgate4的顺序。也就是说,第一选通信号vgate1可以具有最大上升长度r1,第二选通信号vgate2可以具有第二大上升长度r2,第三选通信号vgate3可以具有第三大上升长度r3,并且第四选通信号vgate4可以具有最小上升长度r4(即,r1》r2》r3》r4)。

[0317]

在这种情况下,在第一选通信号至第四选通信号(vgate1至vgate4)当中,虽然第一选通信号vgate1总是具有最大的上升长度r1,但第二选通信号至第四选通信号(vgate2至vgate4)的相应上升长度(r2、r3、r4)之间的差异可以不同地变化。

[0318]

比较第一选通信号至第四选通信号(vgate1至vgate4)的相应下降特性(下降长度),第四选通信号vgate4具有最差的下降特性,并且剩余选通信号的相应下降特性差的程度可以按照第三选通信号vgate3、第二选通信号vgate2、第一选通信号vgate1的顺序。也就是说,第四选通信号vgate4可以具有最大下降长度f4,第三选通信号vgate3可以具有第二大下降长度f3,第二选通信号vgate2可以具有第三大下降长度f2,并且第一选通信号vgate1可以具有最小下降长度f1(即,f1《f2《f3《f4)。

[0319]

在这种情况下,在第一选通信号至第四选通信号(vgate1至vgate4)中,虽然第四选通信号vgate4总是具有最大的下降长度f4,但第一选通信号至第三选通信号(vgate1至vgate3)的相应下降长度(f1、f2、f3)之间的差异可以不同地变化。

[0320]

为了减少如上所述的第一选通信号至第四选通信号(vgate1至vgate4)之间的特性差异(上升特性差异、下降特性差异)(即,补偿选通信号之间的特性差异),电平移位器300可以执行时钟信号控制功能。

[0321]

参照图19,为了减少第一选通信号至第四选通信号(vgate1至vgate4)之间的特性差异(下降特性差异),电平移位器300可以控制第一时钟信号至第三时钟信号(clk1至

clk3)的相应下降长度(cf1、cf2和cf3)变得更大以用于允许第一选通信号至第三选通信号(vgate1至vgate3)的相应下降长度(f1、f2和f3)具有与具有最差下降特性的第四选通信号vgate4的下降长度f4相似的长度。

[0322]

参照图19,第一选通信号vgate1的导通电平电压持续时间和第二选通信号vgate2的导通电平电压持续时间可以交叠,并且第二选通信号vgate2的导通电平电压持续时间和第三选通信号vgate3的导通电平电压持续时间可以交叠,并且第三选通信号vgate3的导通电平电压持续时间与第四选通信号vgate4的导通电平电压持续时间可以交叠。

[0323]

参照图19,第一选通信号vgate1的导通电平电压持续时间的定时可以早于作为最晚选通信号vgatem(其中m为4)的第四选通信号vgate4。在这种情况下,第一时钟信号clk1的下降长度cf1可以大于第四时钟信号clk4的下降长度cf4,或者第四时钟信号clk4的上升长度cr4可以大于第一时钟信号clk1的上升长度cr1。下面进行相关讨论。

[0324]

参照图19,只要第四时钟信号clk4的下降长度cf4是最小的,就可以允许第一时钟信号至第三时钟信号(clk1至clk3)的相应下降长度(cf1、cf2和cf3)之间的差异进行变化。

[0325]

参照图19,例如,第四时钟信号clk4具有最小的下降长度cf4,第三时钟信号clk3具有第二小的下降长度cf3,第二时钟信号clk2具有第三小的下降长度cf2,并且第一时钟信号clk1具有最大的下降长度cf1(即,cf4《cf3《cf2《cf1)。

[0326]

参照图19,为了减少第一选通信号至第四选通信号(vgate1至vgate4)之间的特性差异(上升特性差异),电平移位器300可以控制第二时钟信号至第四时钟信号(clk2至clk4)的相应上升长度(cr2、cr3和cr4)变得更大以用于允许第二选通信号至第四选通信号(vgate2至vgate4)的相应上升长度(r2、r3和r4)具有与具有最差上升特性的第一选通信号vgate1的上升长度r1相似的长度。

[0327]

参照图19,只要第一时钟信号clk1的上升长度cr1最小,就可以允许第二时钟信号至第四时钟信号(clk2至clk4)的相应第一上升长度(cr2、cr3和cr4)之间的差异进行变化。

[0328]

参照图19,例如,第一时钟信号clk1具有最小的上升长度cr1,第二时钟信号clk2具有第二小的上升长度cr2,第三时钟信号clk3具有第三小的上升长度cr3,并且第四时钟信号clk4具有最大的上升长度cr4(即,cr1《cr2《cr3《cr4)。

[0329]

图20是图16的选通信号输出系统中的电平移位器300的框图。图21是图19的电平移位器300的详细示图。

[0330]

参照图20和图21,电平移位器300可以将第一时钟信号clk1、第二时钟信号clk2、第三时钟信号clk3和第四时钟信号clk4输出到选通驱动电路130。

[0331]

参照图20和图21,电平移位器300可以包括:第一时钟输出缓冲器cbuf1,其用于生成第一时钟信号clk1并将所生成的第一时钟信号clk1输出到第一时钟输出端子nclk1;第二时钟输出缓冲器cbuf2,其用于生成第二时钟信号clk2并将所生成的第二时钟信号clk2输出到第二时钟输出端子nclk2;第三时钟输出缓冲器cbuf3,其用于生成第三时钟信号clk3并将所生成的第三时钟信号clk3输出到第三时钟输出端子nclk3;以及第四时钟输出缓冲器cbuf4,其用于生成第四时钟信号clk4并将所生成的第四时钟信号clk4输出到第四时钟输出端子nclk4。

[0332]

参照图21,第一时钟输出缓冲器cbuf1可以包括第一上升控制电路rcc1和第一下降控制电路fcc1,第一上升控制电路rcc1包括电连接在高电平电压节点nhv和第一时钟输

出端子nclk1之间的n个第一上升控制晶体管(rct1-1至rct1-n),并且第一下降控制电路fcc1包括电连接在低电平电压节点nlv和第一时钟输出端子nclk1之间的n个第一下降控制晶体管(fct1-1至fct1-n),其中n为2或更大的自然数。

[0333]

参照图21,第二时钟输出缓冲器cbuf2可以包括第二上升控制电路rcc2和第二下降控制电路fcc2,第二上升控制电路rcc2包括电连接在高电平电压节点nhv和第二时钟输出端子nclk2之间的n个第二上升控制晶体管(rct2-1至rct2-n),并且第二下降控制电路fcc2包括电连接在低电平电压节点nlv与第二时钟输出端子nclk2之间的n个第二下降控制晶体管(fct2-1至fct2-n)。

[0334]

参照图21,第三时钟输出缓冲器cbuf3可以包括第三上升控制电路rcc3和第三下降控制电路fcc3,第三上升控制电路rcc3包括电连接在高电平电压节点nhv和第三时钟输出端子nclk3之间的n个第三上升控制晶体管(rct3-1至rct3-n),并且第三下降控制电路fcc3包括电连接在低电平电压节点nlv与第三时钟输出端子nclk3之间的n个第三下降控制晶体管(fct3-1至fct3-n)。

[0335]

参照图21,第四时钟输出缓冲器cbuf4可以包括第四上升控制电路rcc4和第四下降控制电路fcc4,第四上升控制电路rcc4包括电连接在高电平电压节点nhv和第四时钟输出端子nclk4之间的n个第四上升控制晶体管(rct4-1至rct4-n),并且第四下降控制电路fcc4包括电连接在低电平电压节点nlv与第四时钟输出端子nclk4之间的n个第四下降控制晶体管(fct4-1至fct4-n)。

[0336]

包括在第一上升控制电路rcc1、第一下降控制电路fcc1、第二上升控制电路rcc2、第二下降控制电路fcc2、第三上升控制电路rcc3、第三下降控制电路fcc3、第四上升控制电路rcc4和第四下降控制电路fcc4中的至少一个中的n个控制晶体管的相应导通或/和截止可以被独立地控制。

[0337]

参照图21,在第一时钟输出缓冲器cbuf1中,n个第一上升控制晶体管(rct1-1至rct1-n)的相应导通或/和截止可以由n个第一上升控制信号rcs1[1:n]单独控制,并且n个第一下降控制晶体管(fct1-1至fct1-n)的相应导通或/和截止可以由n个第一下降控制信号fcs1[1:n]单独控制。

[0338]

参照图21,在第二时钟输出缓冲器cbuf2中,n个第二上升控制晶体管(rct2-1至rct2-n)的相应导通或/和截止可以由n个第二上升控制信号rcs2[1:n]单独控制,并且n个第二下降控制晶体管(fct2-1至fct2-n)的相应导通或/和截止可以由n个第二下降控制信号fcs2[1:n]单独控制。

[0339]

参照图21,在第三时钟输出缓冲器cbuf3中,n个第三上升控制晶体管(rct3-1至rct3-n)的相应导通或/和截止可以由n个第三上升控制信号rcs3[1:n]单独控制,并且n个第三下降控制晶体管(fct3-1至fct3-n)的相应导通或/和截止可以由n个第三下降控制信号fcs3[1:n]单独控制。

[0340]

参照图21,在第四时钟输出缓冲器cbuf4中,n个第四上升控制晶体管(rct4-1至rct4-n)的相应导通或/和截止可以由n个第四上升控制信号rcs4[1:n]单独控制,并且n个第四下降控制晶体管(fct4-1至fct4-n)的相应导通或/和截止可以由n个第四下降控制信号fcs4[1:n]单独控制。

[0341]

参照图21,当第一时钟信号clk1的下降长度cf1大于第四时钟信号clk4的下降长

度cf4时,n个第一下降控制晶体管(fct1-1至fct1-n)当中的导通的下降控制晶体管的数量可以小于n个第四下降控制晶体管(fct4-1至fct4-n)当中的导通的下降控制晶体管的数量。

[0342]

参照图21,当第四时钟信号clk4的上升长度cr4大于第一时钟信号clk1的上升长度cr1时,n个第四上升控制晶体管(rct4-1至rct4-n)当中的导通的上升控制晶体管的数量可以小于n个第一上升控制晶体管(rct1-1至rct1-n)当中的导通的上升控制晶体管的数量。

[0343]

图22例示了根据本公开的各方面的在显示装置100中使用至少一个电阻器(r1、r2)对选通信号之间的特性差异的补偿。

[0344]

参照图22,根据本公开的各方面的显示装置100可以包括:印刷电路板pcb,其被配置为将第一参考时钟信号ref_clk1输出到第一参考时钟输出端子nr1并将第二参考时钟信号ref_clk2输出到第二参考时钟输出端子nr2;第一电阻器r1,其连接在第一参考时钟输出端子nr1和选通驱动电路130之间;以及第二电阻器r2,其连接在第二参考时钟输出端子nr2和选通驱动电路130之间。

[0345]

参照图22,第一参考时钟信号ref_clk1和第二参考时钟信号ref_clk2是未经控制的时钟信号,并且其相应上升长度和下降长度可以彼此对应。

[0346]

第一电阻器r1和第二电阻器r2可以具有不同的电阻值。例如,第一电阻器r1的电阻值可以大于第二电阻器r2的电阻值。随着第一电阻器r1的电阻值增大,第一时钟信号clk1的上升长度和下降长度可以变得更大。随着第一电阻器r1的电阻值减小,第一时钟信号clk1的上升长度和下降长度会变得更小。

[0347]

第一时钟信号clk1可以是在第一参考时钟信号ref_clk1通过第一电阻器r1并且然后进入选通驱动电路130时的信号。第二时钟信号clk2可以是在第二参考时钟信号ref_clk2通过第二电阻器r2并且然后进入选通驱动电路130时的信号。

[0348]

图23a至图23d例示了根据本公开的各方面的通过电阻器的控制来控制和输出至少一个时钟信号(clk1、clk2)的电平移位器300,并且该电平移位器300被包括在显示装置100中。

[0349]

参照图23a,电平移位器300可以向选通驱动电路130提供m个时钟信号(clk1至clkm)。电平移位器300可以安装在印刷电路板pcb上或连接到印刷电路板pcb。

[0350]

m个时钟信号(clk1至clkm)可以包括第一时钟信号clk1和第二时钟信号clk2。

[0351]

电平移位器300可以包括第一信源引脚(sourcing pin)psrc1、第一信宿引脚(sink pin)psnk1、第二信源引脚psrc2和第二信宿引脚psnk2。

[0352]

电平移位器300可以包括位于第一信源引脚psrc1和施加有高电平电压hv的节点之间的第一高电平开关s1h以及位于第一信宿引脚psnk1和施加有低电平电压lv的节点之间的第一低电平开关s1l。

[0353]

电平移位器300可以包括位于第二信源引脚psrc2和施加有高电平电压hv的节点之间的第二高电平开关s2h以及位于第二信宿引脚psnk2与施加有低电平电压lv的节点之间的第二低电平开关s2l。

[0354]

电平移位器300还可以包括用于输出控制信号(cs1h、cs1l、cs2h和cs2l)的控制逻辑2300,以便于控制第一高电平开关s1h、第一低电平开关s1l、第二高电平开关s2h和第二

低电平开关s2l的相应开关操作。

[0355]

当第一高电平开关s1h接通时,第一时钟信号clk1可以上升到高电平电压hv,并且当第一低电平开关s1l接通时,第一时钟信号clk1可以下降到低电平电压lv。

[0356]

当第二高电平开关s2h接通时,第二时钟信号clk2可以上升到高电平电压hv,并且当第二低电平开关s2l接通时,第二时钟信号clk2可以下降到低电平电压lv。

[0357]

本文描述的第一高电平开关s1h、第一低电平开关s1l、第二高电平开关s2h和第二低电平开关s2l中的每一个可以使用晶体管来实现,并且第一高电平开关s1h、第一低电平开关s1l、第二高电平开关s2h和第二低电平开关s2l的相应控制信号(cs1h、cs1l、cs2h和cs2l)可以是施加到晶体管的栅极节点的电压。

[0358]

印刷电路板pcb可以包括第一上升控制电阻器rtr1、第一下降控制电阻器rtf1、第二上升控制电阻器rtr2和第二下降控制电阻器rtf2,并且包括第一时钟信号clk1从其输出到选通驱动电路130的第一输出节点nout1以及第二时钟信号clk2从其输出到选通驱动电路130的第二输出节点nout2。

[0359]

第一上升控制电阻器rtr1可以电连接在第一信源引脚psrc1和第一输出节点nout1之间。第一下降控制电阻器rtf1可以电连接在第一信宿引脚psnk1和第一输出节点nout1之间。

[0360]

第二上升控制电阻器rtr2可以电连接在第二信源引脚psrc2和第二输出节点nout2之间。第二下降控制电阻器rtf2可以电连接在第二信宿引脚psnk2和第二输出节点nout2之间。

[0361]

第一电容器c1可以连接在第一输出节点nout1和地gnd之间,并且第二电容器c2可以连接在第二输出节点nout2和地gnd之间。

[0362]

为了使第一时钟信号clk1的下降长度cf1变为大于第二时钟信号clk2的下降长度cf2,第一下降控制电阻器rtf1的电阻值可以被设置为大于第二下降控制电阻器rtf2的电阻值的值。

[0363]

为了使第二时钟信号clk2的上升长度cr2变为大于第一时钟信号clk1的上升长度cr1,第二上升控制电阻器rtr2的电阻值可以被设置为大于第一上升控制电阻器rtr1的电阻值的值。

[0364]

参照图23b,电平移位器300可以包括第一时钟信号输出引脚pclk1和第二时钟信号输出引脚pclk2。

[0365]

电平移位器300可以包括位于第一时钟信号输出引脚pclk1和施加有高电平电压hv的节点之间的第一高电平开关s1h,以及位于第一时钟信号输出引脚pclk1与施加有低电平电压lv的节点之间的第一低电平开关s1l。

[0366]

电平移位器300可以包括位于第二时钟信号输出引脚pclk2和施加有高电平电压hv的节点之间的第二高电平开关s2h,以及位于第二时钟信号输出引脚pclk2与施加有低电平电压lv的节点之间的第二低电平开关s2l。

[0367]

电平移位器300还可以包括用于输出控制信号(cs1h、cs1l、cs2h和cs2l)以便于控制第一高电平开关s1h、第一低电平开关s1l第二高电平开关s2h和第二低电平开关s2l的相应开关操作的控制逻辑2300。

[0368]

当第一高电平开关s1h接通时,第一时钟信号clk1可以上升到高电平电压hv,并且

当第一低电平开关s1l接通时,第一时钟信号clk1可以下降到低电平电压lv。

[0369]

当第二高电平开关s2h接通时,第二时钟信号clk2可以上升到高电平电压hv,并且当第二低电平开关s2l接通时,第二时钟信号clk2可以下降到低电平电压lv。

[0370]

印刷电路板pcb可以包括第一上升控制电阻器rtr1、第一下降控制电阻器rtf1、第二上升控制电阻器rtr2和第二下降控制电阻器rtf2。

[0371]

印刷电路板pcb可以包括第一输出节点nout1和第二输出节点nout2,第一时钟信号clk1从该第一输出节点nout1输出到选通驱动电路130,并且第二时钟信号clk2从该第二输出节点nout2输出到选通驱动电路130。

[0372]

印刷电路板pcb可以包括用于允许电流在彼此相反的方向上流动的第一上升控制二极管dr1和第一下降控制二极管df1。印刷电路板pcb可以包括用于允许电流在彼此相反的方向上流动的第二上升控制二极管dr2和第二下降控制二极管df2。

[0373]

第一上升控制二极管dr1和第一上升控制电阻器rtr1可以串联连接在第一时钟信号输出引脚pclk1和第一输出节点nout1之间。第一下降控制二极管df1和第一下降控制电阻器rtf1可以串联连接在第一时钟信号输出引脚pclk1和第一输出节点nout1之间。

[0374]

第二上升控制二极管dr2和第二上升控制电阻器rtr2可以串联连接在第二时钟信号输出引脚pclk2和第二输出节点nout2之间。第二下降控制二极管df2和第二下降控制电阻器rtf2可以串联连接在第二时钟信号输出引脚pclk2和第二输出节点nout2之间。

[0375]

第一电容器c1可以连接在第一输出节点nout1和地gnd之间,并且第二电容器c2可以连接在第二输出节点nout2和地gnd之间。

[0376]

为了使第一时钟信号clk1的下降长度cf1变为大于第二时钟信号clk2的下降长度cf2,第一下降控制电阻器rtf1的电阻值可以被设置为大于第二下降控制电阻器rtf2的电阻值的值。

[0377]

为了使第二时钟信号clk2的上升长度cr2变为大于第一时钟信号clk1的上升长度cr1,第二上升控制电阻器rtr2的电阻值可以被设置为大于第一上升控制电阻器rtr1的电阻值的值。

[0378]

参照图23c,电平移位器300可以包括第一时钟信号输出引脚pclk1和第二时钟信号输出引脚pclk2,并且包括第一上升设置引脚pr1、第一下降设置引脚pf1、第二上升设置引脚pr2和第二下降设置引脚pf2。

[0379]

电平移位器300可以包括位于第一时钟信号输出引脚pclk1和施加有高电平电压hv的节点之间的第一高电平开关s1h,以及位于第一时钟信号输出引脚pclk1与施加有低电平电压lv的节点之间的第一低电平开关s1l。

[0380]

电平移位器300可以包括位于第二时钟信号输出引脚pclk2和施加有高电平电压hv的节点之间的第二高电平开关s2h,以及位于第二时钟信号输出引脚pclk2与施加有低电平电压lv的节点之间的第二低电平开关s2l。

[0381]

电平移位器300还可以包括用于输出控制信号(cs1h、cs1l、cs2h和cs2l)以便于控制第一高电平开关s1h、第一低电平开关s1l、第二高电平开关s2h和第二低电平开关s2l的相应开关操作的控制逻辑2300。

[0382]

当第一高电平开关s1h接通时,第一时钟信号clk1可以上升到高电平电压hv,并且当第一低电平开关s1l接通时,第一时钟信号clk1可以下降到低电平电压lv。

[0383]

当第二高电平开关s2h接通时,第二时钟信号clk2可以上升到高电平电压hv,并且当第二低电平开关s2l接通时,第二时钟信号clk2可以下降到低电平电压lv。

[0384]

参照图23c,印刷电路板pcb可以包括第一上升控制电阻器rtr1、第一下降控制电阻器rtf1、第二上升控制电阻器rtr2和第二下降控制电阻器rtf2。

[0385]

第一上升控制电阻器rtr1可以电连接在第一上升设置引脚pr1和地gnd之间。第一下降控制电阻器rtf1可以电连接在第一下降设置引脚pf1和地gnd之间。

[0386]

第二上升控制电阻器rtr2可以电连接在第二上升设置引脚pr2和地gnd之间。第二下降控制电阻器rtf2可以电连接在第二下降设置引脚pf2和地gnd之间。

[0387]

参照图23c,电平移位器300还可以包括设置逻辑2310,该设置逻辑2310用于通过第一上升设置引脚pr1检测第一上升控制电阻器rtr1的电阻值、通过第一下降设置引脚pf1检测第一下降控制电阻器rtf1的电阻值、通过第二上升设置引脚pr2检测第二上升控制电阻器rtr2的电阻值并且通过第二下降设置引脚pf2检测第二下降控制电阻器rtf2的电阻值。

[0388]

例如,设置逻辑2310可以将具有已知电流值的电流提供给第一上升设置引脚pr1,此后,测量第一上升设置引脚pr1处的电压值并且然后通过将测量出的电压值除以已知的电流值来获得第一上升控制电阻器rtr1的阻值。以这样的方式,也可以获得第一下降控制电阻器rtf1、第二上升控制电阻器rtr2和第二下降控制电阻器rtf2的电阻值。

[0389]

设置逻辑2310可以将关于所获得的电阻值的电阻控制信息提供给控制逻辑2300。

[0390]

控制逻辑2300可以使用电阻控制信息来控制第一高电平开关s1h、第一低电平开关s1l、第二高电平开关s2h和第二低电平开关s2l中的每一个的电阻值(接通时的接通电阻)的电平。

[0391]

为了使第一时钟信号clk1的下降长度cf1变为大于第二时钟信号clk2的下降长度cf2,第一低电平开关s1l的电阻值可以被设置为大于第二低电平开关s2l的电阻值的值。

[0392]

为了使第二时钟信号clk2的上升长度cr2变为大于第一时钟信号clk1的上升长度cr1,第二高电平开关s2h的电阻值可以被设置为大于第一高电平开关s1h的电阻值的值。

[0393]

参照图23d,电平移位器300可以包括第一时钟信号输出引脚pclk1和第二时钟信号输出引脚pclk2,并且包括控制时钟端口pc和控制数据端口pd。

[0394]

参照图23d,电平移位器300可以包括位于第一时钟信号输出引脚pclk1和施加有高电平电压hv的节点之间的第一高电平开关s1h,以及位于第一时钟信号输出引脚pclk1与施加有低电平电压lv的节点之间的第一低电平开关s1l。

[0395]

电平移位器300可以包括位于第二时钟信号输出引脚pclk2和施加有高电平电压hv的节点之间的第二高电平开关s2h,以及位于第二时钟信号输出引脚pclk2和施加有低电平电压lv的节点之间的第二低电平开关s2l。

[0396]

电平移位器300还可以包括用于输出控制信号(cs1h、cs1l、cs2h和cs2l)以便于控制第一高电平开关s1h、第一低电平开关s1l、第二高电平开关s2h和第二低电平开关s2l的相应开关操作的控制逻辑2300。

[0397]

当第一高电平开关s1h接通时,第一时钟信号clk1可以上升到高电平电压hv,并且当第一低电平开关s1l接通时,第一时钟信号clk1可以下降到低电平电压lv。

[0398]

电平移位器300可以通过控制时钟端口pc从控制器140接收控制时钟信号scl,并

且通过控制数据端口pd从控制器140接收用于控制第一时钟信号和第二时钟信号(clk1和clk2)的相应信号波形的控制数据sda。

[0399]

电平移位器300还可以包括设置逻辑2310,设置逻辑2310用于使用控制时钟信号scl和控制数据sda检测设置值,并且将与检测到的设置值相对应的预定义的电阻控制信息提供给控制逻辑2300。设置逻辑2310可以使用寄存器来实现。

[0400]

参照图23d,例如,设置逻辑2310可以针对控制时钟信号scl的每个下降定时(或上升定时)来标识控制数据sda的电压电平,通过将所标识的电压电平与参考电压电平进行比较以观察所标识的电压电平是大于还是小于参考电压电平或所标识的电压电平大于或小于参考电压电平的程度来获得比特流(11100111)作为设置值,并且使用预定义的设置值和电阻控制信息之间的对应表来推导与所获得的设置值对应的控制信息。

[0401]

设置逻辑2310可以将关于所获得的电阻值的电阻控制信息提供给控制逻辑2300。

[0402]

控制逻辑2300可以使用电阻控制信息来控制第一高电平开关s1h、第一低电平开关s1l、第二高电平开关s2h和第二低电平开关s2l中的每一个的电阻值(接通时的接通电阻)的水平。

[0403]

为了使第一时钟信号clk1的下降长度cf1变为大于第二时钟信号clk2的下降长度cf2,第一低电平开关s1l的电阻值可以被设置为大于第二低电平开关s2l的电阻值的值。

[0404]

为了使第二时钟信号clk2的上升长度cr2变为大于第一时钟信号clk1的上升长度cr1,第二高电平开关s2h的电阻值可以被设置为大于第一高电平开关s1h的电阻值的值。

[0405]

参照图23e,电平移位器300可以包括第一时钟信号输出引脚pclk1和第二时钟信号输出引脚pclk2,并且包括控制时钟端口pc和控制数据端口pd。

[0406]

参照图23e,电平移位器300可以包括第一上升控制电阻器rtr1、第一下降控制电阻器rtf1、第二上升控制电阻器rtr2和第二下降控制电阻器rtf2。

[0407]

电平移位器300可以包括第一高电平开关s1h、第一低电平开关s1l、第二高电平开关s2h和第二低电平开关s2l。

[0408]

第一高电平开关s1h和第一上升控制电阻器rtr1可以串联连接在第一时钟信号输出引脚pclk1和施加有高电平电压hv的节点之间。第一低电平开关s1l和第一下降控制电阻器rtf1可以串联连接在第一时钟信号输出引脚pclk1和施加有低电平电压lv的节点之间。

[0409]

第二高电平开关s2h和第二上升控制电阻器rtr2可以串联连接在第二时钟信号输出引脚pclk2和施加有高电平电压hv的节点之间。第二低电平开关s2l和第二下降控制电阻器rtf2可以串联连接在第二时钟信号输出引脚pclk2和施加有低电平电压lv的节点之间。

[0410]

电平移位器300还可以包括用于输出控制信号(cs1h、cs1l、cs2h和cs2l)以便于控制第一高电平开关s1h、第一低电平开关s1l、第二高电平开关s2h和第二低电平开关s2l的相应开关操作的控制逻辑2300。

[0411]

当第一高电平开关s1h接通时,第一时钟信号clk1可以上升到高电平电压hv,并且当第一低电平开关s1l接通时,第一时钟信号clk1可以下降到低电平电压lv。

[0412]

电平移位器300可以通过控制时钟端口pc从控制器140接收控制时钟信号scl,并且通过控制数据端口pd从控制器140接收用于控制第一时钟信号和第二时钟信号(clk1和clk2)的相应信号波形的控制数据sda。

[0413]

电平移位器300还可以包括设置逻辑2310,该设置逻辑2310用于使用控制时钟信

号scl和控制数据sda检测设置值,并且将与检测到的设置值相对应的预定义电阻控制信息提供给控制逻辑2300。设置逻辑2310可以使用寄存器来实现。

[0414]

参照图23d,例如,设置逻辑2310可以针对控制时钟信号scl的每个下降定时(或上升定时)来标识控制数据sda的电压电平,通过比较所标识的电压电平与参考电压电平以观察所标识的电压电平是大于还是小于参考电压电平或所标识的电压电平大于或小于参考电压电平的程度来获得比特流(11100111)作为设置值,并且利用预定义的设置值和电阻控制信息之间的对应表来推导与所获得的设置值相对应的控制信息。

[0415]

设置逻辑2310可以基于控制信息使用软件工具来控制第一上升控制电阻器rtr1、第一下降控制电阻器rtf1、第二上升控制电阻器rtr2和第二下降控制电阻器rtf2的相应电阻值。

[0416]

为了使第一时钟信号clk1的下降长度cf1变为大于第二时钟信号clk2的下降长度cf2,第一下降控制电阻器rtf1的电阻值可以被设置为大于第二下降控制电阻器rtf2的电阻值的值。

[0417]

为了使第二时钟信号clk2的上升长度cr2变为大于第一时钟信号clk1的上升长度cr1,第二上升控制电阻器rtr2的电阻值可以被设置为大于第一上升控制电阻器rtr1的电阻值的值。

[0418]

此外,第一上升控制电阻器rtr1、第一下降控制电阻器rtf1、第二上升控制电阻器rtr2和第二下降控制电阻器rtf2的相应电阻值可以分别为第一高电平开关s1h、第一低电平开关s1l、第二高电平开关s2h和第二低电平开关s2l的相应电阻值(接通时的接通电阻)。

[0419]

在这种情况下,设置逻辑2300可以控制第一高电平开关s1h、第一低电平开关s1l、第二高电平开关s2h和第二低电平开关s2l中的每一个的电阻值(接通时的接通电阻)的水平。

[0420]

为了使第一时钟信号clk1的下降长度cf1变为大于第二时钟信号clk2的下降长度cf2,第一低电平开关s1l的电阻值可以被设置为大于第二低电平开关s2l的电阻值的值。

[0421]

为了使第二时钟信号clk2的上升长度cr2变为大于第一时钟信号clk1的上升长度cr1,第二高电平开关s2h的电阻值可以被设置为大于第一高电平开关s1h的电阻值的值。

[0422]

控制包括在图23c、图23d和图23e的电平移位器300中的第一高电平开关s1h、第一低电平开关s1l、第二高电平开关s2h和第二低电平开关(s1h)中的至少一个开关的电阻值(接通时的接通电阻)的水平的方法可以包括控制并联开关中的接通开关的数量的方法和控制控制信号的电压的方法。

[0423]

调整并联开关中的接通开关的数量的方法如下。

[0424]

如图10a至图10d、图11a至图11d、图12、图14和图21所示,在配置了开关的情况下,需要利用并联连接的多个子开关(例如,rct1-1至rct1-n)来调整电阻值,可以通过调整并联连接的多个子开关中的接通开关的数量来控制开关的电阻值。

[0425]

控制控制信号的电压的方法是控制控制开关的接通和/或关断的控制信号(cs1h、cs1l、cs2h和cs2l)的电压的方法。这将参照图24更详细地描述。

[0426]

图24是例示根据本公开的各方面的用于控制包括在显示装置100中的电平移位器300中的开关(s1h、s1l、s2h和s2l)的电阻水平的控制信号cs的图。

[0427]

参照图24,可以控制控制信号(控制信号(cs1h、cs1l、cs2h和cs2l)的对应信号)的

电压变化,以便于控制包括在图23c、图23d和图23e中的电平移位器中的第一高电平开关s1h、第一低电平开关s1l、第二高电平开关s2h和第二低电平开关s2l中的至少一个开关的电阻值(接通时的接通电阻)的水平。

[0428]

为了使时钟信号clk1的下降长度cf1变得更大,下面以控制第一低电平开关s1l的电阻值为例进行讨论。

[0429]

控制逻辑2300可以将施加到第一低电平开关s1l的控制信号cs1l的电压从截止电压voff切换到导通电压von,以便于导通第一低电平开关s1l。

[0430]

为了增大第一低电平开关s1l的电阻值,当将控制信号cs1l的电压从截止电压voff切换到导通电压von时,控制逻辑2300可以以相对减小的速度从截止电压voff切换到导通电压von。

[0431]

如图24所示,随着施加到第一低电平开关s1l的控制信号cs1l的电压从截止电压voff缓慢切换到导通电压von(即,随着图24的曲线中的斜率变得更平缓),通过第一低电平开关s1l的电流流得更慢,这产生的效果等于第一低电平开关s1l的电阻值增加。

[0432]

图25例示了根据本公开的各方面的当在显示装置100中应用如图6a和图6b中的q节点共享结构时对选通信号之间的特性差异的补偿的效果。

[0433]

图25示出了在m=2的情况下应用选通信号之间的特性差异补偿控制之前和之后的第一选通信号vgate1、第二选通信号vgate2和q节点电压的曲线图。

[0434]

参照图25,在应用选通信号之间的特性差异补偿控制之前,第一选通信号和第二选通信号(vgate1和vgate2)的下降特性如下。在这种情况下,下降长度表示电压电平达到下降前电压值的90%的时间与电压电平达到下降前电压值的10%的时间之间的差。

[0435]

参照图25,在应用选通信号之间的特性差异补偿控制之前,第一选通信号vgate1的下降长度为1.64μs。第二选通信号vgate2的下降长度为2.08μs。

[0436]

参照图25,在应用选通信号之间的特性差异补偿控制之前,第一选通信号vgate1与第二选通信号vgate2的下降长度差(下降差)为0.44μs(=2.08-1.61)。

[0437]

需要注意的是,在效果验证模拟中,当应用了选通信号之间的特性差异补偿控制时,仅应用了用于允许第一时钟信号clk1的下降长度cf1变得更大的下降控制。

[0438]

参照图25,在应用了选通信号之间的特性差异补偿控制之后的第一选通信号vgate1的下降特性如下。通过第一选通信号vgate1的下降过程,当从下降长度方面来测量时,电压电平达到下降前电压值的90%的时间与电压电平达到下降前电压值的10%的时间之间的差表现为从应用特性差异补偿控制之前测量的1.64μs延长的1.94μs。

[0439]

参照图25,在应用了选通信号之间的特性差异补偿控制之后的第二选通信号vgate2的下降特性如下。通过第二选通信号vgate2的下降过程,当从下降长度方面来测量时,电压电平达到下降前电压值的90%的时间与电压电平达到下降前电压值的10%的时间之间的差表现为2.08μs。

[0440]

参照图25,在应用了选通信号之间的特性差异补偿控制之后,第一选通信号vgate1与第二选通信号vgate2的下降长度差(下降差)为0.14μs(=2.08-1.94)。该值与作为应用选通信号之间的特性差异补偿控制之前的下降长度之间的差值的0.44μs相比显著减小。

[0441]

因此,可以通过第一时钟信号clk1的下降控制来减小第一选通信号vgate1和第二

选通信号vgate2之间的下降特性的差异。

[0442]

图26例示了根据本公开的各方面的当在显示装置100中应用如图17中的q节点共享结构(m=4)时的补偿选通信号之间的特性差异的功能的效果。

[0443]

图26示出了在m=4的情况下在应用选通信号之间的特性差异补偿控制之前和之后的第一选通信号至第四选通信号(vgate1至vgate4)和q节点电压的曲线图。

[0444]

参照图26,在应用选通信号之间的特性差异补偿控制之前,第一选通信号至第四选通信号(vgate1至vgate4)的下降特性如下。在这种情况下,下降长度表示电压电平达到下降前电压值的90%的时间与电压电平达到下降前电压值的10%的时间之间的差。

[0445]

参照图26,在应用选通信号之间的特性差异补偿控制之前,第一选通信号vgate1的下降长度为1.91μs。第二选通信号vgate2的下降长度为1.83μs。第三选通信号vgate3的下降长度为2.17μs。第四选通信号vgate4的下降长度为2.42μs。

[0446]

参照图26,在应用选通信号之间的特性差异补偿控制之前,第一选通信号至第四选通信号(vgate1至vgate4)之间的下降长度最大差(最大下降差)为0.59μs(=2.42-1.83)。

[0447]

需要注意的是,在效果验证仿真中,当应用选通信号之间的特性差异补偿控制时,应用下降控制以允许:第一时钟信号clk1的下降长度cf1变为最大;第二时钟信号clk2的下降长度cf2变为第二大;并且第三时钟信号clk3的下降长度cf3小于第二时钟信号clk2的下降长度cf2。

[0448]

参照图26,在应用选通信号之间的特性差异补偿控制之后,第一选通信号至第四选通信号(vgate1至vgate4)的下降特性如下。

[0449]

参照图26,在应用选通信号之间的特性差异补偿控制之后,第一选通信号vgate1的下降长度为2.06μs。第二选通信号vgate2的下降长度为1.96μs。第三选通信号vgate3的下降长度为1.99μs。第四选通信号vgate4的下降长度为2.36μs。

[0450]

参照图26,在应用选通信号之间的特性差异补偿控制之后,第一选通信号至第四选通信号(vgate1至vgate4)之间的下降长度最大差(最大下降差)为0.40μs(=2.36-1.96)。该值与作为应用选通信号之间的特性差异补偿控制之前的下降长度之间的差异值的0.59μs相比显著减小。

[0451]

因此,可以通过第一时钟信号至第四时钟信号(clk1至clk4)的下降控制来减少第一选通信号至第四选通信号(vgate1至vgate4)之间下降特性的差异。

[0452]

根据本文描述的实施方式,可以提供能够减少选通信号之间的特性差异从而提高图像质量的电平移位器300、选通驱动电路130和显示装置100。

[0453]

根据本文描述的实施方式,可以提供能够对时钟信号的上升特性和下降特性进行各种控制的电平移位器300,以及使用电平移位器300的选通驱动电路130和显示装置100。

[0454]

根据本文描述的实施方式,可以提供即使当选通驱动电路作为嵌入类型嵌入显示面板中时也能够减小其中设置选通驱动电路的区域的尺寸并且减小选通信号之间的特性差异的电平移位器300、选通驱动电路130和显示装置100。

[0455]

以上描述是为了使本领域技术人员能够实现和使用本发明的技术思想,并且是在特定应用及其要求的上下文中提供的。对所描述的实施方式的各种修改、添加和替换对于本领域技术人员来说将是显而易见的,并且在不脱离本发明的精神和范围的情况下,本文

定义的一般原理可以应用于其它实施方式和应用。以上描述和附图仅出于说明的目的提供了本发明的技术思想的示例。也就是说,所公开的实施方式旨在说明本发明的技术思想的范围。因此,本发明的范围不限于所示的实施方式,而是符合与权利要求一致的最宽范围。本发明的保护范围应基于所附权利要求进行解释,凡在其等同范围内的技术思想均应理解为包含在本发明的保护范围内。

[0456]

相关申请的交叉引用

[0457]

本技术要求于2020年12月24日向韩国知识产权局提交的韩国专利申请第10-2020-0183863号的优先权权益,其公开内容通过引用整体并入本文。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1