阵列基板、显示面板及显示装置的制作方法

1.本技术属于显示技术领域,尤其涉及一种阵列基板、显示面板及显示装置。

背景技术:

2.随着显示技术的发展,用户对显示装置的屏占比要求越来越高,窄边框设计已经成为了显示装置的一大发展趋势。

3.显示装置具有显示区和非显示区。非显示区中设置有扇形走线区,扇形走线区中设置有大量走线,这些走线占据的空间较大,导致扇形走线区的宽度较大,无法进一步压缩显示装置的边框,难以实现显示装置的更窄边框。

技术实现要素:

4.本技术实施例提供一种阵列基板、显示面板及显示装置,能够实现显示装置更窄的边框。

5.第一方面,本技术实施例提供一种阵列基板,阵列基板具有显示区和非显示区,显示区包括中心区域和位于中心区域沿第一方向上的至少一侧的边缘区域,阵列基板包括:中心数据线,位于中心区域,沿第二方向延伸,第二方向与第一方向呈一定角度;边缘数据线,位于边缘区域,沿第二方向延伸;中心连接线,位于非显示区并沿第二方向延伸,中心数据线通过中心连接线与驱动集成电路的连接端口电连接;边缘连接线,边缘连接线包括第一连接线段、第二连接线段和第三连接线段,第一连接线段和第二连接线段位于显示区并至少部分沿第一方向延伸,第一连接线段、第二连接线段与边缘数据线连接,第三连接线段沿第二方向延伸,第一连接线段、第二连接线段通过第三连接线段与驱动集成电路的连接端口电连接,其中,沿第二方向,多条第一连接线段各自连接的边缘数据线和中心区域的距离的变化趋势,与多条第二连接线段各自连接的边缘数据线和中心区域的距离的变化趋势相反,部分第二连接线段位于相邻的两条第一连接线段之间,和/或,部分第一连接线段位于相邻的两条第二连接线段之间。

6.根据第一方面的实施方式,沿第二方向,第一连接线段和第二连接线段按照m:n的比例交替排列,m、n为正整数。

7.根据本技术第一方面前述任一实施方式,第一方向与第二方向垂直。

8.根据本技术第一方面前述任一实施方式,m:n可包括以下任意一者:1:1、1:2、1:3、2:3、2:1、3:1、3:2。

9.根据本技术第一方面前述任一实施方式,边缘连接线还包括第一目标连接线段和第二目标连接线段;第一目标连接线段与距离中心区域最远的边缘数据线连接且至少部分沿第一方向延伸,第二目标连接线段沿第二方向延伸,第一目标连接线段通过第二目标连接线段与驱动集成电路的连接端口电连接;与第一连接线段连接的第三连接线段和与第二连接线段连接的第三连接线段,位于第二目标连接线段远离边缘区域的一侧。

10.根据本技术第一方面前述任一实施方式,第一目标连接线与距离中心区域最远的

边缘数据线和驱动集成电路的连接端口最近的一端连接。

11.根据本技术第一方面前述任一实施方式,边缘连接线还包括第四连接线段和第五连接线段;第四连接线段与边缘数据线连接且至少部分沿第一方向延伸,第五连接线段沿第二方向延伸,第四连接线段通过第五连接线段与驱动集成电路的连接端口电连接,第五连接线段位于第二目标连接线段靠近边缘区域的一侧。

12.根据本技术第一方面前述任一实施方式,第四连接线段的数量为p,p条第四连接线段与距离中心区域最近的p条边缘数据线连接,p为正整数。

13.根据本技术第一方面前述任一实施方式,该阵列基板还包括像素电路列和虚拟像素电路列,一组虚拟像素电路列位于两组像素电路列之间,至少部分第三连接线段的正投影与虚拟像素电路列的正投影交叠,一组虚拟像素电路列包括至少一个虚拟像素电路列,一组像素电路列包括至少一个像素电路列。

14.根据本技术第一方面前述任一实施方式,第二目标连接线段的正投影与虚拟像素电路列的正投影交叠。

15.根据本技术第一方面前述任一实施方式,第五连接线段的正投影与虚拟像素电路列的正投影交叠。

16.根据本技术第一方面前述任一实施方式,阵列基板还包括像素列,虚拟像素电路列和像素电路列的正投影位于像素列所在的区域的正投影之内。

17.根据本技术第一方面前述任一实施方式,像素列的数量小于电路列数量和,电路列数量和为像素电路列的数量与虚拟像素电路列的数量之和。

18.根据本技术第一方面前述任一实施方式,沿第一方向,像素电路列和虚拟像素电路列按照q:1的比例交替排列。

19.根据本技术第一方面前述任一实施方式,该阵列基板还包括:换线连接单元,与边缘连接线、驱动集成电路的连接端口电连接,用于使边缘数据线通过边缘连接线和换线连接单元,按照边缘数据线的排列顺序与对应顺序的连接端口电连接。

20.根据本技术第一方面前述任一实施方式,换线连接单元包括:换线连接线,一端与边缘连接线一一对应电连接,另一端与边缘连接线连接的边缘数据线对应顺序的连接端口电连接。

21.第二方面,本技术实施例提供一种显示面板,包括第一方面的阵列基板。

22.第三方面,本技术实施例提供一种显示装置,包括第二方面的显示面板。

23.本技术实施例提供一种阵列基板、显示面板及显示装置,阵列基板包括位于中心区域的中心数据线和位于边缘区域的边缘数据线。中心数据线通过中心连接线与驱动集成电路的连接端口电连接。边缘数据线通过第一连接线段和第三连接线段与驱动集成电路的连接端口电连接,以及,边缘数据线通过第二连接线段和第三连接线段与驱动集成电路的连接端口电连接,即,边缘数据线通过边缘连接线与驱动集成电路的连接端口电连接。位于非显示区中的中心连接线,以及第三连接线段位于非显示区中的部分均沿第二方向延伸,并没有形成扇形走线区,也不会受到扇形走线区形状的限制,非显示区中连接线段的走线距离可进一步压缩,从而进一步缩短包括阵列基板的显示装置的下边框的宽度,以实现显示装置更窄的边框。

附图说明

24.为了更清楚地说明本技术实施例的技术方案,下面将对本技术实施例中所需要使用的附图作简单的介绍,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

25.图1为显示装置的一示例的俯视示意图;

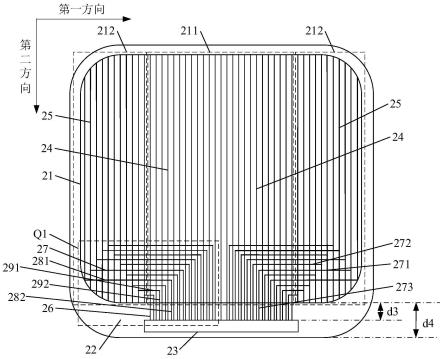

26.图2为本技术一实施例提供的阵列基板的结构示意图;

27.图3为图2中区域q1的局部放大图;

28.图4为本技术另一实施例提供的阵列基板的结构示意图;

29.图5为图4中区域q2的局部放大图;

30.图6为本技术又一实施例提供的阵列基板的结构示意图;

31.图7为图6中区域q3的局部放大图;

32.图8为边缘连接线只包括第二连接线段和第三连接线段的阵列基板的结构示意图;

33.图9为图8所示阵列基板与本技术实施例中阵列基板边缘数据线与驱动集成电路的连接端口之间连接线段的电容的比较示意图;

34.图10为本技术实施例提供的部分第三连接线段设置位置的一示例的示意图;

35.图11为本技术实施例中功能区域的一示例的示意图;

36.图12为本技术实施例中显示装置的一示例的侧截面的示意图;

37.图13为本技术实施例中显示装置的另一示例的侧截面的示意图;

38.图14为本技术实施例中显示装置的又一示例的侧截面的示意图。

具体实施方式

39.下面将详细描述本技术的各个方面的特征和示例性实施例,为了使本技术的目的、技术方案及优点更加清楚明白,以下结合附图及具体实施例,对本技术进行进一步详细描述。应理解,此处所描述的具体实施例仅意在解释本技术,而不是限定本技术。对于本领域技术人员来说,本技术可以在不需要这些具体细节中的一些细节的情况下实施。下面对实施例的描述仅仅是为了通过示出本技术的示例来提供对本技术更好的理解。

40.随着显示技术的发展,用户对显示装置的屏占比要求越要越高,显示装置窄边框设计已经成为了一大发展趋势。图1为显示装置的一示例的俯视示意图。如图1所示,显示装置具有显示区aa和非显示区na。在非显示区na中设置有扇形走线区11,即非显示区na中的走线可形成一个梯形区域。扇形走线区11中设置有大量走线,在走线数量非常大的情况下,扇形走线区11的宽度d1受到扇形走线区11形状的限制,不能继续减小,即扇形走线区11的宽度d1较大,导致非显示区的宽度较大,进而使得显示装置的边框尤其是下边框的宽度d2无法进一步压缩,难以实现显示装置更窄的边框。

41.本技术提供一种阵列基板、显示面板及显示装置,通过调整数据线的走线,使得非显示区的宽度能够进一步缩短,从而进一步压缩显示装置的边框,在保证显示效果的基础上,实现边框更窄的显示装置。

42.下面对阵列基板、显示面板及显示装置依次进行说明。

43.图2为本技术一实施例提供的阵列基板的结构示意图。图3为图2中区域q1的局部

放大图。如图2和图3所示,该阵列基板具有显示区21和非显示区22。显示区21包括中心区域211和位于中心区域211沿第一方向上的至少一侧的边缘区域212。边缘区域212可位于中心区域211沿第一方向上的一侧,也可位于中心区域211沿第一方向上的两侧。即中心区域211可对应设置有一个边缘区域212或两个边缘区域212,在此并不限定。例如,图2所示的中心区域211沿第一方向上的两侧均具有边缘区域212。

44.非显示区22中沿第二方向与显示区21对应的区域可包括能够实现某种或某些功能的部件和区域,在此并不限定。为了便于说明,将非显示区22中沿第二方向与显示区21对应的区域称为功能区域23。例如,在包括阵列基板的显示装置采用cop封装方式即chip on pi封装方式或cof封装方式即chip on film封装方式的情况下,功能区域23可包括弯折区域即bending区域。又例如,在包括阵列基板的显示装置采用cog封装方式即chip on glass封装方式的情况下,功能区域23可包括驱动集成电路(integrated circuit,ic)。

45.在一些示例中,边缘区域212为中心区域211沿第一方向相对于功能区域23凸出的区域。即中心区域211沿第二方向在第一方向上的投影与功能区域23沿第二方向在第一方向上的投影重合。边缘区域212沿第二方向在第一方向上的投影与功能区域23沿第二方向在第一方向上的投影不重合。

46.上述实施例中的第一方向和第二方向不同,可呈一定角度。在一些示例中,第一方向与第二方向相互垂直。例如,第一方向可为显示区中像素单元的行方向,第二方向可为显示区中像素单元的列方向。这里的像素单元具体可指子像素,如红色子像素、绿色子像素和蓝色子像素,在此并不限定。

47.阵列基板可包括中心数据线24、边缘数据线25、中心连接线26和边缘连接线27。

48.中心数据线24位于中心区域211,沿第二方向延伸。多条中心数据线24沿第一方向间隔分布。图2和图3中的中心数据线24的数量只是示意,在实际情况中,中心区域211中的中心数据线24的数量会更多。例如,包括阵列基板的显示装置的分辨率为2340*1080,中心数据线24的数量可达到1440条。

49.边缘数据线25位于边缘区域212,沿第二方向延伸。多条边缘数据线25沿第一方向间隔分布。图2和图3中的边缘数据线25的数量只是示意,在实际情况中,边缘区域212中的边缘数据线25的数量会更多。例如,包括阵列基板的显示装置的分辨率为2340*1080,边缘数据线25的数量可达到720条。

50.中心数据线24与边缘数据线25可为显示区21中的像素单元提供数据信号。

51.中心连接线26位于非显示区22,并沿第二方向延伸。中心数据线24与中心连接线26可一一对应电连接。中心数据线24可通过中心连接线26与驱动集成电路的连接端口电连接。中心数据线24与中心连接线26可一体成型。在一些示例中,中心数据线24可位于显示区21与非显示区22中的功能区域23之间。

52.边缘连接线27包括第一连接线段271、第二连接线段272和第三连接线段273。

53.第一连接线段271和第二连接线段272位于显示区21,并至少部分沿第一方向延伸。第一连接线段271、第二连接线段272与边缘数据线25连接。一条第一连接线段271与一条边缘数据线25连接,一条第二连接线段272与一条边缘数据线25连接。

54.在一些示例中,第一连接线段271和第二连接线段272为直线型,如图2和图3所示,对于一条第一连接线段271来说,该第一连接线段271整体沿第一方向延伸,对于一条第二

连接线段272来说,第二连接线段272整体沿第一方向延伸。

55.在另一些示例中,第一连接线段271和第二连接线段272可为折线型或其他具有弯折的连接线段,在此并不限定弯折的形状。图4为本技术另一实施例提供的阵列基板的结构示意图。图5为图4中区域q2的局部放大图。图4与图2的不同之处在于,图4中第一连接线段271和第二连接线段272为折线型,第一连接线段271包括沿第一方向延伸的线段和沿其他方向延伸的线段,第二连接线段272包括沿第一方向延伸的线段和沿其他方向延伸的线段。如图4和图5所示,第一连接线段271包括沿第一方向延伸的线段和沿第二方向延伸的线段,第二连接线段272包括沿第一方向延伸的线段和沿第二方向延伸的线段。

56.第三连接线段273沿第二方向延伸。一条第三连接线段273部分位于显示区21,另一部分位于非显示区22。第三连接线段273与第一连接线段271、第二连接线段272连接。一条第三连接线段273与一条第一连接线段271或一条第二连接线段272连接。第三连接线段273与驱动集成电路的连接端口电连接。第一连接线段271、第二连接线段272通过第三连接线段273与驱动集成电路的连接端口电连接。对应地,第一连接线段271连接的边缘数据线25通过第一连接线段271、第三连接线段273与驱动集成电路的连接端口电连接,第二连接线段272连接的边缘数据线25通过第二连接线段272、第三连接线段273与驱动集成电路的连接端口电连接。

57.驱动集成电路的连接端口可与驱动集成电路一体设置,也可与驱动集成电路分离设置,在此并不限定。

58.在上述实施例中,沿第二方向,多条第一连接线段271各自连接的边缘数据线25和中心区域211的距离的变化趋势,与多条第二连接线段272各自连接的边缘数据线25和中心区域211的距离的变化趋势相反。边缘数据线25和中心区域211的距离的变化趋势可包括逐渐增大和逐渐减小。例如,多条第一连接线段271各自连接的边缘数据线25和中心区域211的距离的变化趋势可为逐渐增大,多条第二连接线段271各自连接的边缘数据线25和中心区域211的距离的变化趋势可为逐渐减小。又例如,多条第一连接线段271各自连接的边缘数据线25和中心区域211的距离的变化趋势可为逐渐减小,多条第二连接线段271各自连接的边缘数据线25和中心区域211的距离的变化趋势可为逐渐增大。部分第二连接线段272位于相邻的两条第一连接线段271之间,和/或,部分第一连接线段271位于相邻的两条第二连接线段272之间。沿边缘区域212指向中心区域211的方向,多条第三连接线段273的长度逐渐增大。在一些示例中,多条第三连接线段273的长度可等量增大。

59.为了便于理解,本技术实施例以多条第一连接线段271各自连接的边缘数据线25和中心区域211的距离的变化趋势为逐渐增大,多条第二连接线段271各自连接的边缘数据线25和中心区域211的距离的变化趋势为逐渐减小为例进行说明。

60.例如,如图3所示,边缘数据线25包括边缘数据线b1至边缘数据线b11。在连接线段a1至连接线段a11中,第一连接线段271可包括连接线段a2、连接线段a4、连接线段a6和连接线段a8,第二连接线段272可包括连接线段a1、连接线段a3、连接线段a5、连接线段a7、连接线段a9、连接线段a10和连接线段a11。第三连接线段273可包括连接线段c1至连接线段c11。连接线段a2位于连接线段a1和连接线段a3之间,连接线段a4位于连接线段a3和连接线段a5之间,连接线段a6位于连接线段a5和连接线段a7之间,连接线段a8位于连接线段a9和连接线段a10之间,连接线段a3位于连接线段a2和连接线段a4之间,接线段a5位于连接线段a4和

连接线段a6之间,接线段a7位于连接线段a6和连接线段a8之间。沿第二方向,连接线段a2、连接线段a4、连接线段a6和连接线段a8按该顺序排列。与连接线段a2连接的边缘数据线b4、与连接线段a4连接的边缘数据线b3、与连接线段a6连接的边缘数据线b2、与连接线段a8连接的边缘数据线b1和中心区域211的距离的变化趋势为逐渐增大,即上述边缘数据线距离中心区域211越来越远。沿第二方向,连接线段a1、连接线段a3、连接线段a5、连接线段a7、连接线段a9、连接线段a10和连接线段a11按该顺序排列。与连接线段a1连接的边缘数据线b5、与连接线段a3连接的边缘数据线b6、与连接线段a5连接的边缘数据线b7、与连接线段a7连接的边缘数据线b8、与连接线段a9连接的边缘数据线b9、与连接线段a10连接的边缘数据线b10、与连接线段a11连接的边缘数据线b11和中心区域211的距离的变化趋势为逐渐减小,即上述边缘数据线距离中心区域211越来越近。沿第一方向,连接线段c11至连接线段c1按照该顺序排列。

61.又例如,如图3所示,边缘数据线25包括边缘数据线b1至边缘数据线b11。在连接线段a1至连接线段a11中,第一连接线段271可包括连接线段a2、连接线段a4和连接线段a6,第二连接线段272可包括连接线段a1、连接线段a3、连接线段a5和连接线段a7。第三连接线段273可包括连接线段c1至连接线段c8。连接线段a2位于连接线段a1和连接线段a3之间,连接线段a4位于连接线段a3和连接线段a5之间,连接线段a6位于连接线段a5和连接线段a7之间,连接线段a3位于连接线段a2和连接线段a4之间,接线段a5位于连接线段a4和连接线段a6之间,接线段a7位于连接线段a6和连接线段a8之间。沿第二方向,连接线段a2、连接线段a4和连接线段a6按该顺序排列。与连接线段a2连接的边缘数据线b4、与连接线段a4连接的边缘数据线b3、与连接线段a6连接的边缘数据线b2和中心区域211的距离的变化趋势为逐渐增大,即上述边缘数据线距离中心区域211越来越远。沿第二方向,连接线段a1、连接线段a3、连接线段a5和连接线段a7按该顺序排列。与连接线段a1连接的边缘数据线b5、与连接线段a3连接的边缘数据线b6、与连接线段a5连接的边缘数据线b7、与连接线段a7连接的边缘数据线b8和中心区域211的距离的变化趋势为逐渐减小,即上述边缘数据线距离中心区域211越来越近。沿第一方向,连接线段c8至连接线段c1按照该顺序排列。

62.在一些示例中,沿第二方向,第一连接线段271和第二连接线段272按照m:n的比例交替排列,m、n为正整数。即xm条第一连接线段271和xn条第二连接线段272交替排列,x为正整数。在一些示例中,m:n可包括但不限于以下任意一者:1:1、1:2、1:3、2:3、2:1、3:1、3:2。但m和n的取值可根据应用场景和应用需求设定,在此并不限定。例如,m:n=1:1,可包括沿第二方向一条第一连接线段271和一条第二连接线段272交替排列的方式,也可包括沿第二方向两条第二连接线段271和两条第二连接线段272交替排列的方式,还可包括沿第二方向三条第二连接线段271和三条第二连接线段272交替排列的方式,在此并不限定,其他m:n比例的交替排列也可以此类推。

63.例如,边缘数据线25包括边缘数据线b1至边缘数据线b11。在连接线段a1至连接线段a11中,第一连接线段271可包括连接线段a2、连接线段a4和连接线段a6,第二连接线段272可包括连接线段a1、连接线段a3、连接线段a5和连接线段a7。沿第二方向,第一连接线段271和第二连接线段272是按照1:1的比例交替排列的。

64.图6为本技术又一实施例提供的阵列基板的结构示意图。图7为图6中区域q3的局部放大图。图6与图2的不同之处在于,第一连接线段271和第二连接线段272按照1:2的比例

交替排列。

65.例如,如图6所示,第一连接线段271可包括连接选段a13、连接线段a16和连接线段a19,第二连接线段271可包括连接线段a14、连接线段a15、连接线段17和连接线段a18,第三连接线段包括连接线段c13至c19。沿第二方向,连接线段a13、连接线段a16和连接线段a19按该顺序排列。与连接线段a13连接的边缘数据线b14、与连接线段a16连接的边缘数据线b13、与连接线段a19连接的边缘数据线b12和中心区域211的距离的变化趋势逐渐增大,即上述边缘数据线距离中心区域211越来越远。沿第二方向,连接线段a14、连接线段a15、连接线段a17和连接线段a18按该顺序排列。与连接线段a14连接的边缘数据线b16、与连接线段a15连接的边缘数据线b17、与连接线段a17连接的边缘数据线b18、与连接线段a18连接的边缘数据线b19和中心区域211的距离的变化趋势逐渐减小,即上述边缘数据线距离中心区域211越来越近。沿第一方向,连接线段c19至连接线段c13按照该顺序排列。

66.位于非显示区22中的中心连接线26,以及第三连接线段273位于非显示区22中的部分均沿第二方向延伸,并没有形成扇形走线区,也不会受到扇形走线区形状的限制,中心区域211与功能区域23之间的距离d3可进一步压缩,对应地,包括阵列基板的显示装置的下边框的宽度d4可进一步缩短。图2、图4和图6中的d3要小于图1中的d1,图2、图4和图6中的d4要小于图1中的d2。

67.在本技术实施例中,阵列基板包括位于中心区域211的中心数据线24和位于边缘区域212的边缘数据线25。中心数据线24通过中心连接线26与驱动集成电路的连接端口电连接。边缘数据线25通过第一连接线段271和第三连接线段273与驱动集成电路的连接端口电连接,以及,边缘数据线25通过第二连接线段272和第三连接线段273与驱动集成电路的连接端口电连接,即,边缘数据线25通过边缘连接线与驱动集成电路的连接端口电连接。位于非显示区22中的中心连接线26,以及第三连接线段273位于非显示区22中的部分均沿第二方向延伸,并没有形成扇形走线区,也不会受到扇形走线区形状的限制,非显示区中连接线段的走线距离可进一步压缩,从而进一步缩短包括阵列基板的显示装置的下边框的宽度,以实现显示装置更窄的边框。

68.例如,现阶段显示装置中显示区与功能区域之间的距离为1.0毫米左右,显示装置的下边框宽度在2.5毫米至3毫米左右,而包括本技术实施例中的阵列基板的显示装置中显示区与功能区域之间的距离可再缩短0.5毫米左右或更小,显示装置的下边框的宽度可缩短至2毫米甚至2毫米以下。

69.沿第一方向,与第一连接线段271连接的第三连接线段273以及与第二连接线段272连接的第三连接线段273的长度逐渐增大。边缘数据线25距离中心区域越远,与该边缘数据线25连接的第一连接线段271或第二连接线段272的长度就可能会越大。为了避免不同边缘数据线25和驱动集成电路的连接端口之间的边缘连接线27的长度之间差距过大造成的电容突变,本技术实施例中,按照沿第二方向,多条第一连接线段271各自连接的边缘数据线25距离中心区域211越来越远,多条第二连接线段272各自连接的边缘数据线25距离中心区域211越来越近,且第一连接线段271和第二连接线段272沿第二方向交杂分布的规律,设置连接线段,使得连接的第一连接线段271和第三连接线段273的长度之和、连接的第二连接线段272和第三连接线段273的长度之和的差距在可接受范围内,避免连接的第一连接线段271和第三连接线段273的长度之和、连接的第二连接线段272和第三连接线段273的长

度之和发生突变,尽可能地减少边缘数据线25和驱动集成电路的连接端口之间的边缘连接线27的负载,从而保证包括阵列基板的显示装置的显示效果。

70.图8为边缘连接线只包括第二连接线段和第三连接线段的阵列基板的结构示意图。图9为图8所示阵列基板与本技术实施例中阵列基板边缘数据线与驱动集成电路的连接端口之间连接线段的电容的比较示意图。图8所示的阵列基板中边缘数据线25与连接端口之间的边缘连接线27包括连接的第二连接线段272和第三连接线段273。本技术实施例的阵列基板中边缘数据线与连接端口之间的边缘连接线27包括连接的第二连接线段272和第三连接线段273以及连接的第一连接线段271和第三连接线段273。图9中的横坐标为连接线段编号,即为边缘数据线25与连接端口之间的边缘连接线27的编号,图8的阵列基板中每对连接的第二连接线段和第三连接线段对应一个编号,本技术实施例的阵列基板中每对连接的第二连接线段和第三连接线段对应一个编号,每对连接的第一连接线段和第三连接线段对应一个编号。图9的纵坐标为电容,沿纵轴箭头方向,电容增大。如图9所示,图8的阵列基板中边缘数据线25与连接端口之间的边缘连接线27的长度逐渐增大,导致部分不同的边缘数据线25与连接端口之间的边缘连接线27的电容的差距较大,而本技术实施例的阵列基板中边缘数据线25与连接端口之间的边缘连接线27的长度有增大,也有减小,使得不同的边缘数据线25与连接端口之间的边缘连接线27的长度的差距较小。且如图9所示,本技术实施例的阵列基板中边缘数据线25与连接端口之间的边缘连接线27的最大电容要远远小于图8的阵列基板中边缘数据线25与连接端口之间的边缘连接线27的最大电容,因此,包括本技术实施例中的阵列基板的显示装置,不仅能够实现显示装置的更窄边框,还能够尽量减小同的边缘数据线25与连接端口之间的边缘连接线27的电容的差距,以保证显示效果良好甚至优秀。

71.在一些实施例中,为了尽量减小边缘数据线25与连接端口之间的边缘连接线27的最大电容,可对距离中心区域最远的边缘数据线所连接的边缘连接线进行设置。如图2、图4和图6所示,边缘连接线27还可包括第一目标连接线段281和第二目标连接线段282。第一目标连接线段281可以为与第一连接线段271不同的连接线段,第一目标连接线段281也可复用为某一条第一连接线段271,在此并不限定。

72.第一目标连接线段281与距离中心区域211最远的边缘数据线25连接,且第一目标连接线段281至少部分沿第一方向延伸。第一目标连接线段281可为直线型、折线型或其他具有弯折的连接线段。具体地,第一目标连接线281与距离中心区域211最远的边缘数据线25和驱动集成电路的连接端口最近的一端连接。第二目标连接线段282沿第二方向延伸,第二目标连接线段282与第一目标连接线段281连接。第一目标连接线段281通过第二目标连接线段282与驱动集成电路的连接端口电连接。第二目标连接线段282可直接与驱动集成电路的连接端口电连接,也可通过其他结构与驱动集成电路的连接端口电连接。即,距离中心区域211最远的边缘数据线25可通过第一目标连接线段281、第二目标连接线段282与驱动集成电路的连接端口电连接。

73.与第一连接线段271连接的第三连接线段273和与第二连接线段272连接的第三连接线段273,位于第二目标连接线段282远离边缘区域212的一侧。

74.例如,如图3所示,连接线段a8为第一目标连接线段281,连接线段c8为第二目标连接线段282。图3中位于连接线段a8上方的连接线段a1至连接线段a7包括第一连接线段271

和第二连接线段272。图3中连接线段c8的右侧即为第二目标连接线段282远离边缘区域212的一侧,连接线段c1至c7在图3中位于连接线段c8的右侧,连接线段c1至连接线段c7为第三连接线段273。

75.又例如,如图5所示,连接线段a19为第一目标连接线段281,连接线段c19为第二目标连接线段282。图5中位于连接线段a19上方的连接线段a12至连接线段a18包括第一连接线段271和第二连接线段272。图5中连接线段c19的右侧即为第二目标连接线段282远离边缘区域212的一侧,连接线段c12至c18在图5中位于连接线段c19的右侧,连接线段c12至连接线段c18为第三连接线段273。

76.按照普通布线方式,例如图8所示的布线方式,距离中心区域211最远的边缘数据线25与驱动集成电路的连接端口之间的边缘连接线27的长度会非常大,即距离中心区域211最远的边缘数据线25与驱动集成电路的连接端口之间的边缘连接线27的电容会非常大,为了降低距离中心区域211最远的边缘数据线25与驱动集成电路的连接端口之间的边缘连接线27的电容,设置第一目标连接线段281与距离中心区域211最远的边缘数据线25的和驱动集成电路的连接端口最近的一端连接,使第一目标连接线段281与驱动集成电路的连接端口之间的距离尽可能小,减小第一目标连接线段281的长度。又由于沿从边缘区域212指向中心区域211的方向,沿第二方向延伸的连接线段的长度逐渐增大,沿第二方向延伸的连接线段包括第三连接线段273和第二目标连接线段282,第一目标连接线段281与驱动集成电路的连接端口之间的距离尽可能小,还可使第二目标连接线段282的长度尽可能小,从而使距离中心区域211最远的边缘数据线25与驱动集成电路的连接端口之间的边缘连接线27的电容尽可能小。在距离中心区域211最远的边缘数据线25与驱动集成电路的连接端口之间的边缘连接线27的电容尽可能小的基础上,长度比第二目标连接线段282更长的第三连接线段273所连接的第一连接线段、第二连接线段交杂分布,能够尽量减小其他边缘连接线27的长度,即减小其他边缘连接线27的电容,进一步提高显示效果。

77.在一些实施例中,如图2、图4和图6所示,上述实施例中的边缘连接线27还可包括第四连接线段291和第五连接线段292。第四连接线段291与边缘数据线25连接,且第四连接线段291至少部分沿第一方向延伸。第四连接线段291可为直线型、折线型或其他具有弯折的连接线段。第五连接线段292沿第二方向延伸。第五连接线段292位于第二目标连接线段282靠近边缘区域的一侧。一条第五连接线段292的部分位于显示区21,部分位于非显示区22。第五连接线段292与第四连接线段291连接。第五连接线段292可直接与驱动集成电路的连接端口电连接,也可通过其他结构与驱动集成电路的连接端口电连接。第四连接线段291通过第五连接线段292与驱动集成电路的连接端口电连接。即部分边缘数据线25通过第四连接线段291和第五连接线段292与驱动集成电路的连接端口电连接。

78.在一些示例中,第四连接线段291的数量为p。p条第四连接线段291与距离中心区域211最近的p条边缘数据线25连接,p为正整数。沿第二方向,p条第四连接线段291连接的边缘数据线25距离中心区域211的远近变化在此并不限定,p条第四连接线段291连接的边缘数据线25距离中心区域211可越来越远,也可越来越近,也可没有特定规律。

79.例如,如图3所示,第一目标连接线段281为连接线段a8,第二目标连接线段282为连接线段c8。图3中连接线段c8的左侧为第二目标连接线段282靠近边缘区域212的一侧。第四连接线段291包括连接线段a9、连接线段a10和连接线段a11,第五连接线段292包括连接

线段c9、连接线段c10和连接线段c11。图3示出了三条第四连接线段291,连接线段a9、连接线段a10和连接线段a11各自与图3中距离中心区域211最接近的边缘数据线b9、边缘数据线b10和边缘数据线b11连接。

80.又例如,如图7所示,第一目标连接线段281为连接线段a19,第二目标连接线段282为连接线段c19。图7中连接线段c19的左侧为第二目标连接线段282靠近边缘区域212的一侧。第四连接线段291包括连接线段a20、连接线段a21和连接线段a22,第五连接线段292包括连接线段c20、连接线段c21和连接线段c22。图7示出了三条第四连接线段291,连接线段a20、连接线段a21和连接线段a22各自与图7中距离中心区域211最接近的边缘数据线b20、边缘数据线b21和边缘数据线b22连接。

81.在一些实施例中,至少一条第三连接线段273在显示区21的部分可位于相邻的两条中心数据线24之间,第二目标连接线段282在显示区21的部分可位于相邻的两条中心数据线24之间,至少一条第五连接线段292在显示区21的部分可位于相邻的两条中心数据线24之间,以更加充分地利用阵列基板的空间。

82.在一些实施例中,阵列基板还可包括像素电路列和虚拟像素电路列。像素电路列包括像素电路,像素电路列中的像素电路可与像素连接,以驱动像素发光。在一些示例中,虚拟像素电路列可包括像素电路,虚拟像素电路列中的至少部分像素电路不与像素连接。在另一些示例中,虚拟像素电路列也可不包括像素电路。

83.一组虚拟像素电路列位于两组像素电路列之间。一组虚拟像素电路列包括至少一个虚拟像素电路列。一组像素电路列包括至少一个像素电路列。至少部分第三连接线段273的正投影与虚拟像素电路列的正投影交叠,即至少部分第三连接线段273可位于虚拟像素电路列占据的空间内。这里的正投影为沿阵列基板的厚度方向的投影。像素电路列中的像素电路的尺寸可设置地尽可能小,使得在保证像素密度不变的情况下,留出虚拟像素电路列的位置,来设置第三连接线段273。

84.在一些示例中,上述实施例中的第二目标连接线段282的正投影可与虚拟像素电路列的正投影交叠。

85.在一些示例中,上述实施例中的第五连接线段292的正投影可与虚拟像素电路列的正投影交叠。

86.在一些示例中,沿第一方向,像素电路列和虚拟像素电路列可按照q:1的比例交替排列,即yq个像素电路列与y个虚拟像素电路列交替排列,y为正整数。

87.例如,图10为本技术实施例提供的部分第三连接线段设置位置的一示例的示意图。如图10所示,一组虚拟像素电路列包括一个虚拟像素电路列31,一组像素电路列包括四个像素电路列32。四个像素电路列32和一个虚拟像素电路列31交替排列,即像素电路列32和虚拟像素电路列31按照4:1的比例交替排列。第三连接线段273位于虚拟像素电路列31的空间内。

88.在一些实施例中,阵列基板还包括像素列,像素列包括像素。虚拟像素电路列和像素电路列的正投影位于像素列所在的区域的正投影之内。在同一区域内,像素列的数量小于电路列数量和。电路列数量和为像素电路列的数量与虚拟像素电路列的数量之和。像素电路列可驱动像素列。例如,在同一区域内,虚拟像素电路列的数量为1,像素电路列的数量为4,则电路列数量和为5,像素列的数量为4,4个像素电路列可分别驱动4个像素列。

89.边缘数据线25通过边缘连接线27与驱动集成电路的连接端口电连接。由于边缘连接线27包括沿第一方向延伸的连接线段和沿第二方向延伸的连接线段,即边缘连接线27具有弯折,导致边缘连接线27到达驱动集成电路的连接端口时的排列顺序已经发生改变。

90.在一些实施例中,可按照预先设置的边缘连接线27、中心连接线26到达驱动集成电路的连接端口的排列顺序,对驱动集成电路的连接端口进行配置,使驱动集成电路的连接端口的排列顺序与边缘连接线27、中心连接线26到达驱动集成电路的连接端口的排列顺序一致。

91.在一些实施例中,可通过换线连接单元将边缘连接线27与驱动集成电路的连接端口正确的电连接,即将边缘连接线27的顺序梳理为与驱动集成电路的连接端口的排列顺序一致的顺序,不需要更改原有的连接端口的边缘连接线27、中心连接线26到达驱动集成电路的连接端口的排列顺序。对应地,本技术实施例中的阵列基板还可包括换线连接单元。换线连接单元与边缘连接线27、驱动集成电路的连接端口电连接,用于使边缘数据线25通过边缘连接线27和换线连接单元,按照边缘数据线25的排列顺序与对应顺序的连接端口电连接。

92.换线连接单元可位于非显示区22。在一些示例中,换线连接单元可位于上述实施例中的功能区域23。图11为本技术实施例中功能区域的一示例的示意图。图11仅作示意,阵列基板中中心连接线、边缘连接线的数量要远远大于图11示出的数量。如图11所示,功能区域23包括换线连接单元33和驱动集成电路的连接端口。换线连接单元33可包括换线连接线331。换线连接线331的一端与边缘连接线27一一对应电连接,另一端与边缘连接线27连接的边缘数据线25对应顺序的连接端口电连接。换线连接线331的分布与边缘数据线25、第一连接线段271、第二连接线段272、第三连接线段273、第一目标连接线段281、第二目标连接线段282、第四连接线段291和第五连接线段292的排布相关。

93.设图11中边缘连接线27的排列、连接与图3中的边缘连接线27一致。图11中的连接线段e1至e6为中心连接线26。连接端口a1至a11依次与图3中的边缘数据线b1至边缘数据线b11对应。边缘数据线b1至边缘数据线b11各自对应的连接线段分别为依次为连接线段c8、连接线段c6、连接线段c4、连接线段c2、连接线段c1、连接线段c3、连接线段c5、连接线段c7、连接线段c9、连接线段c10、连接线段c11。对应的,换线连接线331与连接线段c8、连接线段c6、连接线段c4、连接线段c2、连接线段c1、连接线段c3、连接线段c5、连接线段c7、连接线段c9、连接线段c10、连接线段c11的连接如图11所示。

94.在一些实施例中,边缘连接线27可与边缘数据线25同层设置,即边缘连接线27与边缘数据线25可位于同一金属层。例如,以阵列基板为常规柔性阵列基板为例,阵列基板可包括第一金属层m1、第二金属层m2、第三金属层m3和第四金属层m4。第一金属层m1、第二金属层m2、第三金属层m3和第四金属层m4常作为信号线金属层使用。在一些示例中,中心数据线24和边缘数据线25可位于第三金属层m3和/或第四金属层m4,对应地,边缘连接线27也可位于第三金属层m3和/或第四金属层m4。

95.在另一些实施例中,边缘连接线27与边缘数据线25非同层设置。边缘连接线27位于目标金属层,目标金属层可位于基底与有源层之间。具体可在阵列基板中增加一金属层即目标金属层来实现边缘连接线27。包括中心数据线24和边缘数据线25的金属层可位于有源层与阳极金属层之间。边缘连接线27与边缘数据线25非同层设置,使得边缘连接线27在

显示区21的布线更为自由灵活。在边缘连接线27与边缘数据线25非同层设置的情况下,边缘连接线27与边缘数据线25可通过通孔电连接。

96.本技术还提供一种显示面板。该显示面板可包括上述实施例中的阵列基板,其技术效果与阵列基板相同,可参见上述实施例中的相关说明,在此不再赘述。

97.本技术还提供一种显示装置。该显示装置包括上述实施例中的显示面板。显示装置具体可为手机、计算机、平板电脑、电视、电子纸等具有显示功能的装置,在此并不限定。本技术实施例中的显示装置可为采用cop封装方式、cof封装方式或cog封装方式的显示装置,在此并不限定。

98.在一些示例中,显示装置采用cog封装方式。图12为本技术实施例中显示装置的一示例的侧截面的示意图。如图12所示,显示装置具有显示区41和非显示区42。非显示区42包括功能区域43。驱动集成电路34位于功能区域43。图12中显示区41与功能区域43之间的距离l1与图2、图4和图6中所示的距离d3基本相同。阵列基板的显示区21与功能区域23之间的距离d3能够进一步缩短,对应地,显示装置的显示区41与功能区域43之间的距离l1能够进一步缩短,从而能够进一步压缩显示装置的边框宽度,能够实现显示装置的更窄边框。

99.在另一些示例中,显示装置采用cof封装方式。图13为本技术实施例中显示装置的另一示例的侧截面的示意图。如图13所示,显示装置具有显示区41和非显示区42。非显示区42包括功能区域43。功能区域43具体可包括上述实施例中的弯折区域。驱动集成电路34位于弯折至阵列基板背面的排线上。图13中显示区41与功能区域43之间的距离l1与图2、图4和图6中所示的距离d3基本相同。阵列基板的显示区21与功能区域23之间的距离d3能够进一步缩短,对应地,显示装置的显示区41与功能区域43之间的距离l1能够进一步缩短,从而能够进一步压缩显示装置的边框宽度,能够实现显示装置的更窄边框。

100.在又一些示例中,显示装置采用cop封装方式。图14为本技术实施例中显示装置的又一示例的侧截面的示意图。如图14所示,显示装置具有显示区41和非显示区42。非显示区42包括功能区域43。功能区域43具体可包括上述实施例中的弯折区域。阵列基板为柔性阵列基板,可弯折至背面,驱动集成电路34位于弯折至背面的柔性阵列基板上。图14中显示区41与功能区域43之间的距离l1与图2、图4和图6中所示的距离d3基本相同。阵列基板的显示区21与功能区域23之间的距离d3能够进一步缩短,对应地,显示装置的显示区41与功能区域43之间的距离l1能够进一步缩短,从而能够进一步压缩显示装置的边框宽度,能够实现显示装置的更窄边框。

101.需要明确的是,本说明书中的各个实施例均采用递进的方式描述,各个实施例之间相同或相似的部分互相参见即可,每个实施例重点说明的都是与其他实施例的不同之处。对于显示面板实施例和显示装置实施例而言,相关之处可以参见阵列基板实施例的说明部分。本技术并不局限于上文所描述并在图中示出的特定步骤和结构。本领域的技术人员可以在领会本发明的精神之后,作出各种改变、修改和添加,或者改变步骤之间的顺序。并且,为了简明起见,这里省略对已知方法技术的详细描述。

102.本领域技术人员应能理解,上述实施例均是示例性而非限制性的。在不同实施例中出现的不同技术特征可以进行组合,以取得有益效果。本领域技术人员在研究附图、说明书及权利要求书的基础上,应能理解并实现所揭示的实施例的其他变化的实施例。在权利要求书中,术语“包括”并不排除其他装置或步骤;不定冠词“一个”不排除多个;术语“第

一”、“第二”用于标示名称而非用于表示任何特定的顺序。权利要求中的任何附图标记均不应被理解为对保护范围的限制。权利要求中出现的多个部分的功能可以由一个单独的硬件或软件模块来实现。某些技术特征出现在不同的从属权利要求中并不意味着不能将这些技术特征进行组合以取得有益效果。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1