多芯片封装结构的制作方法

1.本实用新型涉及mems器件封装,具体涉及一种具有asic芯片、陀螺仪芯片和加速度计芯片的多芯片封装结构。

背景技术:

2.六轴mems惯性传感器通常包括asic(application specific integrated circuit,专用集成电路)芯片、陀螺仪芯片和加速度计芯片,其中asic芯片所占的平面面积一般都会大于陀螺仪芯片和加速度计芯片,在将三者进行多芯片封装时,会采用将asic芯片置于底部,并将陀螺仪芯片和加速度计芯片分别层叠在asic芯片的上方。

3.在采用上述多芯片封装结构的产品中,广泛存在asic芯片的面积不足以使在其上方的陀螺仪芯片和加速度计芯片,均能够被布置在asic芯片的平面面积范围内,即从平面布局上陀螺仪芯片和加速度计芯片至少有一个会延伸到asic芯片外,从而在现有产品中,针对陀螺仪芯片和加速度计芯片在asic芯片上的布局方式多种多样。针对因不同布局而导致的,在smt(surface mounted technology)贴片后某些测试结果超规范,如单轴测试数据偏移等,原因尚不明确。因此本领域技术人员所致力于改进或规范化上述多芯片封装结构的布局,以尽可能减少甚至消除因布局引起的器件失效。

技术实现要素:

4.有鉴于上述技术问题,本实用新型提供了一种多芯片封装结构,包括asic芯片、陀螺仪芯片和加速度计芯片,所述陀螺仪芯片和所述加速度计芯片分别层叠地设置在所述asic芯片上方,所述asic芯片的面积不足以使其能够同时包所述陀螺仪芯片和所述加速度计芯片;所述asic芯片包所述加速度计芯片;所述陀螺仪芯片与所述asic芯片间设置有间隔层。

5.进一步地,所述间隔层采用晶圆片。

6.进一步地,所述加速度计芯片一侧边缘与所述asic芯片一侧边缘重合。

7.进一步地,所述陀螺仪芯片的第一侧边缘延伸到所述asic芯片外,所述间隔层的第一侧边缘也延伸到所述asic芯片外,从而使延伸出的部分陀螺仪芯片得以通过所述间隔层提供支撑。

8.进一步地,所述陀螺仪芯片的第一侧边缘与所述间隔层的第一侧边缘重合。

9.进一步地,所述陀螺仪芯片的第二侧边缘延伸到所述间隔层外形成悬空部分,所述asic芯片的部分引脚设置在所述悬空部分的下方。

10.进一步地,所述陀螺仪芯片和所述间隔层的交叠面积不小于所述陀螺仪芯片面积的75%。

11.进一步地,所述间隔层和所述陀螺仪芯片的交叠面积不小于所述间隔层面积的95%。

12.进一步地,所述陀螺仪芯片包所述间隔层。

13.进一步地,所述加速度计芯片的引脚与所述陀螺仪芯片的引脚同向对齐排布。

14.本实用新型的多芯片封装结构在能够保证封装工艺正常实施的前提下,对于现有芯片在smt贴片后会发生器件失效的情况,针对多芯片的布局进行设置和规范化,从而可有效地改善和减少上述的smt贴片后的器件失效。

15.以下将结合附图对本实用新型的构思、具体结构及产生的技术效果作进一步说明,以充分地了解本实用新型的目的、特征和效果。

附图说明

16.图1是本实用新型中用于解释“图形a包图形b”的结构示意图;

17.图2是本实用新型中用于解释“图形a与图形b交叠”的结构示意图;

18.图3是本实用新型中用于解释“图形a延伸到图形b外”的结构示意图;

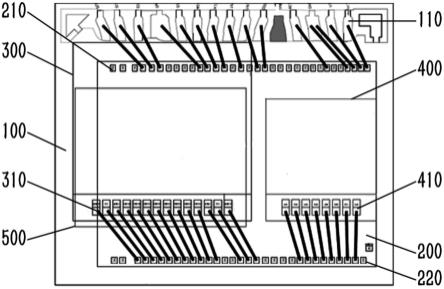

19.图4是本实用新型的一个实施例的多芯片封装结构的顶视角的结构示意图;

20.图5是图4中的多芯片封装结构的侧视角的结构示意图;

21.图6是一种现有的多芯片封装结构的顶视角的结构示意图;

22.图7是分别采用图4和图6中的多芯片封装结构的惯性传感器在smt贴片前后加速度计各轴的测试数据图表。

23.附图标记说明:

24.100—封装基座,

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

110—引脚,

25.200—asic芯片200,

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

210、220—引脚,

26.300—陀螺仪芯片,

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

310—引脚,

27.400—加速度计芯片,

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

410—引脚,

28.500—间隔层。

具体实施方式

29.在本实用新型的实施方式的描述中,需要理解的是,术语“上”、“下”、“前”、“后”、“左”、“右”、“垂直”、“水平”、“顶”、“底”、“内”、“外”、“顺时针”、“逆时针”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本实用新型和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对实用新型的限制。附图为原理图或者概念图,各部分厚度与宽度之间的关系,以及各部分之间的比例关系等等,与其实际值并非完全一致。

30.以下首先对于本实用新型中各芯片间布局关系所使用的术语进行说明,布局的位置关系视图是基于顶视角(topview),显示各芯片在封装结构底面所在平面上的正投影图形。

31.1、图形a包图形b,如图1所示,图形b位于图形a的范围内,也可称为图形b被图形a包;

32.2、图形a与图形b交叠,如图2所示,图形a与图形b具有相互重叠的部分;

33.3、图形a延伸到图形b外,如图3所示,图形a与图形b交叠时,图形a位于图形b某一侧外未交叠的部分。

34.图4和图5示出了本实用新型的一个实施例的多芯片封装结构的结构示意图,其中

包括封装基座100、asic芯片200、陀螺仪芯片300、加速度计芯片400和间隔层500。

35.asic芯片200固定设置于封装基座100上,两者可通过粘合层相连接,如使用环氧树脂、有机硅树脂、聚酰亚胺树脂、酚醛树脂、聚氨酯、丙烯酸树脂等作为胶黏剂,两者的粘合非本实用新型的重点,可使用现有工艺实现,在此不做赘述。

36.陀螺仪芯片300、加速度计芯片400和间隔层500的面积均小于asic芯片200的面积。陀螺仪芯片300、加速度计芯片400和间隔层500中,陀螺仪芯片300的面积最大,其次是间隔层500,加速度计芯片400的面积最小。

37.间隔层500被固定设置在asic芯片200上方,如将两者通过粘合层相连接。在平面布局上,间隔层500的一侧延伸到asic芯片200外,即图4视角中的间隔层500的左侧延伸到asic芯片200的左侧外。在本实施例中,间隔层500采用晶圆片。

38.加速度计芯片400被固定设置在asic芯片200上方,如将两者通过粘合层相连接。在平面布局上,asic芯片200包加速度计芯片400,本实施例中,加速度计芯片400的一侧与asic芯片200的一侧相重合,即图4视角中的加速度计芯片400的右侧与asic芯片200的右侧相重合。在另一些实施例中,加速度计芯片400的右侧与asic芯片200的右侧设置有一间距。

39.陀螺仪芯片300被固定设置在间隔层500上方,如将两者通过粘合层相连接。在平面布局上,陀螺仪芯片300有两侧延伸到asic芯片200外,即图4视角中的陀螺仪芯片300的左侧延伸到asic芯片200的左侧外,陀螺仪芯片300的上侧延伸到asic芯片200的上侧外。

40.本实施例中,陀螺仪芯片300与间隔层500交叠,间隔层500的一侧延伸到陀螺仪芯片300外,即图4视角中的间隔层500的下侧延伸到陀螺仪芯片300的下侧外;并且陀螺仪芯片300与间隔层500有一侧相重合,即图4视角中的陀螺仪芯片300的左侧与间隔层500的左侧相重合,从而延伸出的间隔层500会向延伸出的陀螺仪芯片300提供支撑。在另一些实施例中,也可将图4中间隔层500的左侧和/或右侧延伸到陀螺仪芯片300外。当陀螺仪芯片300与间隔层500具有如上各种情况的交叠时,优选地,陀螺仪芯片300和间隔层500的交叠面积不小于陀螺仪芯片300面积的75%,间隔层500和陀螺仪芯片300的交叠面积不小于间隔层500面积的95%。

41.在另一些实施例中,陀螺仪芯片300包间隔层500,在另一个具体的实施例中,陀螺仪芯片300与间隔层500分别有两侧相重合,如图4视角中可设置陀螺仪芯片300的左侧与间隔层500的左侧相重合,陀螺仪芯片300的下侧与间隔层500的下侧相重合。当陀螺仪芯片300包间隔层500时,优先地,间隔层500的面积不小于陀螺仪芯片300面积的75%。

42.本实施例中,asic芯片200相对的两侧边缘设置有若干引脚,即图4视角中位于asic芯片200的上侧边缘的一排引脚210和位于asic芯片200的下侧边缘的一排引脚220,asic芯片200的引脚210用于与封装基座100上的引脚110电连接,asic芯片200的引脚220用于与陀螺仪芯片300的引脚310和加速度计芯片400的引脚410电连接。陀螺仪芯片300和加速度计芯片400的布置方向使引脚310和引脚410所在侧靠近asic芯片200的下侧。为便于封装工艺中引线的连接,使陀螺仪芯片300的引脚310与加速度计芯片400的引脚410同向对齐排布,从而使得陀螺仪芯片300与加速度计芯片400的引脚排列与asic芯片200的引脚220排列相平行,同时陀螺仪芯片300与加速度计芯片400的引脚排列至asic芯片200的引脚220排列的间距,与asic芯片200的引脚210排列至封装基座100上的引脚110排列的间距大致相等。

43.鉴于以上对于陀螺仪芯片300的引脚布局中的位置要求以及陀螺仪芯片300的面积大小,陀螺仪芯片300的上侧不得不延伸到asic芯片200上侧外,从平面布局来看,asic芯片200上侧的部分引脚会被陀螺仪芯片300所覆盖,而间隔层500由于是与asic芯片200直接粘合,其被设置为不会覆盖到asic芯片200上的任何引脚,从而在空间布局上,部分陀螺仪芯片300是悬空地设置在asic芯片200上侧部分引脚的正上方,两者的间距是由间隔层500及其上下粘合层的总厚度所限定,该厚度可以通过选择间隔层500的厚度来进行调整,以使上述的asic芯片200上侧部分引脚与陀螺仪芯片300有足够的间距,从而适于工艺实施asic芯片200上侧的引脚与封装基座100上的引脚的引线连接。

44.在一个验证本实施例技术效果的方案对比中,将图4中的陀螺仪芯片300、加速度计芯片400和间隔层500整体向右移动,从而使得陀螺仪芯片300和间隔层500的左侧延伸到asic芯片200左侧外的距离大幅减小,相应地,加速度计芯片400的右侧延伸到asic芯片200右侧外,如图6所示,这一布局是六轴mems惯性传感器中被广泛采用的一种布局结构。图7的图表中示出了图4和图6布局结构的惯性传感器在smt贴片前后的加速度计测试结果对比(每项测试采样100颗芯片),从图表中数据可见,在smt贴片前,图4和图6两种布局结构的惯性传感器中的加速度计各轴的测试数据变化不大,而在smt贴片后进行的加速度计各轴的测试数据却出现了较大的变化,采用图6布局结构的惯性传感器中的加速度计的x轴测试的最小值和y轴测试的最大值均超出了的0

±

200mg的规范限,造成该批次芯片失效,而采用图4布局结构的惯性传感器中的加速度计各轴的测试数据虽然也发生了一定的起伏变化,但整体的测试结果均在规范限内,该批次芯片合格。

45.本实施例的多芯片封装结构在能够保证封装工艺正常实施的前提下,对于现有芯片在smt贴片后会发生器件失效的情况,针对多芯片的布局进行设置和规范化,从而可有效地改善和减少上述的smt贴片后的器件失效。

46.以上详细描述了本实用新型的较佳具体实施例。应当理解,本领域的普通技术人员无需创造性劳动就可以根据本实用新型的构思作出诸多修改和变化。因此,凡本技术领域中技术人员依本实用新型的构思在现有技术的基础上通过逻辑分析、推理或者有限的实验可以得到的技术方案,皆应在由权利要求书所确定的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1