芯片测试方法、装置、处理器芯片及服务器与流程

[0001]

本发明涉及芯片自动测试技术领域,尤其涉及一种芯片测试方法、装置、处理器芯片及服务器。

背景技术:

[0002]

在超大规模数字集成电路设计中,尤其是soc(system on chip,系统级芯片),因其功能复杂,性能完整,整个芯片设计一般分为不同的ip(intellectual property,知识产权)模块,ip模块一般指某个具有知识产权的设计模块。总的设计流程是先完成单个ip模块的设计与验证,然后整合成一个大的芯片。在芯片级测试中,模块之间,模块与外部之间,目前使用最多的是基于jtag(joint test action group,联合测试工作组)协议的通讯及其扩展。因此,在ate(automatic test equipment,自动测试设备)测试向量中,设计工程师和dft(design for test,用于芯片测试而设计的电路)工程师通常需要提供基于jtag指令的ate测试向量,将该ate测试向量交给ate测试工程师用来进行ate测试。而一个完整的jtag tap(test access port,测试访问端口)由16位状态机组成,所有的测试指令都是围绕jtag tap的状态机运行。通常来说,一个大的芯片设计,会有不同的设计部门,甚至不同的公司合作开发完成,有的是soft macro(软巨集,指集成电路设计中指某个模块的rtl行为级代码,不包含实例化,综合布线的模块统称),有的是hard macro(硬巨集,指已经实现实例化,综合布线,时序分析的现成模块,可以直接集成到芯片使用)。不同ip模块设计来源,造成设计文件的多样化及复杂化。有的ip模块使用第三方eda工具直接产生ate向量stil(standard test interface language,标准测试接口语言)文件,有的ip模块只能提供verilog源代码代替ate向量,而有的ip模块只有仿真文件,还有的ip模块只有jtag指令以测试规格的方式提供。其输出向量文件格式各式各样,如此,在ate测试阶段,ate测试工程师,需要花费较多时间成本去熟悉不同的设计语言,处理不同的测试向量文件,延长了芯片的测试周期。

技术实现要素:

[0003]

有鉴于此,本发明实施例提供一种芯片测试方法、装置、处理器芯片及服务器,可有效缩短芯片测试周期。

[0004]

本发明一个或多个实施例提供了一种芯片测试方法,包括:获取自动测试设备ate向量的源文件,其中,所述源文件包括以预设编译语言创建的文本文件;根据所述源文件生成目标芯片的ate向量;根据所述ate向量对所述目标芯片进行ate上机测试。

[0005]

可选的,所述方法还包括:在获取ate向量的源文件之前,以预设编译语言创建所述源文件;根据所述源文件生成仿真文件;根据所述仿真文件进行仿真,得到仿真结果;响应于所述仿真结果满足预设条件,确定所述源文件通过仿真测试;响应于所述仿真结果不满足所述预设条件,重新以所述预设编译语言创建ate向量的源文件。

[0006]

可选的,根据源文件生成目标芯片的ate向量,包括:获取目标测试参数;根据所述目标测试参数对所述源文件进行修改,得到修改后的源文件;将修改后的源文件输入所述

预设编译器,得到所述预设编译器输出的所述ate向量。

[0007]

可选的,所述预设编译语言中包括以下至少一种类型的变量:jtag管脚、ate向量产生联合测试工作组jtag时钟周期数、ate向量标准测试接口语言stil头文件、ate向量stil尾文件以及仿真断点。可选的,所述预设编译语言中定义了ate测试流程中各种命令对应的关键字。

[0008]

可选的,所述方法还包括:在根据所述ate向量对所述目标芯片进行自动测试设备ate上机测试之后,响应于ate上机测试未通过,重新以所述预设编译语言创建ate向量的源文件。

[0009]

本发明一个或多个实施例还提供了一种芯片测试装置,包括:获取模块,被配置为获取自动测试设备ate向量的源文件,其中,所述源文件包括以预设编译语言创建的文本文件;第一生成模块,被配置为根据所述源文件生成目标芯片的ate向量;测试模块,被配置为根据所述ate向量对所述目标芯片进行ate上机测试。

[0010]

可选的,所述装置还包括:创建模块,被配置为在获取ate向量的源文件之前,以预设编译语言创建所述源文件;第二生成模块,被配置为根据所述源文件生成仿真文件;仿真模块,被配置为根据所述仿真文件进行仿真,得到仿真结果;确定模块,被配置为响应于所述仿真结果满足预设条件,确定所述源文件通过仿真测试;第二创建模块,被配置为响应于所述仿真结果不满足所述预设条件,重新以所述预设编译语言创建ate向量的源文件。

[0011]

可选的,所述第一生成模块具体被配置为:获取目标测试参数;根据所述目标测试参数对所述源文件进行修改,得到修改后的源文件;将修改后的源文件输入所述预设编译器,得到所述预设编译器输出的所述ate向量。

[0012]

可选的,所述预设编译语言中包括以下至少一种类型的变量:jtag管脚、ate向量产生联合测试工作组jtag时钟周期数、ate向量标准测试接口语言stil头文件、ate向量stil尾文件以及仿真断点。

[0013]

可选的,所述预设编译语言中定义了ate测试流程中各种命令对应的关键字。

[0014]

可选的,所述装置还包括:第三创建模块,被配置为在根据所述ate向量对所述目标芯片进行自动测试设备ate上机测试之后,响应于ate上机测试未通过,重新以所述预设编译语言创建ate向量的源文件。

[0015]

本发明一个或多个实施例还提供了一种处理器芯片,包括:至少一个处理器核心、缓存;所述处理器核心,用于执行上述任意一种芯片测试方法。

[0016]

本发明一个或多个实施例还提供了一种服务器,包括:壳体、处理器、存储器、电路板和电源电路,其中,电路板安置在壳体围成的空间内部,处理器和存储器设置在电路板上;电源电路,用于为上述电子设备的各个电路或器件供电;存储器用于存储可执行程序代码;所述处理器通过读取存储器中存储的可执行程序代码来运行与可执行程序代码对应的程序,用于执行上述任意一种芯片测试方法。

[0017]

本发明一个或多个实施例的芯片测试方法,在对芯片进行ate测试时,获取到的是ate向量的源文件,而并非ate向量本身,这样根据实际测试需求,可对该源文件进行调整,以基于调整后的源文件生成ate测试向量,从而完成ate测试,即使ate测试未通过,也仅需重新创建ate测试向量的源文件,可有效缩短芯片测试周期。

附图说明

[0018]

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图。

[0019]

图1示出一种芯片测试方法的流程图;

[0020]

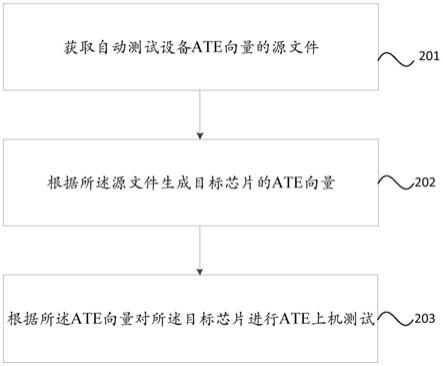

图2是根据本发明一个或多个实施例示出的一种芯片测试方法的流程图;

[0021]

图3是根据本发明一个或多个实施例示出的一种芯片测试方法的流程图;

[0022]

图4是根据本发明一个或多个实施例示出的一种芯片测试装置的框图;

[0023]

图5是根据本发明一个或多个实施例示出的一种芯片的结构示意图;

[0024]

图6是根据本发明一个或多个实施例示出的一种服务器的结构示意图。

具体实施方式

[0025]

下面结合附图对本发明实施例进行详细描述。

[0026]

应当明确,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其它实施例,都属于本发明保护的范围。

[0027]

图1示出一种芯片测试方法,如图1所示,当在基于ate向量对芯片进行ate上机测试失败时,需要重新创建ate向量,然后经过仿真,以及经过测试工程师基于该ate向量得到ate可以使用的stil向量文件。在该过程中,负责生成ate向量的设计工程师和负责ate测试的测试工程师只能串行工作,且工作条件前后依赖性很强,对于压缩产品周期不利。同时,由于设计仿真环境和ate测试环境差异较大,可能会导致在设计仿真环境下测试通过但ate测试失败的情况发生。且在ate测试过程中,测试工程师每次修改ate向量,都需要前端设计工程师的介入,而修改ate向量是测试工程师在ate测试过程中经常需要进行的操作,显然这样较为耗费人力。且因芯片的不同ip模块提供的文件格式不统一,测试工程师需要特别对每一种格式进行处理,难度非常大,且每个测试工程师的偏好不同,会导致向量输出不统一,导致测试效率低下。此外,向量导入周期长,也延迟了芯片产品的上线周期。

[0028]

本发明一个或多个实施例提供了一种芯片测试方法,图2是根据本发明一个或多个实施例的一种芯片测试方法的流程图,如图2所示,该方法包括:

[0029]

步骤201:获取ate向量的源文件,其中,所述源文件包括以预设编译语言创建的文本文件;

[0030]

其中,ate向量的源文件例如可以是一个可任意被修改的源文件。该源文件以文本文件形式存在,使其可读性较高,降低了对该源文件的修改难度。

[0031]

其中,预设编译语言例如可以是一种可读性较强、抽象程度较高的高级编译语言,该语言可支持现有的常用jtag指令读写,tap 16位状态机的仿真,以及芯片管脚的状态控制以及时序控制等。也支持输出ate测试向量文件stil和仿真文件如verilog等,也可以输出任何atpg工具需要的向量仿真输入格式。该预设编译语言可专用于ate测试,该预设编译语言中可预先定义好了各种ate测试项对应的字符,故,在创建测试向量的源文件时,可直接使用这些已被定义好的字符来表示具体的ate测试项,而无需如一些底层编译语言一样

需要使用者在创建源文件时自行定义一些基本的变量。

[0032]

步骤202:根据所述源文件生成目标芯片的ate向量;

[0033]

例如,可根据测试需求,确定出相应的测试参数,根据测试参数对源文件进行修改,得到修改后的源文件,将修改后的源文件输入对应于预设编译语言的预设编译器,由该预设编译器输出ate向量。

[0034]

步骤203:根据所述ate向量对所述目标芯片进行自动测试设备ate上机测试。

[0035]

本发明一个或多个实施例的芯片测试方法,在对芯片进行ate测试时,获取到的是ate向量的源文件,而并非ate向量本身,这样根据实际测试需求,可对该源文件进行调整,以基于调整后的源文件生成ate测试向量,从而完成ate测试,即使ate测试未通过,也仅需重新创建ate测试向量的源文件,可有效缩短芯片测试周期。

[0036]

在本发明的一个或多个实施例中,上述芯片测试方法还可包括:在获取ate向量的源文件之前,以预设编译语言创建所述源文件;根据所述源文件生成仿真文件,该仿真文件例如verilog。根据所述仿真文件进行仿真,得到仿真结果;响应于所述仿真结果满足预设条件,确定所述源文件通过仿真测试;例如,可根据测试需求设定仿真结果所需满足的条件。响应于所述仿真结果不满足所述预设条件,重新以所述预设编译语言创建ate向量的源文件。在本实施例中,基于ate测试向量的源文件生成仿真文件以及生成测试向量的步骤可以同时执行,可也先后执行。

[0037]

在本发明的一个或多个实施例中,仿真文件与ate测试向量均可基于ate向量的源文件生成,保证了二者的一致性,可降低仿真环境和测试环境的差异性,可在一定程度上避免仿真结果和测试结果差异较大的问题。

[0038]

在本发明的一个或多个实施例中,根据源文件生成目标芯片的ate向量可包括:获取目标测试参数;根据所述目标测试参数对所述源文件进行修改,得到修改后的源文件;将修改后的源文件输入所述预设编译器,得到所述预设编译器输出的所述ate向量。其中,可根据测试需求确定目标测试参数,根据目标测试参数对所述源文件进行修改,例如,可利用测试参数对源文件中的变量进行赋值,再将修改后的源文件输入预设编译器,即可得到预设编译器输出的ate向量,该预设编译器例如根据修改后的源文件产生基于jtag指令的ate测试向量。

[0039]

在本发明的一个或多个实施例中,所述预设编译语言中包括以下至少一种类型的变量:

[0040]

jtag管脚、ate向量产生jtag时钟周期数、ate向量stil头文件、ate向量stil尾文件以及仿真断点。所述预设编译语言中定义了各种ate测试项对应的指令。其中,jtag管脚的变量名例如可以包括:jtag_tck、jtag_tms、jtag_tdi、jtag_trst以及jtag_tdo,这些变量可用于定义jtag管脚;ate向量产生jtag时钟周期数的变量名例如可以为cyclesperjtaginstruction,该变量可用于指定ate向量产生jtag时钟的周期数;ate向量stil头文件的变量名例如可以为stilheader,该变量可用于指定ate向量stil头文件;ate向量stil尾文件的变量名例如可以为stilfooter,该变量例如可以用于指定ate向量stil尾文件;仿真断点的变量名例如可以为cutpoints,该变量例如可以用于指定仿真断点。

[0041]

此外,预设编译语言中还可包括字母、数字等一般变量,以及还可包括用于指定必须变量的修饰字,该修饰字的变量名例如可以为required,还可包括用于指定别名的修饰

字,该修饰字的变量名例如可以为alias。

[0042]

在本发明的一个或多个实施例中,所述预设编译语言中定义了ate测试流程中各种命令对应的关键字,基于此,该预设编译语言可专用于ate测试,在创建上述源文件时,可降低创建难度,提高创建效率。

[0043]

在本发明的一个或多个实施例中,上述芯片测试方法还可包括:在根据所述ate向量对所述目标芯片进行自动测试设备ate上机测试之后,响应于ate上机测试未通过,重新以所述预设编译语言创建ate向量的源文件,可见在本实施例中,在ate上机测试不通过的情况下,仅重新创建ate向量的源文件即可,而无需重新创建ate向量,可缩短芯片测试周期。

[0044]

在本发明的一个或多个实施例中,创建仿真文件的过程可与创建ate测试向量的过程同步进行,仿真过程也可与测试过程同步进行,同时,测试过程还可在仿真通过后进行。基于此,可进一步缩短芯片测试周期,图3是根据本发明一个或多个实施例示出的一种芯片测试方法的流程图,如图3所示,该方法包括,创建ate向量指令集(为上述预设编译语言的一个示例);基于ate向量指令集创建ate向量的源文件;根据ate向量的源文件产生仿真文件以及产生向量文件stil,根据仿真文件进行仿真测试,若仿真失败,则重新生成ate向量的源文件,根据向量文件进行ate上机测试,若ate上机测试失败,则重新生成ate向量的源文件,若ate上机测试通过,流程结束。

[0045]

图4是根据本发明一个或多个实施例示出的一种芯片测试装置的结构示意图,如图4所示,该装置40包括:

[0046]

获取模块41,被配置为获取自动测试设备ate向量的源文件,其中,所述源文件包括以预设编译语言创建的文本文件;

[0047]

第一生成模块42,被配置为根据所述源文件生成目标芯片的ate向量;

[0048]

测试模块43,被配置为根据所述ate向量对所述目标芯片进行ate上机测试。

[0049]

在本发明的一个或多个实施例中,上述芯片测试装置还可包括:创建模块,被配置为在获取ate向量的源文件之前,以预设编译语言创建所述源文件;第二生成模块,被配置为根据所述源文件生成仿真文件;仿真模块,被配置为根据所述仿真文件进行仿真,得到仿真结果;确定模块,被配置为响应于所述仿真结果满足预设条件,确定所述源文件通过仿真测试;第二创建模块,被配置为响应于所述仿真结果不满足所述预设条件,重新以所述预设编译语言创建ate向量的源文件。

[0050]

在本发明的一个或多个实施例中,所述第一生成模块具体被配置为:获取目标测试参数;根据所述目标测试参数对所述源文件进行修改,得到修改后的源文件;将修改后的源文件输入所述预设编译器,得到所述预设编译器输出的所述ate向量。

[0051]

在本发明的一个或多个实施例中,所述预设编译语言中包括以下至少一种类型的变量:jtag管脚、ate向量产生联合测试工作组jtag时钟周期数、ate向量标准测试接口语言stil头文件、ate向量stil尾文件以及仿真断点。

[0052]

在本发明的一个或多个实施例中,所述预设编译语言中定义了ate测试流程中各种命令对应的关键字。

[0053]

在本发明的一个或多个实施例中,上述芯片测试装置还可包括:第三创建模块,被配置为在根据所述ate向量对所述目标芯片进行自动测试设备ate上机测试之后,响应于

ate上机测试未通过,重新以所述预设编译语言创建ate向量的源文件。

[0054]

本发明一个或多个实施例还提供了一种处理器芯片,图5是根据本发明一个或多个实施例示出的一种处理芯片的示意图,如图5所示,该处理芯片50包括:至少一个处理器核心51以及缓存52;所述处理器核心51,用于执行上述任意一种芯片测试方法。

[0055]

本发明一个或多个实施例还提供了一种服务器,包括:壳体、处理器、存储器、电路板和电源电路,其中,电路板安置在壳体围成的空间内部,处理器和存储器设置在电路板上;电源电路,用于为上述服务器的各个电路或器件供电;存储器用于存储可执行程序代码;所述处理器通过读取存储器中存储的可执行程序代码来运行与可执行程序代码对应的程序,用于执行上述任意一种芯片测试方法。

[0056]

相应的,如图6所示,本发明一个或多个实施例提供的服务器,可以包括:壳体61、处理器62、存储器63、电路板64和电源电路65,其中,电路板64安置在壳体61围成的空间内部,处理器62和存储器63设置在电路板64上;电源电路65,用于为上述服务器的各个电路或器件供电;存储器63用于存储可执行程序代码;处理器62通过读取存储器63中存储的可执行程序代码来运行与可执行程序代码对应的程序,用于执行前述实施例提供的任意一种芯片扫描测试方法。

[0057]

需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。

[0058]

本说明书中的各个实施例均采用相关的方式描述,各个实施例之间相同相似的部分互相参见即可,每个实施例重点说明的都是与其他实施例的不同之处。

[0059]

尤其,对于装置实施例而言,由于其基本相似于方法实施例,所以描述的比较简单,相关之处参见方法实施例的部分说明即可。

[0060]

为了描述的方便,描述以上装置是以功能分为各种单元/模块分别描述。当然,在实施本发明时可以把各单元/模块的功能在同一个或多个软件和/或硬件中实现。

[0061]

本领域普通技术人员可以理解实现上述实施例方法中的全部或部分流程,是可以通过计算机程序来指令相关的硬件来完成,所述的程序可存储于一计算机可读取存储介质中,该程序在执行时,可包括如上述各方法的实施例的流程。其中,所述的存储介质可为磁碟、光盘、只读存储记忆体(read-only memory,rom)或随机存储记忆体(random access memory,ram)等。

[0062]

以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1