一种实时时钟的中断测试电路的制作方法

1.本实用新型涉及芯片测试设备领域,尤其涉及一种用于对实时时钟芯片进行中断测试,判断脉冲频率响应性能的测试电路。

背景技术:

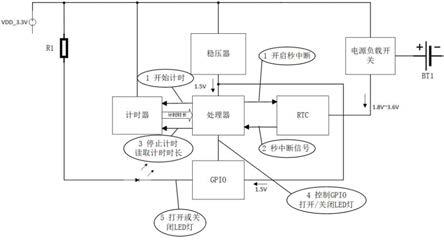

2.在集成电路设计过程中,通常实时时钟芯片(以下部分简称为rtc)的中断测试是不可或缺的一个重要环节,为后续电路设计和芯片集成将提供可靠保障。但传统该测试环节下,如图1所示,gpio输出端一般需要外接示波器并调试查看波形。一方面示波器成本难于节省,另一方面调试示波器也相对费时,观察并判断脉冲频率的直观性较差。

技术实现要素:

3.为了克服现有技术的不足,本实用新型的目的旨在提出一种实时时钟的中断测试电路,并以此改善测试过程的便捷性和可操作性。

4.本实用新型的上述目的,将通过以下技术方案得以实现:一种实时时钟的中断测试电路,通过处理器连接实时时钟芯片控制启闭中断信号,并由处理器通过gpio输出中断脉冲,其特征在于:所述gpio的输出端与输入电压vdd之间接设有led与电阻r1串联的支路。

5.进一步地,在所述处理器与输入电压vdd之间接设有计时器,且计时结果信号与led点亮的计数信号一并信号反馈处理器。

6.本实用新型技术方案应用实施后的显著效果为:该测试电路省却了判断脉冲频率对示波器的依赖,节省了测试成本的同时,通过设置计时时段并反馈led亮灭的响应计数,能够低成本地实现自动判断脉冲脉冲频率的正确性,提高了测试效率。

附图说明

7.图1是传统面对实时时钟的中断测试电路示意图。

8.图2是本实用新型面对实时时钟中断测试改良后的电路示意图。

具体实施方式

9.以下便结合实施例附图,对本实用新型的具体实施方式作进一步的详述,以使本实用新型技术方案更易于理解、掌握。

10.为了降低实时时钟芯片进行中断测试对示波器的高成本依赖,需要人工肉眼观察的不便,本实用新型创新提出了针对该实时时钟中断测试的改良电路。

11.作为该类测试电路传统且必不可少的基础结构,如图1所示,整个测试电路由输入电压vdd_3.3v供能。其中必要性地包括通过处理器相连的rtc和gpio,即待测试的实时时钟芯片和通用输入/输出接口。为匹配处理器及rtc正常运行的额定电压稳定性,该测试电路在处理器的供能端与输入电压vdd之间接设有输出1.5v的稳压器,且稳压器的另一输出端以同样大小的电压输出为gpio供能;而rtc供能端与输入电压vdd之间接设有输出1.8v~

3.6v的电源负载开关。由图示箭头可见,该基础测试电路中,处理器用于面向rtc输出控制中断信号启闭的驱动,且rtc则面向处理器输出所需的中断信号;处理器对该中断信号进行处理后即由gpio对外输出。

12.从本实用新型的创新特点来看,如图2所示的优选实施例,该gpio的输出端与输入电压vdd之间接设有led与电阻r1串联的支路。通过gpio所输出的处理后脉冲信号与输入电压vdd之间的压差变化,以一定频率点亮led,从而可以直观反应脉冲频率大小。其中通过电阻r1分压并赋予led两端压差,故该电阻r1在满足驱动点亮led的前提下无阻值限定要求。同时,在该处理器与输入电压vdd之间接设有还计时器,且计时结果信号与led点亮的计数信号一并信号反馈处理器。这样通过处理器设定计时器的时长,并综合所反馈的led点亮的计数信号,能便利性地自动判断脉冲频率,并以此比较处理器对rtc的驱动信号是否一致。

13.综上实施例及图示到详述可见,该测试电路省却了判断脉冲频率对示波器的依赖,节省了测试成本的同时,通过设置计时时段并反馈led亮灭的响应计数,能够低成本地实现自动判断脉冲脉冲频率的正确性,提高了测试效率。

14.除上述实施例外,本实用新型还可以有其它实施方式。凡采用等同替换或等效变换形成的技术方案,均落在本实用新型所要求保护的范围之内。

技术特征:

1.一种实时时钟的中断测试电路,通过处理器连接待测试的实时时钟芯片和通用输入/输出接口,并面向实时时钟芯片输出控制中断信号启闭的驱动,且实时时钟芯片面向处理器输出所需的中断信号,由处理器通过通用输入/输出接口输出中断脉冲,其特征在于:所述通用输入/输出接口的输出端与输入电压vdd之间接设有led与电阻r1串联的支路。2.根据权利要求1所述实时时钟的中断测试电路,其特征在于:在所述处理器与输入电压vdd之间接设有计时器,且计时结果信号与led点亮的计数信号一并信号反馈处理器。3.根据权利要求1所述实时时钟的中断测试电路,其特征在于:所述处理器的供能端与输入电压vdd之间接设有输出1.5v的稳压器,且稳压器的另一输出端接入gpio。4.根据权利要求1所述实时时钟的中断测试电路,其特征在于:所述实时时钟芯片的供能端与输入电压vdd之间接设有输出1.8v~3.6v的电源负载开关。

技术总结

本实用新型揭示了一种实时时钟的中断测试电路,通过处理器连接实时时钟芯片控制启闭中断信号,并由处理器通过GPIO输出中断脉冲,其特征在于:该GPIO的输出端与输入电压VDD之间接设有LED与电阻R1串联的支路;且在所述处理器与输入电压VDD之间接设有计时器,计时结果信号与LED点亮的计数信号一并信号反馈处理器。应用本实用新型该测试电路,省却了判断脉冲频率对示波器的依赖,节省了测试成本的同时,通过设置计时时段并反馈LED亮灭的响应计数,能够低成本地实现自动判断脉冲脉冲频率的正确性,提高了测试效率。提高了测试效率。提高了测试效率。

技术研发人员:陆网锁 徐建华

受保护的技术使用者:宜宾芯汇信息科技有限公司

技术研发日:2020.12.30

技术公布日:2021/12/28

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1