评估电子装联材料可靠性的测试方法与流程

1.本技术涉及电子装联技术领域,尤其涉及一种评估电子装联材料可靠性的测试方法。

背景技术:

2.现有评估电子装联材料可靠性的测试方法,测试场景与应用场景存在巨大差异,在评估电子装联材料的可靠性的时候,不能准确评估出材料的差异,因此,需要新的符合应用场景的测试方法。

技术实现要素:

3.本技术一方面提供一种评估电子装联材料可靠性的测试方法,其包括:提供菊花链芯片假件及电路板,其中,菊花链芯片假件包括第一电路,电路板包括与第一电路的图案互补的第二电路;使第一电路和第二电路通过电子装联材料形成第一菊花链链路及第二菊花链链路;以及使第一菊花链链路及第二菊花链链路之间形成电压差,检测第一菊花链链路及第二菊花链链路之间的表面绝缘电阻的变化,以评估电子装联材料的表面绝缘电阻能力。

4.该测试方法中,菊花链芯片假件依照菊花链的走线规则具有第一电路,而电路板参考用于测试的菊花链芯片假件的第一电路设置有与第一电路的图案互补的第二电路。当菊花链芯片假件组装到电路板上后,第一电路和第二电路组合成两条完整的菊花链链路(即,第一菊花链链路及第二菊花链链路)。通过使第一菊花链链路及第二菊花链链路之间形成电压差,检测第一菊花链链路及第二菊花链链路之间的表面绝缘电阻的变化,进而评估电子装联材料的表面绝缘电阻能力。由于菊花链芯片假件具有与真实芯片一致的封装。因此,该测试方法更符合真实应用场景,对电子装联材料的评估更准确和科学。

5.在本技术的一些实施例中,电子装联材料包括锡膏,形成第一菊花链链路及第二菊花链链路的步骤包括:于电路板上印刷锡膏;将菊花链芯片假件贴装至电路板上,使第一电路通过锡膏和第二电路连接,进而形成第一菊花链链路及第二菊花链链路;以及回流。该测试方法中,印刷锡膏、贴片及回流的步骤与真实芯片的应用场景中印刷锡膏、贴片及回流的步骤一致,因此,能够更准确科学地评估电子装联材料的表面绝缘电阻能力。

6.在本技术的一些实施例中,形成第一菊花链链路及第二菊花链链路的步骤还包括回流后,于菊花链芯片假件及电路板之间的间隙内设置底部填充胶;评估电子装联材料的表面绝缘电阻能力的步骤中,评估的为锡膏和底部填充胶的表面绝缘电阻能力,或者说评估的为锡膏和底部填充胶的材料兼容性。

7.在本技术的一些实施例中,评估电子装联材料的表面绝缘电阻能力的步骤包括于第一菊花链链路及第二菊花链链路上分别施加负电压及正电压,以使得第一菊花链链路与第二菊花链链路之间具有电压梯度。当设置有菊花链芯片假件的电路板处于高温高湿的环

境中时,电子装联材料(如,锡膏)中的阳极金属会被水解形成金属离子,由于第一菊花链链路及第二菊花链链路之间具有电压梯度,在电场力的作用下,电子装联材料中水解出的金属离子会迁移到电压为负的第一菊花链链路,并被还原逐渐形成树枝状金属沉积物,被称为“晶枝”。若晶枝从电压为负的第一菊花链链路向电压为正的第二菊花链链路生长,使第一菊花链链路和第二菊花链链路之间连接,则第一菊花链链路和第二菊花链链路之间会发生短路,导致第一菊花链链路和第二菊花链链路之间的表面绝缘电阻显著降低,使设置有菊花链芯片假件的电路板中发生电化学迁移失效。该测试方法中,通过检测第一菊花链链路和第二菊花链链路之间表面绝缘电阻的变化,检测设置有菊花链芯片假件的电路板中是否存在电化学迁移失效的现象以及发生电化学迁移失效所用的时间,进而评估电子装联材料的表面绝缘电阻能力。

8.在本技术的一些实施例中,第一菊花链链路的一端被施加负电压,另一端电性连接至一可靠性测试系统。第二菊花链链路的一端被施加正电压,另一端电性连接至可靠性测试系统。可靠性测试系统实时监测第一菊花链链路及第二菊花链链路之间的表面绝缘电阻的变化,以评估电子装联材料的表面绝缘电阻能力。

9.在本技术的一些实施例中,当第一菊花链链路及第二菊花链链路之间的表面绝缘电阻降至106欧姆级别时,表明第一菊花链链路及第二菊花链链路之间存在电化学迁移失效,可靠性测试系统通过监测发生电化学迁移失效的时间,评估电子装联材料的表面绝缘电阻能力。在其他实施例中,还可以采用其他标准定义第一菊花链链路及第二菊花链链路之间是否存在电化学迁移失效。

10.在本技术的一些实施例中,评估电子装联材料的表面绝缘电阻能力的步骤中,测试环境的温度为85℃,湿度为85%。通过使电子装联材料处于高温高湿的测试环境中,测试第一菊花链链路及第二菊花链链路之间存在电化学迁移失效的时间,以评估电子装联材料的表面绝缘电阻能力。

11.在本技术的一些实施例中,第一电路包括用于形成第一菊花链链路的一部分的多个第一引脚及用于形成第二菊花链链路的一部分的多个第二引脚;其中,每一第一引脚的周边至少有一个第二引脚,每一第二引脚的周边至少有一个第一引脚。如此,当第一菊花链链路和第二菊花链链路被分别施加负电压及正电压后,每一第一引脚与紧邻其的第二引脚之间、及每一第二引脚与紧邻其的第一引脚之间均会形成电压梯度。在高温高湿的环境下,在电场力的作用下,电子装联材料中水解出的金属离子会迁移到电压为负的第一引脚,并被还原逐渐形成晶枝。若晶枝从电压为负的第一引脚向电压为正的第二引脚生长,使第一引脚和第二引脚之间连接,则第一菊花链链路和第二菊花链链路之间会发生短路,导致第一菊花链链路和第二菊花链链路之间的表面绝缘电阻显著降低,使设置有菊花链芯片假件的电路板中发生电化学迁移失效。

12.在本技术的一些实施例中,对应于每一个第一引脚和每一个第二引脚,第二电路均设置有一个焊盘位置,焊盘位置用于通过电子装联材料与其所对应的一个第一引脚或一个第二引脚电性连接。其中,焊盘位置可通过印刷锡膏实现与对应的第一引脚或第二引脚电性连接。

13.在本技术的一些实施例中,菊花链芯片假件包括由相邻的两个第一引脚电性连接形成的第一引脚对和/或由相邻的两个第二引脚电性连接形成的第二引脚对。菊花链芯片

假件还包括第一基板和第一走线,第一电路位于第一基板的表面上,第一走线可以为第一基板内部的线路或者为第一基板的表面的线路。第一基板的材质为半导体,例如硅。菊花链芯片假件中,至少部分第一引脚与紧邻其的一个第一引脚通过第一走线电性连接而形成一个第一引脚对,至少部分第二引脚与紧邻其的一个第二引脚通过第一走线电性连接而形成一个第一引脚对。此外,由于电路板上的第二电路与菊花链芯片假件的第一电路的图案互补,因此,菊花链芯片假件的引脚之间设置有第一走线的位置,对应于电路板上,相邻焊盘位置之间未设置走线;而菊花链芯片假件的引脚之间相邻的两个第一引脚或相邻的两个第二引脚之间没有设置第一走线的位置,对应于电路板上,相邻焊盘位置之间设置有走线。如此,当菊花链芯片假件组装到电路板上后,第一电路和第二电路组合形成至少两条完整的菊花链链路。

14.在本技术的一些实施例中,菊花链芯片假件中,部分第一引脚与任意一个第一引脚、任意一个第二引脚均为电性绝缘的(定义为孤立引脚),和/或部分第二引脚与任意一个第一引脚、任意一个第二引脚均为电性绝缘的(定义为孤立引脚)。菊花链芯片假件中,各个引脚可以以引脚对的方式排列,也可以以引脚对和孤立引脚组合的方式排列。即,第一电路中,第一引脚可以均以第一引脚对的方式排列,也可以以第一引脚对和孤立引脚的组合的方式排列;同样,第一电路中,第二引脚可以均以第二引脚对的方式排列,也可以以第二引脚对和孤立引脚的组合的方式排列。

15.在本技术的一些实施例中,菊花链芯片假件为引脚外露型的封装结构或引脚在器件底部型的封装结构。由于菊花链芯片假件具有与真实芯片一致的封装。因此,该测试方法更符合真实应用场景,对电子装联材料(如锡膏)的评估更准确和科学。无论是引脚外露型的芯片封装结构还是引脚在器件底部型的芯片封装结构,菊花链芯片假件均能准确地模拟真实芯片在焊接回流过程中助焊剂挥发情况。

16.在本技术的一些实施例中,菊花链芯片假件为球栅阵列封装结构、方形扁平无引脚封装结构、小尺寸封装结构、塑封有引线芯片载体封装结构、无引线陶瓷芯片载体封装结构、芯片尺寸封装结构之一,但不限于此。

附图说明

17.图1为本技术的一些实施例,提供的评估电子装联材料可靠性的测试方法的流程示意图。

18.图2为本技术的一些实施例,提供的菊花链芯片假件的电路示意图。

19.图3为本技术的一些实施例,提供的电路板的电路示意图。

20.图4为图2中的菊花链芯片假件与图3中的电路板组装后的电路示意图。

21.图5为测试过程中,第一引脚及第二引脚上的电压示意图。

22.图6为采用本技术的一些实施例的评估电子装联材料可靠性的测试方法,测试的两种方案的sir能力的测试数据图。

23.图7为采用现有技术中的测试方法,测试的两种方案的sir能力的测试数据图。

24.图8为示意出引脚与引脚之间电迁移的x射线(x

‑

ray)图。

25.图9为示意出引脚与引脚之间电迁移的计算机断层扫描(computed tomography,ct)图。

26.图10为现有技术中,梳状电路板的平面示意图。

27.图11为图10中的电路的放大示意图。

28.主要元件符号说明菊花链芯片假件

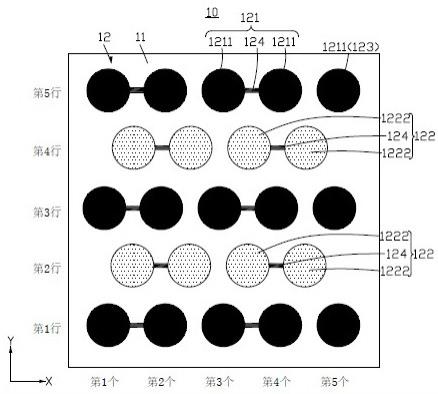

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

10第一基板

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

11第一电路

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

12第一引脚对

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

121第一引脚

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

1211第二引脚对

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

122第二引脚

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

1222孤立引脚

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

123第一走线

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

124电路板

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

20第二基板

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

21第二电路

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

22焊盘位置

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

221第二走线

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

223第一菊花链链路

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

31第二菊花链链路

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

32梳状电路板

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

40梳状导线

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

42如下具体实施方式将结合上述附图进一步说明本技术。

具体实施方式

29.为了方便理解本技术实施例的方案,首先对本技术实施例涉及到的相关技术进行描述。电子产品线路板(printed circuit board assembly,pcba)上的表面组装元器件发展至今,已经有多种封装类型的表面组装元件/表面组装器件(surfacemountedcomponents/surfacemounteddevices,smc/smd)用于电子产品的生产。目前,集成芯片(integrated circuit,ic)引脚间距越来越密,由最初的1.27mm发展至0.8mm、0.65mm、0.4mm、0.35mm以及0.3mm,引脚与引脚间的最小间距已经到0.15mm,相当于一根稍粗的头发丝的直径的距离。而引脚与引脚之间在长期通电的情况下,有电化学迁移失效的风险。其中,图8箭头所指的位置及图9箭头所指的位置示意出了相邻的两个引脚之间由于电化学迁移而失效的现象。

30.此外,电子产品为保证用户使用过程中的机械可靠性以及环境可靠性,需要在芯片底部增加底部填充胶。由于焊接用锡膏残留助焊剂与底部填充胶具有一定的不兼容性,会导致芯片环境可靠性下降,出现电化学腐蚀或者离子迁移,最终导致产品失效,影响用户体验。电子产品在环境测试中经常出现相关失效。解决此类问题的核心是要求锡膏助焊剂与底部填充胶具备材料兼容性,并通过严苛的双85环境可靠性测试。业界ipc有标准的测试方法,主要是梳状电路法测试电子装联材料(如锡膏、底部填充胶以及锡膏和底部填充胶)

的表面绝缘电阻(surface insulation resistance,sir)能力。

31.图10及图11分别为梳状电路板40的平面示意图及局部放大图。当前梳状电路板测试法主要存在以下问题:其一,测试过程中需要在梳状电路板40的梳状导线42上印刷锡膏,锡膏回流在敞开的环境下,助焊剂挥发比较充分,然而,对于引脚外露型的芯片封装结构,焊接回流过程中助焊剂挥发充分,而对于引脚在器件底部型的芯片封装结构,焊接回流过程助焊剂不能充分挥发。测试场景与实际应用场景差异较大。其二,标准梳状电路中,相邻的两个梳状导线42之间的间隙为0.5mm,其不能模拟测试引脚间距为0.15mm的sir能力。其三,梳状电路板40表面涂敷的胶水厚度不可控,与实际ic类器件底部填充胶水厚度在0.2mm以内且厚度均匀可控相比,测试场景与应用场景差异巨大。因此,需要新的符合应用场景的测试方法。

32.此外,需要说明的是,在本技术实施例中,菊花链(daisy

‑

chain)芯片假件,也称空封装(dummy package)或假芯片(fake chip),其一般采用与真实芯片相似的无功能的假裸片(dummy die)且与真实芯片相似或一致的封装组成,但其基板与真实芯片的基板有区别。在菊花链芯片假件的基板上,有特定的走线图案,当其贴装到与其匹配(即,电路图案互补)的电路板上时,就能形成连续的并连接菊花链芯片假件的引脚的菊花链链路。也就是说,菊花链芯片假件依照菊花链的走线规则,在其基板上具有通过走线将引脚连接在一起的菊花链支路;而电路板的基板参考用于测试的菊花链芯片假件的走线及引脚的设置,设计有互补的走线。也就是说,电路板上设置有与菊花链芯片假件上的菊花链支路的图案互补的菊花链支路(也称反式菊花链支路)。当菊花链芯片假件组装到电路板上后,两个菊花链支路就组合成了完整的菊花链链路。此外,菊花链芯片假件及电路板可以从制作厂商处采购或定做。

33.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行描述。

34.图1为本技术的一些实施例,提供的评估电子装联材料可靠性的测试方法的流程示意图。根据不同需求,所述测试方法的步骤顺序可以改变,某些步骤可以省略或合并。

35.步骤s1:提供菊花链芯片假件及电路板。

36.图2为本技术的一些实施例,提供的菊花链芯片假件10的电路示意图。如图2所示,菊花链芯片假件10包括第一基板11及位于第一基板11上的第一电路12。

37.具体地,第一电路12包括多个第一引脚1211、多个第二引脚1222及第一走线124。第一引脚1211、第二引脚1222均位于第一基板11的表面上。第一走线124可以为第一基板11内部的线路或者为第一基板11的表面的线路。第一引脚1211用于在后续步骤中,形成第一菊花链链路31(标注在图4中)的一部分,第二引脚1222用于在后续步骤中,形成第二菊花链链路32(标注在图4中)的一部分。第一基板11的材质为半导体,例如硅。

38.图2中,多个第一引脚1211、多个第二引脚1222沿y轴方向排布为多行。定义沿y轴正向,自下至上分别为第1、2、...、n行(n为大于等于2的整数)。每一行的第一引脚1211或第二引脚1222中,定义沿x轴方向上,自左至右,分别为第1、2、...、m个(m为大于等于1的整数)第一引脚1211或第二引脚1222。x轴垂直于y轴。图2中,n=5;奇数行中,m=5;偶数行中,m=4。奇数行的引脚为第一引脚1211,偶数行的为第二引脚1222。每一第一引脚1211的周边至少有一个第二引脚1222,每一第二引脚1222的周边至少有一个第一引脚1211。

39.在其他实施例中,菊花链芯片假件10中的引脚数量、排列密集程度不限于图2所

示。

40.多个第一引脚1211中,部分第一引脚1211与紧邻其的一个第一引脚1211通过第一走线124电性连接而形成一个第一引脚对121,部分第一引脚1211与任意一个第一引脚1211、任意一个第二引脚1222均为电性绝缘的,在图2中,标注为孤立引脚123。此外,图2中每一第二引脚1222与紧邻其的一个第二引脚1222通过第一走线124电性连接而形成一个第二引脚对122。在其他实施例中,部分第二引脚1222中,也可包括与任意一个第一引脚1211、任意一个第二引脚1222均为电性绝缘的孤立引脚123。

41.图3为本技术的一些实施例,提供的电路板20的电路示意图。如图3所示,电路板20包括第二基板21及位于第一基板11上的第二电路22。

42.具体地,电路板20可以为印刷电路板。第二基板21为绝缘的。第二电路22定义有多个焊盘位置221(图3中,以空心的圆示意)。其中,多个焊盘位置221沿y轴方向排布为多行。定义沿y轴正向,自下至上分别为第1、2、...、p行(p为大于等于2的整数,且p大于等于n)。每一行的焊盘位置221中,定义沿x轴方向上,自左至右,分别为第1、2、

…

、q个(q为大于等于1的整数,且q大于等于m)焊盘位置221。图3中,p=n=5;奇数行中,q=m=5;偶数行中,q=m=4。

43.在其他实施例中,焊盘位置221的行数及每行焊盘位置221的数量可以为p>n和/或q>m。该多个焊盘位置221用于后续步骤中,在其上印刷锡膏,通过锡膏与菊花链芯片假件10上的第一引脚1211或第二引脚1222电性连接。图3中,第二电路22还包括设置于第二基板21上的多个第二走线223,每一第二走线223设置于两个相邻的焊盘位置221之间。

44.请同时参阅图2和图3,菊花链芯片假件10上的第一电路12的图案与电路板20上的第二电路22的图案为互补的。即,当将菊花链芯片假件10与电路板20贴合时,第一电路12可与第二电路22配合形成至少两条完整的菊花链链路。

45.具体地,对应于菊花链芯片假件10的每一第一引脚1211,电路板20上均设置有一个焊盘位置221;对应于菊花链芯片假件10的每一第二引脚1222,电路板20上均设置有一个焊盘位置221。在后续贴片制程中,在电路板20的焊盘位置221上印刷锡膏后,菊花链芯片假件10的第一引脚1211或第二引脚1222可通过该锡膏连接至对应的焊盘位置221上。

46.具体地,菊花链芯片假件10上第1行的第1、2、

…

、5个第一引脚1211一一对应于电路板20上第2行的第1、2、

…

、5个焊盘位置221;菊花链芯片假件10上第2行的第1、2、

…

、4个第二引脚1222一一对应于电路板20上第2行的第1、2、

…

、4个焊盘位置221;依此类推,第n行的第1、2、

…

、m个第一引脚1211或第二引脚1222一一对应于电路板20上第n行的第1、2、

…

、m个焊盘位置221。

47.此外,在菊花链芯片假件10的引脚之间设置有第一走线124的位置,对应于电路板20上,相邻焊盘位置221之间未设置第二走线223;在菊花链芯片假件10上,相邻的两个第一引脚1211或相邻的两个第二引脚1222之间没有设置第一走线124的位置,对应于电路板20上,相邻焊盘位置221之间设置有第二走线223。例如,菊花链芯片假件10上,第1行第1个第一引脚1211与第1行第2个第一引脚1211之间设置有第一走线124,而对应于电路板20上,第1行第1个焊盘位置221与第1行第2个焊盘位置221之间没有设置第二走线223;菊花链芯片假件10上,第1行第2个第一引脚1211与第1行第3个第一引脚1211之间未设置第一走线124,而对应于电路板20上,第1行第2个焊盘位置221与第1行第3个焊盘位置221之间设置有第二走线223。

48.步骤s2:印刷锡膏。

49.具体地,在电路板20的焊盘位置221处印刷锡膏,使每一焊盘位置221处形成一焊垫(图未示)。

50.步骤s3:贴片。

51.具体地,将菊花链芯片假件10贴装至电路板20上。每一第一引脚1211及每一第二引脚1222均通过锡膏电性连接至对应的焊盘位置221处。如图3所示,多个第一引脚1211通过第一走线124、第二走线223及在焊盘位置221的锡膏顺次连接形成第一菊花链链路31。其中,每一第一引脚1211通过锡膏电性连接至电路板20上对应的焊盘位置221处,相邻的第一引脚对121之间、第一引脚对121与孤立引脚123之间、孤立引脚123与孤立引脚123之间通过位于电路板20上的第二走线223连接。多个第二引脚1222通过第一走线124、第二走线223及在焊盘位置221的锡膏顺次连接形成第二菊花链链路32。相邻的第二引脚对122之间通过位于电路板20上的第二走线223连接。此外,第一菊花链链路31及第二菊花链链路32为相互绝缘的。也就是说,图4中,第一走线124与第二走线223交叉的位置为绝缘间隔设置的。

52.需要说明的是,本技术的实施例中,以菊花链芯片假件10贴装至电路板20上后形成两条菊花链链路为例进行说明。在其他实施例中,菊花链芯片假件贴装至电路板上后,形成的菊花链链路数量不限于为两条,且形成的菊花链链路的图案也不限于图4所示。

53.步骤s4:回流。

54.在本技术的一些实施例中,将贴装有菊花链芯片假件10的电路板20放置入回流焊机的轨道中,经过升温、保温、焊接、冷却等环节,将锡膏从膏状经高温变为液体,再经冷却变成固体状,从而实现贴片电子元器件(即菊花链芯片假件10)与电路板20焊接的作用。

55.需要说明的是,该测试方法中,印刷锡膏、贴片及回流的步骤与真实芯片的应用场景中印刷锡膏、贴片及回流的步骤一致,以较佳地评估电子装联材料的表面绝缘电阻(surface insulation resistance,sir)能力。

56.步骤s5:上电测试。

57.在本技术的一些实施例中,回流后直接对第一菊花链链路31及第二菊花链链路32进行上电测试。

58.如图4所示,第一菊花链链路31的一端被施加负电压,第二菊花链链路32的一端被施加正电压。而第一菊花链链路31的另一端及第二菊花链链路32的另一端连接至一可靠性测试系统(图未示)的测试接口,通过将贴装有菊花链芯片假件菊花链芯片假件10的电路板放置于高温高湿的环境中加速其失效,可靠性测试系统实时监测第一菊花链链路31与第二菊花链链路32之间的表面绝缘电阻值的变化,以判断第一菊花链链路31与第二菊花链链路32是否失效,进而评估电子装联材料(如锡膏)的表面绝缘电阻能力。其中,表面绝缘电阻能力可以理解成为阻止引脚或者引脚表面短路的能力。

59.具体地,步骤s5中,上电测试为对电子装联材料(如锡膏)进行双85环境可靠性测试。即,将贴装有菊花链芯片假件10的电路板20放置于温度为85℃,湿度为85%的高温高湿测试环境中。

60.此外,由于菊花链芯片假件10中,每一第一引脚1211的周边至少有一个第二引脚1222,每一第二引脚1222的周边至少有一个第一引脚1211。因此,如图4及图5所示,上电测试后,第一菊花链链路31和第二菊花链链路32被分别施加负电压及正电压,每一第一引脚

1211与紧邻其的第二引脚1222之间、及每一第二引脚1222与紧邻其的第一引脚1211之间均会形成电压梯度。

61.由于贴装有菊花链芯片假件10的电路板20处于高温高湿的环境中,因此,在绝缘材料(如,第二基板21)的表面容易凝结水膜,锡膏中的阳极金属会被水解形成金属离子,由于第一引脚1211与第二引脚1222之间具有电压梯度,在电场力的作用下,锡膏中水解出的金属离子会迁移到电压为负的第一引脚1211,并被还原逐渐形成树枝状金属沉积物,被称为“晶枝”。若晶枝从电压为负的第一引脚1211向电压为正的第二引脚1222生长,使第一引脚1211和第二引脚1222之间连接,则第一菊花链链路31和第二菊花链链路32之间会发生短路,导致第一菊花链链路31和第二菊花链链路32之间的表面绝缘电阻显著降低,使贴装有菊花链芯片假件10的电路板20中发生电化学迁移失效。该测试方法中,通过实时监测第一菊花链链路31和第二菊花链链路32之间表面绝缘电阻,检测贴装有菊花链芯片假件10的电路板20中是否存在电化学迁移失效的现象;若贴装有菊花链芯片假件10的电路板20中存在电化学迁移失效的现象,则通过监测发生电化学迁移失效的时间,可以评估电子装联材料(如锡膏)的sir能力。

62.步骤s6:点胶。

63.在本技术的另一些实施例中,回流后,于菊花链芯片假件10及电路板20之间的间隙内设置底部填充胶(图未示)。然后再进行上电测试。该种情况下,上电测试步骤中,评估的为锡膏和底部填充胶的表面绝缘电阻能力,或者说评估的为锡膏和底部填充胶的材料兼容性。其中,底部填充胶可通过点胶机形成。

64.需要说明的是,图2中,示出的菊花链芯片假件10为引脚在器件底部型的封装结构,用以评估电子装联材料(如锡膏、底部填充胶以及锡膏和底部填充胶)应用至真实芯片为引脚在器件底部型的封装结构的绝缘电阻能力。在本技术的其他实施例中,菊花链芯片假件10可以为引脚外露型的封装结构,以评估电子装联材料(如锡膏、底部填充胶以及锡膏和底部填充胶)应用至真实芯片为引脚外露型的封装结构的绝缘电阻能力。

65.具体地,菊花链芯片假件10可以为本领域技术人员所知的各种封装形式中的一种,如球栅阵列(ball grid array, bga)封装结构、方形扁平无引脚(quad flat non

‑

leaded package,qfn)封装结构、小尺寸封装(small outline package,sop)结构、塑封有引线芯片载体(plastic leaded chip carrier,plcc)封装结构、无引线陶瓷芯片载体(leadless ceramic chip carrier,lccc)封装结构、芯片尺寸封装(chip size package,csp)结构之一。

66.由于该测试方法中,菊花链芯片假件具有与真实芯片一致的封装。因此,该测试方法更符合真实应用场景,对电子装联材料(如锡膏)的评估更准确和科学。具体地,其一,无论是引脚外露型的芯片封装结构还是引脚在器件底部型的芯片封装结构,菊花链芯片假件均能准确地模拟真实芯片在焊接回流过程中助焊剂挥发情况。其二,由于菊花链芯片假件具有与真实芯片一致的封装,因此,其能够准确模拟测试引脚间距为0.15mm的sir能力,而标准梳状电路中,由于相邻的两个梳状导线之间的间隙为0.5mm,其不能模拟测试引脚间距为0.15mm的sir能力。其三,菊花链芯片假件的引脚上的底部填充胶的厚度均匀可控。

67.以下结合图6及图7,对比说明本技术实施例的测试方法与现有技术中的测试方法,测试的两种方案(方案一与方案二)的sir能力的效果。图6及图7中,横坐标均为时间,单

位为小时(h),纵坐标均为表面绝缘电阻,单位为欧姆(ω)。其中,方案一与方案二的区别点在于其电子装联材料不同。需要说明的是,一般地,当表面绝缘电阻降至106欧姆级别时,表明电路板中存在电化学迁移失效的现象。如图7所示,采用本技术实施例的测试方法,方案一在101小时时开始失效,而方案二在405小时失效。而现有技术的测试方法(ipc

‑

b

‑

24),如图6所示,方案一与方案二均能通过480h的高温高湿测试。也就是说,对于方案一和方案二,现有技术的测试方法无法测试出方案一与方案二的电子装联材料的sir能力的差异。而本技术实施例的测试方法,由于采用菊花链芯片假件进行测试,更接近于真实芯片的使用场景,可实现高密电子装联材料sir能力的精确评估。

68.以上实施例仅用以说明本技术的技术方案而非限制,尽管参照较佳实施例对本技术进行了详细的说明,本领域的普通技术人员应当理解,可以对本技术的技术方案进行修改或等同替换,而不脱离本技术技术方案的精神和实质。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1