时间测量电路、电子系统以及相应的集成电路的制作方法

1.本说明书的实施例涉及时间测量电路。

背景技术:

2.在多种应用中,被配置为测量在第一(开始)事件与第二(停止)事件之间经过的时间的时间测量电路(计时器)是有用的。

3.例如,在pwm信号的背景中可以使用时间测量电路。通常,如图1所示,pwm信号是具有给定开关时段t

sw

的周期性信号,其中pwm信号被设置为针对给定接通持续时间t

on

为高,以及针对给定断开持续时间t

off

为低,其中:

4.t

sw

=t

on

+t

off (1)

5.而且,通常定义pwm信号的占空比d,其中d=t

on

/t

sw

。

6.可以在各种模式中生成这种pwm信号。例如,如图1所示,最简单的解决方案中的一个解决方案是基于振荡器电路以及计数器的,该振荡器电路生成时钟信号clk,以及该计数器被配置为响应于时钟信号clk而增加计数值。因此,通过使用比较器电路,可以例如根据由计数器所提供的计数值来生成pwm信号(例如,通过比较计数值与给定阈值,该给定阈值例如指示接通持续时间t

on

和开关时段t

sw

)。

7.例如,当pwm信号被用于驱动(例如,经由半桥或全桥)谐振电路时,时间测量电路可能是有用的,该谐振电路包括一个或多个电感和/或电容(例如,lc谐振回路)。例如,典型应用可以是无线功率传输器或电子转换器。例如,在该应用中,测量在pwm信号(表示开始事件)的上升边沿和/或下降边沿与给定事件(响应于pwm的上升边沿或下降边沿而生成)之间经过的时间可以是有用的。例如,计时器可以测量在pwm信号的上升边沿与当电流流经谐振回路的给定部件或在谐振回路的给定部件或节点处的电压(例如,流经lc谐振回路的部件中的一个部件的电流或该lc谐振回路的部件中的一个部件处的电压(诸如lc谐振回路的振铃节点处的电压))达到给定阈值时的时刻之间经过的时间。

技术实现要素:

8.考虑到前述内容,本公开的各种实施例提供了用于测量在开始事件与停止事件之间经过的时间的解决方案。更具体地,各种实施例涉及用于确定相位值的解决方案,该相位值指示在时钟信号的边沿与异步事件信号被设置时的时刻之间经过的时间。

9.本公开的一方面提供了一种时间测量电路,被配置为生成相位值,时间测量电路包括:多相时钟生成器,被配置为生成给定数目n个相移时钟相位的序列,相移时钟相位具有相同的时钟时段并且相移了对应于时钟时段的分数1/n的时间,其中相移时钟相位中的一个相移时钟相位表示参考时钟信号;节点,被配置为接收异步事件信号;相位采样电路,被配置为生成相位值,相位值指示在参考时钟信号的边沿与异步事件信号被设置时的时刻之间经过的时钟时段的分数1/n的数目。

10.根据一个或多个实施例,其中相位采样电路包括:第一子电路,包括针对相移时钟

相位中的每个相移时钟相位的相应的第一触发器,相应的第一触发器被配置为响应于异步事件信号,对相应的相移时钟相位进行采样,从而确定相应的第一控制信号,相应的第一控制信号指示在异步事件信号被设置时的时刻处,相应的时钟相位是被设置为高还是被设置为低;第二子电路,包括针对相移时钟相位中的每个相移时钟相位的相应的第二触发器,相应的第二触发器被配置为响应于相应的相移时钟相位,对相应的第一控制信号进行采样,从而确定与相应的第一控制信号的同步版本相对应的相应的第二控制信号;第三子电路,被配置为:将相移时钟相位中的每个相移时钟相位与另一时钟相位相关联,另一时钟相位对应于以时间在相应时钟相位之前的相移时钟相位序列的相移时钟相位;针对相移时钟相位中的每个相移时钟相位,确定相应的第三控制信号,相应的第三控制信号指示:与相应的相移时钟相位相关联的第二控制信号是否指示在异步事件信号被设置时的时刻处,相应的相移时钟相位被设置为低,以及与相应的另一时钟相位相关联的第二控制信号是否指示在异步事件信号被设置时的时刻处,相应的另一时钟相位被设置为高;以及第四子电路,包括针对相移时钟相位中的每个相移时钟相位的相应的第三触发器,相应的第三触发器被配置为响应于相应的相移时钟相位,对相应的第三控制信号进行采样,从而确定与相应的第三控制信号相对应的相应的第四控制信号。

11.根据一个或多个实施例,其中:第一触发器中的每个第一触发器被配置为,响应于异步事件信号的上升边沿,对相应的相移时钟相位进行采样;以及第二触发器中的每个第二触发器被配置为,响应于相应的相移时钟相位的下降边沿,对相应的第一控制信号进行采样。

12.根据一个或多个实施例,时间测量电路包括针对相移时钟相位中的每个相移时钟相位的相应的逻辑or门,相应的逻辑or门被配置为,在输入处接收由相应的第一触发器所提供的相应的第一控制信号和由相应的第二触发器所提供的相应的第二控制信号,从而确定相应的第五控制信号,并且其中第二触发器中的每个第二触发器被配置为,对相应的第五控制信号进行采样,由此仅当相应的第一控制信号被设置为高时,第二触发器中的每个第二触发器才对相应的第一控制信号进行采样。

13.根据一个或多个实施例,其中第三子电路包括针对相移时钟相位中的每个相移时钟相位的相应的逻辑and门,每个逻辑and门被配置为,在输入处接收与相应的相移时钟相位相关联的第二控制信号的反相版本,以及与相应的另一时钟相位相关联的第二控制信号,从而生成相应的第三控制信号。

14.根据一个或多个实施例,其中:第三触发器中的每个第三触发器被配置为响应于相应的相移时钟相位的上升边沿,对相应的第三控制信号进行采样。

15.根据一个或多个实施例,其中第一触发器、第二触发器和第三触发器被配置为经由重置信号来重置。

16.根据一个或多个实施例,其中另一触发器与第二触发器的每个触发器或第三触发器中的每个触发器级联连接。

17.根据一个或多个实施例,其中第四控制信号表示相位值的独热编码

18.根据一个或多个实施例,其中根据选择信号,在相移时钟相位之中选择参考时钟信号,并且其中相位值是根据第四控制信号和选择信号确定的。

19.根据一个或多个实施例,时间测量电路包括:计数器电路,被配置为响应于参考时

钟信号而增加计数值;以及计数器采样电路,被配置为通过对计数值进行采样来生成经采样计数值。

20.根据一个或多个实施例,其中计数器采样电路包括:第一采样电路,被配置为响应于参考时钟信号的上升边沿,对异步事件信号进行采样,从而生成第一经同步的异步事件信号;第二采样电路,被配置为响应于参考时钟信号的下降边沿,对异步事件信号进行采样,从而生成第二经同步的异步事件信号;以及采样电路,被配置为响应于参考时钟信号的上升边沿,根据第一经同步的异步事件和第二经同步的异步事件存储计数器电路的计数值或经减一的计数器电路的计数值,从而生成经采样计数值。

21.根据本公开的另一方面,提供了一种电子系统,包括:时间测量电路,包括:多相时钟生成器,被配置为生成给定数目n个相移时钟相位的序列,相移时钟相位具有相同的时钟时段并且被相移了对应于时钟时段的分数1/n的时间,其中相移时钟相位中的一个相移时钟相位表示参考时钟信号;节点,被配置为接收异步事件信号;相位采样电路,被配置为生成相位值,相位值指示在参考时钟信号的边沿与异步事件信号被设置时的时刻处之间经过的时钟时段的分数1/n的数目;计数器电路,被配置为响应于参考时钟信号而增加计数值;以及计数器采样电路,被配置为通过对计数值进行采样来生成经采样计数值;以及脉冲宽度调制pwm信号生成器电路,被配置为根据计数器电路的计数值来生成脉冲宽度调制信号,其中经采样计数值和相位值指示时钟循环的数目以及在脉冲宽度调制信号的边沿与异步事件信号被设置时的时刻处之间经过的参考时钟信号的分数1/n的数目。

22.根据一个或多个实施例,其中相位采样电路包括:第一子电路,包括针对相移时钟相位中的每个相移时钟相位的相应的第一触发器,相应的第一触发器被配置为响应于异步事件信号,对相应的相移时钟相位进行采样,从而确定相应的第一控制信号,相应的第一控制信号指示在异步事件信号被设置时的时刻处,相应时钟相位是被设置为高还是被设置为低;第二子电路,包括针对相移时钟相位中的每个相移时钟相位的相应的第二触发器,相应的第二触发器被配置为响应于相应的相移时钟相位,对相应的第一控制信号进行采样,从而确定与相应的第一控制信号的同步版本相对应的相应的第二控制信号;第三子电路,被配置为:将相移时钟相位中的每个相移时钟相位与另一时钟相位相关联,另一时钟相位对应于以时间在相应时钟相位之前的相移时钟相位序列的相移时钟相位;确定针对相移时钟相位中的每个相移时钟相位的相应的第三控制信号,相应的第三控制信号指示:与相应的相移时钟相位相关联的第二控制信号是否指示在异步事件信号被设置时的时刻处,相应的相移时钟相位被设置为低,以及与相应的另一时钟相位相关联的第二控制信号是否指示在异步事件信号被设置时的时刻处,相应的另一时钟相位被设置为高;以及第四子电路,包括针对相移时钟相位中的每个相移时钟相位的相应的第三触发器,相应的第三触发器被配置为响应于相应的相移时钟相位,对相应的第三控制信号进行采样,从而确定与相应的第三控制信号相对应的相应的第四控制信号。

23.根据一个或多个实施例,其中时间测量电路包括:针对相移时钟相位中的每个相移时钟相位的相应的逻辑or门,逻辑or门被配置为在输入处接收由相应的第一触发器所提供的相应的第一控制信号和由相应的第二触发器所提供的相应的第二控制信号,从而确定相应的第五控制信号,并且其中第二触发器中的每个第二触发器被配置为对相应的第五控制信号进行采样,由此第二触发器中的每个第二触发器仅当相应的第一控制信号被设置为

高时,才对相应的第一控制信号进行采样。

24.根据一个或多个实施例,其中时间测量电路的第三子电路包括:针对相移时钟相位中的每个相移时钟相位的相应的逻辑and门,每个逻辑and门被配置为在输入处接收与相应的相移时钟相位相关联的第二控制信号的反相版本以及与相应的另一时钟相位相关联的第二控制信号,从而生成相应的第三控制信号。

25.根据本公开的又一方面,提供了一种集成电路,包括:时间测量电路,包括:多相时钟生成器,被配置为生成给定数目n个相移时钟相位的序列,相移时钟相位具有相同的时钟时段并且相移了对应于时钟时段的分数1/n的时间,其中相移时钟相位中的一个相移时钟相位表示参考时钟信号;节点,被配置为接收异步事件信号;相位采样电路,被配置为生成相位值,相位值指示在参考时钟信号的边沿与异步事件信号被设置时的时刻处之间经过的时钟时段的分数1/n的数目。

26.根据一个或多个实施例,其中相位采样电路包括:第一子电路,包括针对相移时钟相位中的每个相移时钟相位的相应的第一触发器,相应的第一触发器被配置为响应于异步事件信号,对相应的相移时钟相位进行采样,从而确定相应的第一控制信号,相应的第一控制信号指示在异步事件信号被设置时的时刻处相应时钟相位是被设置为高还是被设置为低;第二子电路,包括针对相移时钟相位中的每个相移时钟相位的相应的第二触发器,相应的第二触发器被配置为响应于相应的相移时钟相位,对相应的第一控制信号进行采样,从而确定与相应的第一控制信号的同步版本相对应的相应的第二控制信号;第三子电路,被配置为:将相移时钟相位中的每个相移时钟相位与另一时钟相位相关联,另一时钟相位对应于以时间在相应时钟相位之前的相移时钟相位序列的相移时钟相位;针对相移时钟相位中的每个相移时钟相位,确定相应的第三控制信号,相应的第三控制信号指示:与相应的相移时钟相位相关联的第二控制信号是否指示在异步事件信号被设置时的时刻处,相应的相移时钟相位被设置为低,以及与相应的另一时钟相位相关联的第二控制信号是否指示在异步事件信号被设置时的时刻处,相应的另一时钟相位被设置为高;以及第四子电路,包括针对相移时钟相位中的每个相移时钟相位的相应的第三触发器,相应的第三触发器被配置为响应于相应的相移时钟相位,对相应的第三控制信号进行采样,从而确定与相应的第三控制信号相对应的相应的第四控制信号。

27.根据一个或多个实施例,其中时间测量电路包括:计数器电路,被配置为响应于参考时钟信号而增加计数值;以及计数器采样电路,被配置为通过对计数值进行采样来生成经采样计数值。

28.根据一个或多个实施例,集成电路还包括:脉冲宽度调制pwm信号生成器电路,被配置为根据计数器电路的计数值来生成脉冲宽度调制信号,其中经采样计数值和相位值指示时钟循环的数目以及在脉冲宽度调制信号的边沿与异步事件信号被设置时的时刻处之间经过的参考时钟信号的分数1/n的数目。

29.利用本公开提供的实施例,计时器电路被配置为响应于异步事件,以高分辨率、最小延迟且没有亚稳性问题的情况下以相干方式存储时间信息和/或相位信息。

附图说明

30.现在,参考附图,对本公开的实施例进行描述,这些附图纯粹以非限制性示例的方

式提供,并且其中:

31.图1示出了pwm信号的示例;

32.图2示出了生成多相时钟信号的电路的示例。

33.图3示出了由图2的电路所提供的时钟相位的波形的示例;

34.图4示出了借助于多相时钟信号来对pwm信号的接通持续时间进行微调的示例;

35.图5示出了借助于多相时钟信号来对pwm信号的接通持续时间和关断持续时间二者进行微调的实施例;

36.图6a和图6b示出了根据本公开的计时器电路的实施例;

37.图7示出了由图6a和图6b的定时器电路所生成的示例性波形;

38.图8示出了pwm生成器电路的实施例;

39.图9a、图9b、图10a、图10b、图10c、图11a、图11b、图12a、图12b、图12c和图12d示出了图6a、图6b和图8的电路的各种细节;

40.图13示出了被配置为响应于异步事件而确定经采样计数值和采样相位值的定时器电路的实施例;

41.图14示出了被配置为响应于异步事件来确定经采样计数值的计数值采样电路的实施例;

42.图15、图16和图17示出了图14的计数值采样电路的细节;以及

43.图18、图19和图20示出了被配置为响应于异步事件而确定采样相位值的相位值采样电路的实施例。

具体实施方式

44.在后续描述中,对各种具体细节进行了说明,旨在实现对实施例的深入理解。在没有这些具体细节中的一个或多个特定细节的情况下或通过其他方法、部件、材料等,可以提供实施例。在其他情况下,没有对已知结构、材料或操作进行详细示出或描述,从而不会使实施例的各个方面晦涩难懂。

45.在本说明书的框架中对“一实施例”或“一个实施例”的引用意指指示相对于该实施例描述的特定配置、结构或特点包括在至少一个实施例中。因此,可能在本说明书的各个方面中出现的诸如“在一实施例中”、“在一个实施例中”之类的短语不一定是指一个相同实施例。而且,在一个或多个实施例中,可以以任何适当方式组合特定构象、结构或特点。

46.仅为了方便而提供本文中所使用的参考,因此不限定实施例的保护界限或范围。

47.在下文所描述的图2至图20中,已经参考图1所描述的部分、元件或部件由这些图中先前使用的相同附图标记指定。已经对这些元件进行了描述,并且在以下内容中不再进行重复,以免使本具体实施方式繁琐。

48.如前所述,时间测量电路(计时器)在各种应用中可以是有用的,该时间测量电路被配置为测量在第一(开始)事件与第二(停止)事件之间经过的时间,诸如用于测量在pwm信号的上升边沿和/或下降边沿(表示开始事件)与响应于pwm信号的上升边沿或下降边沿而生成的给定事件之间经过的时间。通常,第二/停止事件因此可以经由异步外部信号来发信号通知。

49.因此,在对时间测量电路的实施例进行讨论之前,首先将对用于生成pwm信号的第

一可能解决方案进行讨论。

50.如关于图1所描述的,用于生成pwm信号的最简单的解决方案中的一个解决方案是基于生成时钟信号clk的振荡器电路和被配置为响应于时钟信号clk而增加计数值的计数器的。因此,通过使用比较器电路,可以例如根据由计数器所提供的计数值来生成pwm信号,例如,通过比较计数值与给定阈值,该给定阈值例如指示接通持续时间t

on

和开关时段t

sw

。

51.然而,在这种(数字)实现方式中,pwm信号的准确度和分辨率受时钟信号clk的时钟时段t

clk

(采样频率)的限制。而且,随着增加时钟频率f

clk

=1/t

clk

,开关损耗也将会增加。

52.然而,在许多应用中,高分辨率的pwm信号是必需的或非常优选的。例如,如前所述,pwm信号可以用于许多应用,以控制电压或电流的平均值,这些许多应用诸如:用于无线电池充电器、开关模式功率转换器、电机控制和照明。例如,在这种应用中,半桥或全桥可以用于驱动通常包括一个或多个电感器和电容器的谐振回路,其中半桥或全桥的电子开关借助于pwm信号来驱动。

53.为了使设备小型化,可以使用较小电感器,从而导致工作频率较高。因此,通常应当提供具有高精度分辨率的高频调制波形pwm信号,以便将功耗保持处于可接受值处。例如,在开关电源中,输出电压通常与pwm占空比成正比。对占空比的调整越小,对输出的最终改变就越小,即,对输出电压的更精确控制准许实现更好的准确度水平和系统稳定性。而且,使输出电压纹波最小意指降低噪声水平。

54.用于生成pwm信号(特别是高分辨率(hr)pwm信号)的备选解决方案基于使用多个时钟相位,即,具有相同频率的相移时钟信号。

55.例如,图2示出了用于经由延迟锁定环(dll)生成多个时钟相位φ0..φ

n

的可能电路。

56.具体地,在所考虑的示例中,由振荡器osc所生成的时钟信号clk被馈送到多个(相同)延迟级du1..du

n

的级联。具体地,在所考虑的示例中,第一相位φ0与时钟信号clk相对应,而其他相位φ1..φ

n

与延迟级du1..du

n

的输出信号相对应。

57.在所考虑的示例中,延迟级du1..du

n

中的每个延迟级具有根据(电压或电流)控制信号ctrl而可编程/可设置的延迟t

du

。例如,具有可变延迟的这种延迟级du可以使用偶数个反相器来实现,其中反相器中的一个或多个反相器对连接到反相器的输出的诸如寄生电容的相应电容进行充电。在这种情况下,控制信号ctrl可以指示由反相器所提供的用于对相应电容进行充电的电流,从而使直到随后反相器切换为止的时间发生变化。

58.在所考虑的示例中,最后一个相位φ

n

(相对于时钟信号clk具有给定延迟t

d

=n

·

t

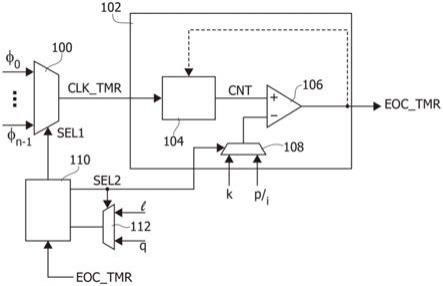

du

)和时钟信号clk被提供给相位检测器pd。相位检测器pd的输出被馈送到具有至少i(积分)部件的调节器cp(诸如电荷泵),其中调节器cp在输出处提供控制信号ctrl。可选地,控制信号ctrl可以通过环路滤波器lf传递。

59.因此,本质上讲,由块pd/cp/lf所实现的负反馈回路在时间上使最后一个相位φ

n

与时钟信号clk同步。如果延迟单元du相同,则所有时钟相位φ1..φ

n

将具有相同频率f

clk

,但是相对于前一相位相移了延迟t

du

=t

clk

/n。

60.这样的多个时钟相位也可以通过锁相环(pll)提供,该锁相环包括压控振荡器(vco),该压控振荡器包括具有多个延迟级的环形振荡器,其中pll被锁定到时钟信号clk的频率。此外,在这种情况下,pll的锁定可以通过使得由延迟级所引入的延迟发生变化来获

得,例如,通过经由偏置电路使得由实现这种延迟级的反相器级所提供的电流发生变化,直到在vco的输出处的振荡器信号与时钟信号clk相对应为止。因此,vco的每个延迟级可以提供相应时钟相位,该相应时钟相位被相移了时钟信号clk的时段的给定分数。

61.例如,图3示出了在n=17的情况下相位φ1..φ

16

的示例性波形,其中图中未示出最后一个相位φ

17

=φ0=clk。

62.因而,如图4所示,虽然计数器和相应比较器电路可以提供粗略pwm信号(具有时钟信号clk的多个k时钟循环),但是可以使用附加时钟相位φ1..φ

n

来对粗略pwm信号添加微调,这本质上准许将时钟信号clk的分数t

du

添加到粗略pwm信号。例如,文献us7,206,343b2中描述了这种解决方案,为此,其内容通过引用并入本文。

63.例如,分数可以通过以下方式添加到粗略pwm信号:

64.例如通过使用一个或多个逻辑(例如,or)门,直接组合具有给定选定时钟相位φ的粗略pwm信号,或

65.如文献us 7,206,343 b2中所述,通过附加延迟级使得粗略pwm信号间接地传递、并且例如经由逻辑(例如,or)门将粗略pwm信号与延迟pwm信号组合,其中附加延迟级引入了与延迟级du1..dun相同的延迟t

du

,例如,通过使用与延迟级du1..du

n

相同的控制信号ctrl偏置附加延迟级。

66.因此,假设计数器(和相应比较器电路)提供具有开关时段t

sw

=i

·

t

clk

和接通持续时间t

on

=k

·

t

clk

(0≤k≤i)的粗略pwm信号,则最终pwm信号可以具有开关时段t

sw

=i

·

t

clk

和接通持续时间t

on

=k

·

t

clk

+l

·

t

clk

/n(0≤l<n)。因此,可以通过设置参数k和l的整数值来选择pwm信号的接通持续时间t

on

。因此,本质上讲,使用附加dll或pll准许以较高精度使接通持续时间t

on

发生变化(或一般地使占空比d发生变化),同时开关时段t

sw

保持恒定。

67.然而,在各种实施例中,pwm信号生成器电路还可以被配置为接收多个时钟相位φ0..φ

n

,并且根据这些时钟相位φ0..φ

n

生成pwm信号的上升边沿和下降边沿二者,从而以较高分辨率控制pwm占空比和pwm频率两者。

68.图5示出了第一实施例的一般操作。

69.在所考虑的实施例中,pwm信号生成器电路接收第一时钟相位φ0(和/或最后时钟相位φ

n

=φ0)和中间时钟相位φ1..φ

n

‑1。在一些实施例中,pwm信号生成器电路包括多相时钟生成器,其生成各种时钟相位,该多相时钟生成器可以包括被配置为生成本文中所描述的时钟相位的任何多相时钟生成器。在本公开的介绍中已经对用于生成这种时钟相位的可能解决方案进行了描述,并且相关描述整体适用(特别是参见图2的描述)。也就是说,在一些实施例中,本公开的各种实施例的多相时钟生成器电路可以例如相对于图2进行描述。

70.而且,在所考虑的实施例中,pwm信号生成器电路被配置为生成pwm信号,其中:

71.开关持续时间t

sw

可以设置为t

sw

=i

·

t

clk

+j

·

t

clk

/n;以及

72.接通时间t

on

可以设置为t

on

=k

·

t

clk

+l

·

t

clk

/n。

73.在各种实施例中,参数i、j、k和l是整数值,其中参数i、j、k和l可以是可编程的。

74.具体地,在图5所示的示例中,假设n=17,例如,pwm信号生成器电路接收时钟相位φ0..φ

16

,并且pwm信号生成器电路被配置为生成pwm信号,其中:

75.t

sw

=i

·

t

clk

+10

·

t

clk

/17=t

i

+10

·

t

clk

/17,

76.占空比为50%(即,t

on

=t

off

=t

sw

/2),即,

77.t

on

=t

off

=t

i

/2+5

·

t

clk

/17。

78.在所考虑的示例中,为了简单起见,假设i为偶数,并且k=p=i/2。

79.具体地,在所考虑的实施例中,pwm信号生成器电路被配置为在第一接通时段t1期间将相位φ0用作用于数字计数器的时钟信号,该数字计数器对时间时段t

i

/2=k

·

t

clk

进行计数,并且(如以下所更详细地描述的)pwm信号生成器电路通过使用相位φ5在结束时添加时段t

clk

的分数5/17。

80.然而,作为随后跟踪各种分数的累加的替代,pwm信号生成器电路在随后关断时段t2期间将相位φ5(即,用于添加分数的相位)用作用于定时器电路(即,对时间时段p

·

t

clk

进行计数的数字计数器)的时钟信号。而且,pwm信号生成器电路通过在这种情况下使用相位φ

10

在结束时再次添加时段t

clk

的相应分数5/17,直到相位φ

10

相对于相位φ5偏移了延迟5

·

t

clk

/17。

81.接下来,pwm信号生成器电路在第二接通时段t3期间将相位φ

10

用作用于数字计数器的时钟信号,该数字计数器对时间时段k

·

t

clk

进行计数,并且pwm信号生成器电路这次通过使用相位φ

15

在结束时添加时段t

clk

的分数5/17,直到相位φ

15

相对于相位φ

10

偏移了延迟5

·

t

clk

/17。

82.同样,pwm信号生成器电路在随后关断时段t4期间将相位φ

15

用作用于数字计数器的时钟信号,该数字计数器对时间时段p

·

t

clk

进行计数,并且pwm信号生成器电路这次通过使用相位φ3在结束时添加时段t

clk

的分数5/17,直到相位φ3相对于相位φ

15

偏移了延迟5

·

t

clk

/17。

83.该操作还针对随后的接通时段和关断时段继续进行。

84.在各种实施例中,pwm生成器电路因此被配置为生成pwm信号,其中:

85.接通持续时间与t

on

=k

·

t

clk

+l

·

t

clk

/n相对应;以及

86.关断持续时间与t

off

=p

·

t

clk

+q

·

t

clk

/n相对应。

87.在各种实施例中,参数n(延迟级数/相位)在硬件水平处被固定。然而,数目n也可以是可编程的,例如,通过在图2中使用给定固定数目个延迟级(例如,32个)、并且选择第n个相位(不一定是最后一个)作为提供给相位检测器pd的反馈信号。实际上,在这种方式中,控制环路仍被锁定到第n个相位φ

n

,,其中t

du

=t

clk

/n。

88.因此,在各种实施例中,pwm信号生成器电路的定时器电路(包括计数器电路和比较器电路)被配置为:

89.在接通时段t

on

期间,从重置值开始增加计数值,直到计数值达到整数值k为止;以及

90.在关断时段t

off

期间,从重置值开始增加计数值,直到计数值达到整数值p为止。

91.然而,一般而言,计时器电路还可以监测开关持续时间t

sw

,即,pwm信号生成器电路的计时器电路(包括计数器电路和比较器电路)可以被配置为:

92.在接通时段期间,从重置值开始增加计数值,直到计数值达到整数k值为止;以及

93.在关断时段期间,增加在接通时段期间使用的计数值,直到计数值达到整数值i为止。

94.因此,在各种实施例中,pwm信号生成器电路被配置为确定参数k/l以及p/q和i/j中的至少一个参数,其中:

95.在接通时段t

on

的情况下,k对应于时钟信号clk的时钟循环的整数数目,并且l对应于时钟信号clk的时钟循环的分数1/n的整数数目;

96.在关断时段t

off

的情况下,p对应于时钟信号clk的时钟循环的整数数目,并且q对应于时钟信号clk的时钟循环的分数1/n的整数数目;以及

97.在开关时段t

sw

的情况下,i对应于时钟信号clk的时钟循环的整数数目,并且j对应于时钟信号clk的时钟循环的分数1/n的整数数目。

98.具体地,鉴于上述定义:

99.t

on

=k

·

t

clk

+l

·

t

clk

/n

ꢀꢀꢀ

(2)

100.t

off

=p

·

t

clk

+q

·

t

clk

/n

ꢀꢀ

(3)

101.t

sw

=t

on

+t

off

=i

·

t

clk

+j

·

t

clk

/n

ꢀꢀ

(4)

102.根据以下公式,整数值i和j与整数值k、l、p和q有关:

103.如果(l+q)<n(无溢出),则:

104.i=k+p;j=l+q,

ꢀꢀꢀꢀ

(5)

105.如果(l+q)>n(有溢出),则:

106.i=k+p+1;j=l+q

–

n。

ꢀꢀꢀ

(6)

107.因此,在各种实施例中,pwm生成器电路被配置为接收参数i、k和p中的至少两个参数,以及参数j、l和q中的至少两个参数。例如,pwm信号生成器电路可以直接接收参数k/l和/或p/q和/或i/j,诸如:

108.标识(例如,对应于)参数k/l的数据;以及

109.标识(例如,对应于)参数p/q的数据。

110.备选地,pwm信号生成器电路可以接收其他数据,从而准许根据等式(5)和(6)计算这些参数,诸如:

111.标识开关持续时间t

sw

的数据,诸如上文所提及的参数i和j,以及以下各项中的一项:

112.标识(例如,对应于)参数k/l的数据;

113.标识(例如,对应于)参数p/q的数据;或

114.标识占空比的数据。

115.如图6a所示,在各种实施例中,pwm信号生成器电路包括计时器电路102,该计时器电路102包括数字计数器电路104,该数字计数器电路104被配置为响应于时钟信号clk_tmr而使整数计数值cnt发生变化(即,增加或减小);以及比较器电路106,该比较器电路106被配置为比较计数值cnt与相应整数比较阈值。

116.如图6a所示,通过例如经由多路复用器108选择参数k或p作为比较阈值,相同计数器104和比较器106可以用于接通时段和关断时段两者。因而,通过经由比较器106的输出处的信号来重置计数器104,相同计数器104可以用于监测接通时段和关断时段。然而,计数器104也可以用于监测接通时段和持续时间t

sw

。例如,在这种情况下,多路复用器108可以接收参数k和i,并且仅当计数值cnt达到值i时才可以重置计数器104。

117.备选地,如图6b所示,相应计数器104a和104b以及比较器106a和106b可以用于接通时段和关断时段,其中比较器106a比较由计数器104a所提供的计数值cnta与参数k,而比较器106b比较由计数器104b所提供的计数值cntb与参数p。

118.在各种实施例中,计时器电路102被配置为当比较器的输出指示计数值已经达到比较阈值时(例如,通过使用在比较器106的输出处的信号eoc_tmr或在比较器106a和106b的输出处的信号eoc_tmra和eoc_tmrb),生成一个或多个触发信号。

119.在所考虑的实施例中,信号eoc_tmr(图6a)或信号eoc_tmra和eoc_tmrb(图6b)被提供给控制电路110,该控制电路110根据以下各项选择用于定时器电路102(特别是计数器104(104a/104b))的时钟信号clk_tmr:

120.在接通时段期间,参数l;以及

121.在关断时段期间,参数q。

122.具体地,即使在监测开关持续时间t

sw

的结束时,优选的是例如根据等式(5)和(6)获得(例如,计算)参数q,这是因为该参数指示必须相对于先前接通时间被添加的附加分数。

123.例如,控制电路110可以通过经由选择信号sel1驱动在输入处接收时钟相位φ0..φ

n

‑1的多路复用器100,来选择时钟信号clk_tmr。同样,控制信号可以经由选择信号sel2驱动多路复用器112,以便选择参数l或参数q,亦即,选择信号指示当前时段是接通时段还是关断时段,并且因此还可以用于驱动多路复用器108。

124.具体地,在各种实施例中,响应于在信号eoc_tmr(图6a)或信号eoc_tmra和eoc_tmrb(图6b)中的触发,控制电路110被配置为改变选择信号sel1的逻辑值:

125.在接通时段期间,根据参数l;以及

126.在关断时段期间,根据参数q。

127.具体地,在各种实施例中,控制电路还执行模运算,以便将选择信号sel1维持在介于0与n

‑

1之间。因而,响应于信号eoc_tmr(图6a)或信号eoc_tmra和eoc_tmrb(图6b)中的触发,控制电路110使选择信号sel1发生变化:

128.在接通时段期间,sel1=(sel1+l)mod n;以及

129.在关断时段期间,sel1=(sel1+q)mod n。

130.因此,本质上讲,控制电路110实现了相位累加器电路,该相位累加器电路将l或q添加到当前选择的相位,其中(例如,如等式(5)和(6)所示)可以根据参数j和n计算参数q。

131.最终,在各种实施例中,相应时段(接通时段或关断时段)被终止,并且随后时段利用选定时钟相位的下一时钟脉冲(即,基于定时器电路102使用哪种类型的边沿的下一上升边沿或下降边沿)开始。

132.因此,本质上讲,在接通时段t

on

期间,在时间k

·

t

clk

之后生成触发信号eoc_tmr(或eoc_tmra),并且通过改变时钟信号clk_tmr来终止接通时段,从而在附加时间l/n

·

t

clk

之后,开始下一关断时段。同样,在关断时段t

off

期间,在时间p

·

t

clk

之后生成触发信号eoc_tmr(或eoc_tmrb)(其例如可以通过重置计数器104并且等待p个循环或通过等待直到计数值达到i为止而获得),并且通过改变时钟信号clk_tmr来终止关断时段,从而在附加时间q/n

·

t

clk

之后,开始下一接通时段。

133.例如,这在图7中示出,其中在接通时段期间,定时器电路使用时钟相位clk_tmr=φ

x

,并且例如在例如具有第10个上升边沿的相位φ

x

的k=9个时段之后,触发信号eoc_tmr被设置。响应于触发信号eoc_tmr(eoc_tmra),控制电路选择新相位clk_tmr=φ

y

(其中y=(x+l)mod n)。而且,响应于在信号φ

y

中紧随其后的(例如,上升)边沿,pwm信号生成器电路

终止接通时段,并且开始随后的关断时段,从而引入了与时钟时段的分数l/n相对应的附加时间。

134.在所考虑的实施例中,在随后的关断时段期间,计时器电路使用时钟相位clk_tmr=φ

y

,并且例如在例如具有第9个上升边沿的相位φ

y

的p=8个时段之后,触发信号eoc_tmr被设置。响应于触发信号eoc_tmr(eoc_tmrb),控制电路选择新相位clk_tmr=φ

z

(其中z=(y+q)mod n)。响应于在信号φ

z

中紧随其后的(例如,上升)边沿,pwm信号生成器电路终止关断时段,并且开始随后的接通时段,从而引入了与时钟时段的分数q/n相对应的附加时间。

135.在先前实施例中,控制电路110被配置为驱动选择电路100,以便响应于信号eoc_tmr,将指派给时钟信号clk_tmr的相位φ从当前相位φ(t)(例如,φ0)改变为下一相位φ(t+1)(例如,φ5),从而在相应接通或关断时段结束处添加分数(l或q)。

136.然而,在各种实施例中,从当前相位φ(t)到下一相位φ(t+1)的切换可能在相应时段期间的任何时刻发生。在这种情况下,控制单元110还可以被配置为:例如,响应于时钟信号clk_tmr,将选择信号sel1从旧相位φ(t)顺序增大/减小到新相位φ(t+1)(例如,φ0、φ1、φ2、φ3、φ4、φ5),或通过切换直接增大/减小到新相位φ(t+1)。

137.通常,虽然已经参考时钟信号clk的时段,但实际上相位φ0...φ

n

‑1也可以具有不同的时钟时段t

pll

,例如,频率f

pll

=1/t

pll

可以是时钟频率f

clk

的倍数,例如,通过在相位φ

n

‑1的反馈环路中使用分频器。因而,一般而言:

138.接通持续时间与t

on

=k

·

t

pll

+l

·

t

pll

/n相对应;以及

139.关断持续时间与t

off

=p

·

t

pll

+q

·

t

pll

/n相对应。

140.图8示出了pwm信号生成器电路的第二实施例。

141.具体地,在所考虑的实施例中,pwm信号生成器电路再次包括定时器电路102、时钟切换电路100

′

和控制电路/相位累加器110

′

。

142.具体地,对于图6a和图6b,时钟切换电路100

′

不是仅使用多路复用器、而是使用一种电路来实现的,该电路响应于由定时器电路102所提供的触发信号eoc_tmr而根据由控制电路110

′

所提供的选择信号sel1,直接生成用于定时器电路的时钟信号clk_tmr。通常,如前所述,任何其他触发信号也可以被用于根据选择信号sel1向时钟信号clk_tmr指派新时钟相位。

143.例如,在图9a和图9b中示出了时钟切换电路100

′

的可能实施例。

144.在所考虑的实施例中,选择信号sel1(指示下一时钟相位)被提供给一系列可选锁存器1000,可选锁存器1000被配置为响应于触发信号eoc_tmr而存储信号sel1的值。基本上讲,这些锁存器1000确保仅当生成在信号eoc_tmr中的触发时,电路才对信号sel1的值进行采样。

145.在所考虑的实施例中,每个时钟相位φ0…

φ

n

‑1被提供给相应传输门(门控时钟单元)10020...1002

n

,其根据选择信号sel1或可选锁存选择信号sel1而被启用,从而生成相应(门控)信号φ

0_gtd

…

φ

n

‑

1_gtd

。例如,在各种实施例中,选择信号包括(n个)位sel0...sel

n

‑1并且使用独热编码,其中给定位与给定时钟相位φ0...φ

n

‑1单义相关联(即,位sel0...sel

n

‑1中只有一个位被设置),并且指示相应时钟相位φ0...φ

n

‑1可以通过相应传输门10020...1002

n

‑1,而其他时钟相位φ0...φ

n

‑1无法通过相应传输门10020...1002

n

‑1。一般

而言,其他编码方案还可以用于选择信号(诸如二进制编码),并且传输门可以经由被配置为根据选择信号sel1生成用于传输门10020...1002

n

‑1的独热编码驱动信号的解码器电路来驱动。

146.如图9b所示,信号φ

0_gtd

…

φ

n

‑

1_gtd

然后被提供给组合逻辑电路1004,该组合逻辑电路1004被配置为在输出处通过组合信号φ

0_gtd

...φ

n

‑

1_gtd

来生成用于定时器电路102的时钟信号clk_tmr。例如,在各种实施例中,信号φ

0_gtd

…

φ

n

‑

1_gtd

经由逻辑or运算来组合,例如,使用多个or门or1、or2、or3等的级联结构来实现。

147.图10a示出了时钟切换电路100

′

在依序具有值k、x和y的选择信号sel1示例处的操作,从而(响应于触发信号eoc_tmr)依序激活时钟相位φ

k_gtd

、φ

x_gtd

和φ

y_gtd

。

148.因此,在选择信号sel1发生改变的情况下,时钟信号clk_tmr响应于选择信号而从第一时钟相位切换到第二时钟相位。

149.具体地,如图10b所示,当第二时钟相位(φ

x_gtd

)变为高(上升边沿)、并且第一时钟相位(φ

k_gtd

)仍为高时,所产生的时钟信号clk_tmr将会具有持续时间高于时钟相位φ0...φ

n

‑1的时钟时段t

pll

的单个时钟脉冲,从而实质上损失了一时钟循环。

150.通常,当相应分数l或q小于n/2时,这种情况将会发生。

151.相反,如图10c所示,当第二时钟相位(φ

y_gtd

)变为高(上升边沿)、并且第一时钟相位(φ

x_gtd

)为低时,所产生的时钟信号clk_tmr具有持续时间小于时钟相位φ0...φ

n

‑1的时钟时段t

pll

的单个时钟脉冲。通常,当相应分数l或q大于n/2时,这种情况将会发生。

152.因此,为了正确确定相应时间间隔的持续时间,应当考虑丢失的时钟边沿(图10b)。具体地,在各种实施例中,如果丢失时钟循环(即,相应分数l或q小于n/2),则pwm信号生成器电路被配置为将计时器电路102增加一个附加时钟循环,即,在单个时钟循环内,计时器102增加2,而非仅增加1。

153.图11a示出了定时器电路102的可能实施例。

154.具体地,在所考虑的实施例中,计数器104使用累加器实现,该累加器包括:

155.寄存器1040,其在输出处提供计数值cnt,其中寄存器1040被配置为响应于时钟信号clk_tmr而存储在相应输入处的信号reg_in;以及

156.数字加法器1042,其被配置为通过将增量值inc添加到计数值cnt来在寄存器1040的输入处生成信号reg_in。

157.在所考虑的实施例中,可以例如经由多路复用器1044将增量值inc设置为“1”或“2”。具体地,选择经由通过控制电路110所提供的选择信号sel3(或同样通过控制电路110

′

)驱动。

158.具体地,在所考虑的实施例中,控制电路110包括:

159.数字比较器1100,其被配置为确定当前接通时段或当前关断时段的分数值l或q是否大于n/2;以及

160.电路1102,其被配置为根据由比较器1100所生成的比较信号和指示新接通时段或新关断时段的开始的触发信号(诸如信号eoc_tmr)来生成选择信号sel3;或在通常情况下根据由比较器1100所生成的比较信号和长度为一个clk_tmr循环并且在接通时段或关断时段期间的任何适当时刻生成的通用触发信号来生成选择信号sel3。

161.具体地,在所考虑的实施例中,多路复用器112已经提供了针对当前时段的分数

值,其中选择信号sel2指示当前时段是接通时段还是关断时段。因而,比较器1100可以在输入处接收由多路复用器112所提供的信号,并且因此生成指示分数值l或q是否大于n/2的比较信号。具体地,电路110和112被配置为:

162.当在比较器的输出处的信号指示分数l或q(基于当前时段)大于n/2或触发信号(例如,eoc_tmr)未被设置时,经由信号sel3驱动多路复用器1044,以便选择值“1”,由此累加器1040/1042响应于时钟信号clk_tmr而增加“1”;以及

163.当在比较器的输出处的信号指示分数l或q(基于当前时段)小于n/2并且触发信号(例如,eoc_tmr)已被设置时,经由信号sel3驱动多路复用器1044,以便选择值“2”,由此累加器1040/1042响应于时钟信号clk_tmr而增加“2”。

164.因而,基本上讲,定时器电路104被配置为当分数l或q(基于当前时段)小于n/2时,针对信号clk_tmr的一个时钟循环(即,每个接通时段或关断时段的单个循环),将计数值增加二(“2”)。

165.相反,图11b示出了可以通过直接调整由比较器106所使用的阈值来获得相似结果。

166.具体地,在所考虑的实施例中,增量值inc总是被设置为“1”,并且提供了附加数字减法器,其例如经由多路复用器1048被配置为:

167.从由多路复用器108所选择的当前阈值(k或p)减去值“1”;或

168.维持阈值,例如,通过从由多路复用器108所选择的当前阈值(k或p)减去值“0”。

169.一般而言,还可以组合实施例,即,在接通持续时间期间,可以通过“加二”机构(图11a)或阈值k的调整(图11b)来实现,并且可以在关断持续时间期间,通过“加二”机构或阈值p的调整来实现。

170.因而,在所考虑的实施例中,电路1100/1102通知计时器电路102由于图9b所示的时钟组合而已经错过了计数边沿或即将错过计数边沿。该错过边沿信息(即,信号sel3)可以由控制电路/相位累加器机器110/110

′

计算,该控制电路/相位累加器机器110/110

′

控制精细延迟选择、并且生成相位选择改变sel1(指示要用于对pwm信号进行微调的下一时钟相位)。实际上,如果新相位选择选择了具有在运行时钟的接通时间期间出现上升边沿的时钟,则组合clk_tmr将具有较长接通时间,并且用于图9b的时钟组合电路装置的下一选定时钟相位的边沿将会被错过。如果相位选择改变小于可用相位的数目的一半,则会发生这种情况,即,当相应分数l或q小于n/2(例如,)时,发生这种情况。

171.使用该时钟改变属性,计时器可以递增“1”或“2”,或比较器106的阈值可以相对于如图11a或图11b所示生成的该内部标志来进行调整。

172.在各种实施例中,响应于新时钟相位(即,随后接通时段或关断时段的选定时钟相位φ

0_gtd

...φ

n

‑

1_gtd

)的下一上升边沿,对pwm信号进行切换。然而,在给定时隙/时段期间的任何适当时刻中生成sel1信号的情况下,响应于触发信号eoc_tmr的上升边沿,还可以改变pwm信号。

173.例如,如图8所示,pwm信号生成器电路可以包括触发电路114,该触发电路114被配置为根据信号φ

0_gtd

...φ

n

‑

1_gtd

和触发信号eoc_tmr生成pwm信号。

174.通常,响应于信号eoc_tmr(或eoc_tmra和eoc_tmrb)和新时钟相位,任何合适电路可以用于切换pwm信号的水平。

175.例如,图12a示出了触发电路114的实施例。具体地,触发电路114包括上升边沿检测器电路。具体地,在所考虑的实施例中,触发电路包括针对信号φ

0_gtd

...φ

n

‑

1_gtd

中的每个信号的相应上升边沿检测器11400..1140

n

‑1,其根据信号eoc_tmr而被启用。

176.具体地,如图12b、图12c和图12d所示,响应于当前时钟相位的上升边沿(例如,图12c中的φ

k_gtd

),信号eoc_tmr将会在短暂延迟之后被设置。响应于在信号eoc_tmr中的触发,电路100

′

将切换到新时钟相位(例如,图12c中的φ

x_gtd

)。因此,旧时钟信号的附加上升边沿(例如,图12c中的φ

k_gtd

)不会出现。因此,响应于新时钟相位中的随后上升边沿(例如,图12c中的φ

x_gtd

),相应边沿检测器1140将会设置其输出(例如,设置为高),这也是因为信号eoc_tmr仍被设置。

177.因而,在所考虑的实施例中,为此,各种上升边沿检测器11400..1140

n

‑1的输出可以被连接到例如实现逻辑or功能的组合逻辑电路(图12a示意性地示出了逻辑or门or4,其可能与or门链中的最后一个or门相对应,例如,包括级联的具有3个输入的6个or门、具有2个输入的2个or门、以及or门or4),但是总的来说,由于相对于速度和时钟相位的数目的平衡过程不同,所以可以使用不同数目和拓扑的门来实现各种上升边沿检测器11400..1140

n

‑1的输出,这会在输出处生成触发信号trig,该触发信号trig指示pwm信号的逻辑水平必须改变。

178.因而,在所考虑的实施例中,信号trig可以用于驱动触发器ff1,以便使触发器ff1的输出反相,其中pwm信号根据在触发器ff1的输出处的信号生成(并且优选地,与该信号相对应)。

179.例如,在所考虑的实施例中,触发器ff1使用d型触发器实现,其经由反相器inv1在数据端子d处接收触发器ff1的反相输出信号,从而响应于触发信号trig,使触发器ff1的输出反相。

180.发明人已经观察到,上述时钟信号clk_tmr还可以用于实现(高分辨率)精密计时器,即,定时器电路,其被配置为生成指示开始事件与停止事件之间经过的时间的信号。

181.具体地,如前所述,pwm信号通常用于控制电压或电流的平均值。例如,pwm信号通常用于无线电池充电器、开关模式电源(电子转换器)、电机控制和照明中。例如,当pwm信号用于驱动(例如,经由半桥或全桥)谐振电路时,该计时器可能是有用的,该谐振电路包括一个或多个电感和电容,例如,lc谐振回路。例如,典型应用可以是无线功率发射器或电子转换器。例如,在该应用中,测量在pwm信号的上升边沿和/或下降边沿与给定事件(响应于pwm信号的上升边沿或下降边沿而生成的)之间经过的时间可以是有用的。例如,计时器可以测量在pwm信号的上升边沿与流经谐振回路的给定部件的电流或在谐振回路的给定部件或节点处的电压(例如,流经lc谐振回路的部件中的一个部件的电流或该lc谐振回路的部件中的一个部件处的电压(诸如lc谐振回路的振铃节点处的电压))达到给定阈值时的时刻之间经过的时间。

182.发明人已经观察到,响应于给定异步事件,(多个)上述粗略计数器104或104a/104b以及相位信号φ0...φ

n

‑1可以被用于以高分辨率捕获pwm信号生成器电路的时间信息。

183.具体地,在各种实施例中,计时器电路被配置为响应于这种异步事件,以高分辨率、最小延迟且没有亚稳性问题的情况下以相干方式(例如,相对于pwm信号的上升边沿或

下降边沿和从pll输出的n个相位)存储时间信息和/或相位信息。

184.具体地,在先前实施例中,(多个)计数器104或104a/104b由与单个选定时钟相位相对应的自适应时钟clk_tmr控制,并且针对下一间隔t

on

或t

off

可以使用不同的时钟相位,从而应用微调。因此,计时器应当例如根据时钟循环的数目和相位信息对时间进行采样。

185.图13示出了电路30的第一实施例,该电路30被配置为响应于异步事件(例如,信号ae中的上升(和/或下降)边沿)而确定计数值cv和相位值pv。

186.如前所述,这种异步事件信号ae可以经由比较器电路300生成,该比较器电路300被配置为比较模拟(电压或电流)信号与相应阈值th。

187.具体地,在所考虑的实施例中,电路30从计数器104接收多个相位信号φ0...φ

n

‑1和计数值cnt。

188.在所考虑的实施例中,经由同步链对异步事件信号ae进行采样,例如,使用级联连接的两个(或更多个)触发器ffa和ffb实现的同步链。具体地,在所考虑的实施例中,异步事件信号ae使用相位信号φ0…

φ

n

‑1中的每个相位信号进行采样/与之同步,即,电路30包括针对相位信号φ0…

φ

n

‑1中的每个相位信号的相应同步链ffa0/ffb0、ffa1/ffb1、

……

,其被配置为响应于相应相位信号φ0...φ

n

‑1而对异步事件信号ae进行采样,从而生成异步事件信号ae的相应采样版本/同步版本ae0、ae1、

……

189.在所考虑的实施例中,同步信号ae0、ae1、

……

中的一个同步信号(例如,信号ae0)被提供给寄存器301,以便存储计数器104的计数值cnt(或同样,计数器104a的计数值cnta或计数器104b的计数值cntb),从而在输出处提供计数值cv。

190.而且,各种同步版本ae0、ae1、

……

被提供给电路302,优选地,组合逻辑电路,该电路302被配置为根据同步信号ae0、ae1、

…

的(瞬时)逻辑值生成相位值pv。

191.然而,发明人已经观察到,例如,由于亚稳性和不同路径定时,所以分别存储计数器值cnt和相位状态(如信号ae0、ae1、

……

所指示示的)可能导致错误的计数器和相位配对。例如,即使在使用同步链时,也必须组合信号ae0、ae1、

……

,并且操作也应与计数器104的时钟信号clk_tmr同步。

192.图14和图19示出了被配置为响应于异步事件信号ae而确定计数值cv和/或相位值pv的电路的第二实施例。

193.具体地,图14示出了被配置为确定计数值cv的电路30a的实施例。

194.具体地,在所考虑的实施例中,电路30a包括两个同步级304和306。例如,同步级304和306中的每个同步级可以使用一个或多个触发器来实现。

195.具体地,在所考虑的实施例中,同步级/触发器306被配置为在时钟信号clk_tmr的每个上升边沿处对异步事件信号ae进行采样,例如,时钟信号clk_tmr被连接到同步级/触发器306的时钟输入,从而生成第一同步事件信号ae_rs,并且同步级/触发器304被配置为在时钟信号clk_tmr的每个下降边沿处对异步事件信号ae进行采样,该异步事件信号ae由反相器inv示意性地示出,该反相器inv将时钟信号clk_tmr的反相版本提供给同步级/触发器304的时钟输入,从而生成第二同步事件信号ae_f1。

196.例如,图16示出了两个同步电路304和306的vhdl代码的实施例。

197.具体地,过程“p_async_fllng”对电路304的行为进行建模,而过程“p_async_rsng”对电路304的行为进行建模。

198.通常,过程“p_async_fllng”被配置为响应于时钟信号clk_tmr的下降边沿(由条件clk_tmr

′

event和clk_tmr=

’0’

指示)而将信号cmp_asynch_evnt的值(对应于异步事件信号ae)指派给信号asynch_evnt_ret_fl(表示电路304的输出处的信号ae_fl)。同样,过程“p_async_rsng”被配置为响应于时钟信号clk_tmr的上升边沿(由条件clk_tmr

′

event和clk_tmr=

’1’

指示)而将信号cmp_asynch_evnt的值(对应于异步事件信号ae)指派给信号asynch_evnt_ret_rs(表示电路306的输出处的信号ae_rs)。

199.在各种实施例中,电路304和306也可以支持重置操作。例如,在图16中,过程“p_async_fllng”被配置为当设置了信号s_rst_dump(表示重置信号)时,重置信号asynch_evnt_ret_fl。同样,过程“p_async_rsng”可以被配置为当设置了信号s_rst_dump时,重置信号asynch_evnt_ret_rs。

200.在图14所示的实施例中,在同步级/触发器304和306的输出处的信号被提供给采样电路308,该采样电路308被配置为响应于时钟信号clk_tmr,并且将信号ae_rs/asynch_evnt_ret_rs和ae_fl/asynch_evnt_ret_fl的逻辑值考虑在内,而存储计数器104的计数值cnt(或同样cnta/cntb)。

201.在所考虑的实施例中,当发信号通知异步事件ae时,由电路304/306设置信号ae_rs/asynch_evnt_ret_rs和ae_fl/asynch_evnt_ret_fl中的至少一个信号。

202.具体地,如图15所示,当计数器值cnt在时钟信号clk_tmr的每个上升边沿增加时,存在给定延迟,直到计数器值cnt发生改变为止。

203.因此,当在时钟信号clk_tmr为高的同时(例如,图14中的时刻t2)发生异步事件ae时,信号ae_fl/asynch_evnt_ret_fl将使用时钟信号clk_tmr的下一下降边沿来被设置为高。因此,当在时钟信号clk_tmr的下一上升边沿处对计数值cnt进行采样时,信号ae_rs/asynch_evnt_ret_rs仍被设置为低(由于固有传播延迟)。

204.相反,当在时钟信号clk_tmr为低的同时(例如,图14中的时刻t1)发生异步重置ae时,该事件相对于对计数值进行采样时的时刻t3而在计数值cnt

‑

1处发生。然而,在这种情况下,信号ae_rs/asynch_evnt_ret_rs将在时钟信号clk_tmr的下一上升边沿处被设置为高,而信号ae_fl/asynch_evnt_ret_fl将在时钟信号clk_tmr的下一下降边沿处被设置为高。因此,当在时钟信号clk_tmr的下一上升边沿对计数值cnt进行采样时,电路30a应当的确对值cnt

‑

1进行采样。

205.因此,在各种实施例中,电路30a被配置为:

206.当信号ae_rs/asynch_evnt_ret_rs为低并且信号ae_fl/asynch_evnt_ret_fl为高时,响应于时钟信号clk_tmr的上升边沿而对计数值cnt进行采样;以及

207.当信号ae_rs/asynch_evnt_ret_rs为高并且信号ae_fl/asynch_evnt_ret_fl为高时,响应于时钟信号clk_tmr的上升边沿而对计数值cnt

‑

1进行采样。

208.例如,图17示出了电路308的vhdl代码的实施例,其中过程“p_counter_dump”对相应行为进行建模。

209.例如,在所考虑的实施例中,响应于时钟信号clk_tmr的上升边沿(由条件clk_tmr

′

event和clk_tmr=

’1’

指示),电路310验证信号asynch_evnt_ret_rs(ae_rs)和asynch_evnt_ret_fl(ae_fl)的逻辑值。在信号asynch_evnt_ret_rs(ae_rs)和asynch_evnt_ret_fl(ae_fl)为高的情况下,电路将值tmr_crs

–

1(表示值cnt

–

1)存储到信号s_

tmrcnt_dmp(表示计数值cv)。相反,如果信号asynch_evnt_ret_rs(ae_rs)为低而asynch_evnt_ret_fl(ae_fl)为高,电路将值tmr_crs(cnt)存储到信号s_tmrcnt_dmp(表示计数值cv)。

210.在各种实施例中,电路308还可以支持样本使能信号。例如,在图16中,过程“p_counter_dump”被配置为仅当样本使能信号s_end_dump具有给定逻辑电平(例如,如条件s_end_dump=

’0’

所示,为低)时,才存储值tmr_crs

–

1或tmr_crs。而且,一旦存储了值tmr_crs

‑

1或tmr_crs,该信号的逻辑值就被反相(例如,如操作s_end_dump<=

’1’

)所示,为高)。

211.在各种实施例中,电路308可以被配置为当设置了信号s_rst_dump(再次表示重置信号)时,重置信号s_tmrcnt_dmp和s_end_dump。

212.因此,在各种实施例中,电路30a被配置为接收时钟信号clk_tmr,诸如关于图5至图12的pwm生成器电路所描述的时钟信号clk_tmr,其中该时钟信号用于增加计数器104。第一同步电路304用于响应于时钟信号clk_tmr的下降边沿而对异步事件信号ae进行同步/重新计时,从而生成第一信号ae_f1。第二同步电路306用于响应于时钟信号clk_tmr的上升边沿而对异步事件信号ae进行同步/重新计时,从而生成第一信号ae_rs。

213.采样电路308例如经由组合逻辑电路对信号ae_fl和ae_rs进行阐述,以确定:

214.是否发生了异步事件ae;以及

215.基于信号ae_fl和ae_rs,异步事件ae是在时钟信号clk_tmr为高还是为低时发生。

216.在信号ae_fl和ae_rs两者均为高的情况下,计数器值cnt被存储为信号cv,并且如果仅信号ae_fl为高,则计数器值cnt减一(cnt

‑

1)被存储为信号cv。

217.如前所述,图19示出了被配置为执行相位检测/采样的电路30b。

218.在所考虑的实施例中,电路30b包括第一水平的n个触发器ffa0..ffa

n

‑1,其中触发器ffa0..ffa

n

‑1中的每个触发器被配置为响应于异步事件信号ae(即,异步事件信号ae应用于触发器ffa

i

的时钟输入),对时钟相位φ0...φ

n

‑1(即,其中0≤i≤(n

‑

1)的相位φ

i

被应用于触发器ffa

i

的数据输入)进行采样。

219.在所考虑的实施例中,电路30b包括第二水平的n个触发器ffb0..ffb

n

‑1,其被配置为响应于相应相位φ0...φ

n

‑1的下降边沿,存储在触发器ffa0..ffa

n

‑1中的相应触发器的输出处的信号,即,给定触发器ffa

i

的输出被应用于/耦合到相应触发器ffb

i

的数据输入,以及相应时钟相位φ

i

的反相版本(经由反相器inv0..inv

n

‑1所示意性示出的)被应用于触发器ffb

i

的时钟输入,从而在触发器ffb0..ffb

n

‑1的输出处生成相应信号cmp_ph(0)

…

cmp_ph(n

‑

1)。

220.具体地,在各种实施例中,触发器ffb0..ffb

n

‑1被配置为当在相应触发器ffa0..ffa

n

‑1的输出处的信号为高时,仅存储在相应触发器ffa0..ffa

n

‑1的输出处的信号。因而,一旦在触发器ffa

i

的输出处的信号被设置为高,则响应于相应相位φ

i

的下一下降边沿,在相应触发器ffb

i

处的输出就被设置为高,并且当在触发器ffa

i

的输出处的信号被设置为低时,触发器ffb

i

也保持为高。例如,为此,针对每个触发器ffb0..ffb

n

‑1,在图19中示意性地示出了相应逻辑or门or0..or

n

‑1,其中每个逻辑or门or

i

在输入处接收在相应触发器ffa

i

的输出处的信号和在相应触发器ffb

i

的输出处的信号,并且逻辑or门or

i

的输出被连接到相应触发器ffb

i

的输入。

221.在所考虑的实施例中,电路30b还包括第三水平的n个触发器ffc0..ffc

n

‑1,其被配

置为响应于相应相位φ0...φ

n

‑1的上升边沿,存储在触发器ffb0..ffb

n

‑1的输出处的两个相邻信号cmp_ph(0)...cmp_ph(n

‑

1)之间的比较的结果。具体地,给定触发器ffc

i

在时钟输入处接收相应相位φ

i

,并且在数据输入处接收比较信号,并且在输出处提供相应信号cmp_ph_fin(i)。

222.具体地,在所考虑的实施例中,每个比较信号指示相应信号cmp_ph(i)是否为低(0≤i≤n

‑

1),即,反相版本inv(cmp_ph(i))为高,并且相应信号cmp_ph(i

‑

1)为高。具体地,根据信号cmp_ph(0)和cmp_ph(n

‑

1)生成第一比较信号。例如,可以经由逻辑and门and0..and

n

‑1生成比较信号,每个逻辑and门and

i

在输入处接收信号cmp_ph(i

‑

1)(或当i=0时,为cmp_ph(n

‑

1))以及信号cmp_ph(i)的反相版本。

223.因此,本质上前两个级ffa和ffb生成同步触发信号cmp_ph(0)

…

cmp_ph(n),其中

224.每个触发器ffa

i

响应于在异步事件信号ae中的上升边沿,对相应时钟相位φ

i

进行采样;以及

225.当响应于相应时钟相位φ

i

的下降边沿,第一级的相应触发器ffa

i

的输出处的信号为高时,每个触发器ffb

i

将其输出设置为高。

226.相反,第三级ffc确定相位值pv。具体地,如图18所示,当生成异步事件ae时,只有一个单个相邻时钟相位集合,其中先前φ

i

‑1为高,而随后φ

i

为低。例如,考虑时刻t1,时钟相位φ1为高,时钟相位φ2为低。因此,第三级针对每个索引i验证信号cmp_ph(i

‑

1)和cmp_ph(i)对/集合,其中信号cmp_ph(i

‑

1)为高而信号cmp_ph(i)为低,其中值i表示相位值pv。具体地,在所考虑的实施例中,第三相位生成信号cmp_ph_fin(0)

…

cmp_ph_fin(n

‑

1),其中仅信号cmp_ph_fin(0)

…

cmp_ph_fin(n

‑

1)中的一个信号被设置为高。因此,本质上信号cmp_ph_fin(0)

…

cmp_ph_fin(n

‑

1)表示索引i/相位值pv的独热编码。

227.通常,只要异步事件信号ae和时钟相位φ0...φ

n

‑1不同步,前两个级都可能引入亚稳性。然而,第三级的比较机构对于解决这种潜在的亚稳性问题也很有用。实际上,通过构造,仅一个单个信道上cmp_ph(i)可以具有亚稳性。假设结构完美平衡,则该亚稳值有望在半个相位时钟时段内被求解,从而在一个and门对的输入处达到相同逻辑值,其中该相同逻辑值被有效使用,从而允许最后一个触发器ffc水平存储正确值。

228.在所考虑的实施例中,寄存器ffb和ffc被用作双边沿同步器;一般而言,同步链ffb

i

和ffc

i

中的每个同步链也可以使用级联连接的更多触发器来实现。

229.在各种实施例中,寄存器ffa、ffb和ffc被配置为响应于诸如先前所提及的信号s_rst_dump的重置信号rst而被重置。通常,这种重置信号rst/s_rst_dump可以由任何合适电路312生成,并且本质上激活下一异步事件ae的检测。例如,在所考虑的实施例中,寄存器响应于信号rst的下降边沿而重置。

230.如前所述,在各种实施例中,计数器电路104(或同样,104a和104b)可以使用前面所述的自适应时钟信号clk_tmr,其中该时钟信号clk_tmr(在诸如接通持续时间t

on

和/或关断持续时间t

off

之类的给定时间段期间)与时钟相位φ0...φ

n

‑1中的一个时钟相位相对应。

231.因此,如图20所示,电路30可以包括电路314,其被配置为根据由计数器104所使用的时钟相位φ0...φ

n

‑1来计算相位差值pv

′

,例如,由选择信号sel1和由级ffc所检测的相位值pv所指示。

232.本公开的各种实施例涉及一种被配置为生成相位值的时间测量电路。

233.在各种实施例中,时间测量电路包括多相时钟生成器,该多相时钟生成器被配置为生成给定数目n个相移时钟相位的序列,该相移时钟相位具有相同的时钟时段并且相移了对应于时钟时段的分数1/n的时间,其中相移时钟相位中的一个时钟相位表示参考时钟信号。

234.在各种实施例中,时间测量电路还包括节点,其用于接收异步事件信号;以及相位采样电路,其被配置为生成相位值,该相位值指示在参考时钟信号的边沿与异步事件信号被设置时的时刻之间经过的时钟时段的分数1/n的数目。

235.在各种实施例中,相位采样电路包括各种子电路。

236.具体地,在各种实施例中,第一子电路包括针对相移时钟相位中的每个相移时钟相位的相应第一触发器,第一触发器中的每个第一触发器被配置为响应于异步事件信号而对相应相移时钟相位进行采样,从而确定相应第一控制信号,该相应第一控制信号指示在异步事件信号被设置时的时刻处,相应时钟相位是被设置为高还是被设置为低。

237.在各种实施例中,第二子电路包括针对相移时钟相位中的每个相移时钟相位的相应第二触发器,第二触发器中的每个第二触发器被配置为响应于相应相移时钟相位而对相应第一控制信号进行采样,从而确定与相应第一控制信号的同步版本相对应的相应第二控制信号。

238.例如,在各种实施例中,第一触发器中的每个第一触发器被配置为响应于异步事件信号的上升边沿而对相应相移时钟相位进行采样,以及第二触发器中的每个第二触发器被配置为响应于相应相移时钟相位的下降边沿而对相应第一控制信号进行采样。

239.在各种实施例中,时间测量电路可以包括针对相移时钟相位中的每个相移时钟相位的相应逻辑or门,每个逻辑or门在输入处接收由相应第一触发器所提供的相应第一控制信号和由相应第二触发器所提供的相应第二控制信号,从而确定相应控制信号,以及其中第二触发器中的每个第二触发器被配置为对这些控制信号中的一个控制信号进行采样,由此第二触发器中的每个第二触发器仅当相应第一控制信号被设置为高时,才对相应第一控制信号进行采样。

240.在各种实施例中,第三子电路被配置为将相移时钟相位中的每个相移时钟相位与另一时钟相位相关联,该另一时钟相位与在相应时钟相位之前的相移时钟相位序列中的相移时钟相位相对应,其中时间对应于时钟时段的分数1/n。而且,第三子电路确定针对相移时钟相位中的每个相移时钟相位的相应第三控制信号,该信号指示:

241.与相应相移时钟相位相关联的第二控制信号是否指示在设置异步事件信号时的时刻处,相应相移时钟相位被设置为低,以及

242.与相应另一时钟相位相关联的第二控制信号是否指示在设置异步事件信号时的时刻处,相应另一时钟相位被设置为高。

243.例如,在各种实施例中,第三子电路包括针对相移时钟相位中的每个相移时钟相位的相应逻辑and门,每个逻辑and门在输入处接收与相应相移时钟相位相关联的第二控制信号的反相版本,以及与相应另一时钟相位相关联的第二控制信号,从而生成相应第三控制信号。

244.在各种实施例中,第四子电路包括针对相移时钟相位中的每个相移时钟相位的相应第三触发器,第三触发器中的每个第三触发器被配置为响应于相应相移时钟相位,对相

应第三控制信号进行采样,从而确定与相应第三控制信号的同步版本相对应的相应第四控制信号。例如,第三触发器中的每个第三触发器可以被配置为响应于相应相移时钟相位的上升边沿,对相应第三控制信号进行采样。

245.因此,如下文所更详细描述的,仅设置第四控制信号中的一个第四控制信号,即,第四控制信号表示相位值的独热编码。

246.而且,在参考时钟信号根据选择信号而在相移时钟相位之中进行选择的情况下,可以根据第四控制信号和选择信号来确定相位值。

247.一般而言,时间测量电路不仅可以监测时钟循环的分数,而且还可以监测自给定事件以来经过的时钟循环的数目。在这种情况下,时间测量电路可以包括计数器电路,其被配置为响应于参考时钟信号而增加计数值;以及计数器采样电路,其被配置为通过对计数器电路的计数值进行采样来生成经采样计数值。

248.例如,在各种实施例中,计数器采样电路包括:

249.第一采样电路,其被配置为响应于参考时钟信号的上升边沿来对异步事件信号进行采样,从而生成第一经同步异步事件信号;

250.第二采样电路,其被配置为响应于参考时钟信号的下降边沿来对异步事件信号进行采样,从而生成第二经同步异步事件信号;以及

251.采样电路,其被配置为响应于参考时钟信号的上升边沿,根据第一经同步异步事件信号和第二经同步异步事件信号来存储计数器电路的计数值或减一的计数器电路的计数值,从而生成经采样计数值。

252.如之前所提及的,这种时间测量电路在包括pwm信号生成器电路的系统中是有用的,该pwm信号生成器电路被配置为例如根据计数器电路的计数值以及可选地还有相移时钟相位生成脉冲宽度调制信号。例如,在这种情况下,经采样计数值和相位值可以指示时钟循环的数目以及在脉冲宽度调制信号的边沿与异步事件信号被设置时的时刻之间经过的参考时钟信号的时钟循环的分数1/n的数目。

253.根据一个或多个实施例,提供了一种时间测量电路,其具有在以下描述中所阐述的独特元件。实施例还涉及一种包括pwm信号生成器电路和时间测量电路的对应系统以及一种对应集成电路。

254.当然,在不损害本公开的原理的情况下,构造和实施例的细节可以相对于仅通过示例在本文中描述和图示的内容而发生大范围变化,而不因此脱离本公开的范围,如由随后权利要求所定义。

255.上述各种实施例可以组合以提供其他实施例。可以根据上述具体实施方式对实施例进行这些和其他改变。一般而言,在以下权利要求书中,所使用的术语不应解释为将权利要求书限制为说明书和权利要求书中所公开的特定实施例,而是应当解释为包括所有可能实施例以及这些权利要求所享有权利的全部范围的等同物。因而,权利要求不受公开内容的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1