一种绝对式编码器解码系统实现方法与流程

1.本发明属于电控技术领域中的高精度伺服系统编码器技术领域,具体是指一种绝对式编码器解码系统实现方法。

背景技术:

2.目前,在高精度伺服系统中,位置反馈环节的检测精度直接影响伺服系统的性能。常用的位置检测装置包括有光电编码器和旋转变压器。而旋转变压器因抗电磁干扰性能差、解码电路复杂,现在已逐渐被具有精度高、惯量小、稳定性好的优点的光电编码器所取代。因此光电编码器,在高精度伺服系统中得到了广泛应用。

3.光电编码器在使用时,其对应的解码系统是性能的核心之一;业内各企业都有开发自己的解码系统。比如多摩川公司为自己的光电编码器开发了专门的解码芯片,其串行输出的绝对式编码器内部多采用adm485或类似的芯片作为输出,因此用户需要在解码板上采用adm485兼容的芯片作为编码器与解码芯片的接口电路,这增加了解码系统的成本和复杂程度。比如在海德汉公司的增量式编码器的解码系统中,则是采用复杂可编程逻辑器件cpld(complex programmable logic device)和现场可编程门阵列fpga(field-programmable gate array),通过a/d采样后给fpga,利用cordic算法将正余弦信号解码;这种解码方法在光电码盘和增量式编码器的解码中运用广泛。本专利申请的发明人通过实践与研究发现,这种将cpld或fpga用于绝对式编码器的解码方法不但增加了解码系统的成本,也增加了系统编程的复杂性,如果能采用更简单可靠的解码系统则更有利于整个伺服系统的稳定。

4.综上所述,目前缺少一种系统结构更简单、成本更低、运行更加稳定可靠的用于高精度伺服系统的编码器解码系统实现方法。

技术实现要素:

5.本发明要解决的技术问题是,提供一种系统结构更简单、成本更低、运行更加稳定可靠的用于高精度伺服系统的绝对式编码器解码系统实现方法。

6.为解决上述技术问题,本发明提供的技术方案为:一种绝对式编码器解码系统实现方法,解码系统对应的编码器为绝对式编码器;解码系统采用数字信号处理器(dsp)作为核心控制单元,通过向数字信号处理器(dsp)中加载解码程序完成解码工作;所述的解码系统还包括解码电路和电平转换传输电路;解码电路用于为核心控制单元提供数据采集与处理支撑,电平转换传输电路用于转换电平信号;控制单元与其他单元之间的接口电路严格遵循endat接口协议的时序要求和数据帧格式进行设计;所述的解码系统采用rs485通讯接口在解码系统发出的同步时钟激励下与编码器之间进行数据的双向传输。

7.作为优选,所述的电平转换传输电路用于将绝对式编码器输出的+5v电平信号转换成可以输入数字信号处理器的+3.3v电平信号;同时将数字信号处理器(dsp)输出的同步时钟信号和数据传递给编码器,所述的电平转换传输电路的主芯片采用型号为

sn74lvc4245a的芯片。

8.作为优选,所述的rs485通讯接口采用rs485通信的半双工低功率收发器sn65hvd485ed芯片与编码器进行数据传输;芯片中包含一个驱动器和一个接收器,且能以2.5mbps速率进行传输,同时还采用rs485专用的差分驱动器sn75als191芯片通过数字信号处理器(dsp)控制为编码器提供同步差分时钟信号。

9.作为优选,编码器与rs485芯片发送接收数据时,采用高速光耦芯片tlp113进行电气隔离,当数字信号处理器(dsp)向rs485芯片发出spiste信号,使de为固定高电平时,此时sn65hvd485ed芯片为rs485差分驱动器,将数字信号处理器(dsp)发出的spisimo信号通过di端口经b、a端转化为差分的data+和data-信号;当接收编码器数据信息时,数字信号处理器(dsp)发出spiste信号使re为固定低电平,此时sn65hvd485ed芯片为rs485差分接收器,将编码器传回的data+和data-位置信息经a、b端转换成串行数据通过ro端输入给数字信号处理器(dsp)进行解码。

10.作为优选,编码器的时钟信号是由数字信号处理器(dsp)发出的spiclk信号经过采用rs485单工差分驱动器的sn75als191芯片产生差分的clock+和clock-信号。

11.采用上述方法后,本发明具有如下有益效果:本发明提出的一种绝对式编码器解码系统方法利用dsp的spi接口实现了基于endat2.2协议的绝对式光电编码器的绝对位置值解码,在硬件设计中没有采用昂贵的专用解码芯片,也没有采用额外的cpld(fpga)来处理编码器数据,通过半双工和单工的rs485来完成与编码器的通信和数据交换,大大简化系统设计,降低产品成本,并且实现对装有绝对位置值传感器伺服电机的高精度控制。采用软件的方式处理编码器数据,通过crc检验提高了传输可靠性。不但可满足系统获取位置信息的需要,还可以灵活地对通信错误进行诊断和处理。可以避免程序长时间的延时,还可以在对电机进行解耦之前得到编码器的位置信息。诊断方法物理概念清晰,实现简单,具有良好的应用价值。

12.综上所述,本发明提供了一种系统结构更简单、成本更低、运行更加稳定可靠的用于高精度伺服系统的绝对式编码器解码系统实现方法。

附图说明

13.图1是本发明中涉及的endat接口编码器数据采集原理图。

14.图2是本发明中涉及的绝对式编码器接口信号分配图。

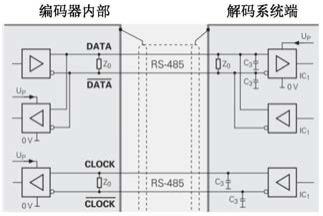

15.图3是本发明中编码器与解码系统的通信接口图。

16.图4是本发明中涉及的基于endat2.2协议的通信接口时序图。

17.图5是本发明中解码系统的输入电路图。

18.图6是本发明中电平转换传输电路原理图。

19.图7是本发明中的485接口电路原理图。

20.图8是本发明中解码系统的电气连接图。

21.图9是本发明中spi发送中断程序框图。

22.图10是本发明中spi接收中断程序框图。

具体实施方式

23.下面结合附图对本发明做进一步的详细说明。

24.一种绝对式编码器解码系统实现方法,解码系统对应的编码器为绝对式编码器;解码系统采用数字信号处理器(dsp)作为核心控制单元,通过向数字信号处理器(dsp)中加载解码程序完成解码工作;所述的解码系统还包括解码电路和电平转换传输电路;解码电路用于为核心控制单元提供数据采集与处理支撑,电平转换传输电路用于转换电平信号;控制单元与其他单元之间的接口电路严格遵循endat接口协议的时序要求和数据帧格式进行设计;所述的解码系统采用rs485通讯接口在解码系统发出的同步时钟激励下与编码器之间进行数据的双向传输。

25.作为优选,所述的电平转换传输电路用于将绝对式编码器输出的+5v电平信号转换成可以输入数字信号处理器的+3.3v电平信号;同时将数字信号处理器(dsp)输出的同步时钟信号和数据传递给编码器,所述的电平转换传输电路的主芯片采用型号为sn74lvc4245a的芯片。

26.作为优选,所述的rs485通讯接口采用rs485通信的半双工低功率收发器sn65hvd485ed芯片与编码器进行数据传输;芯片中包含一个驱动器和一个接收器,且能以2.5mbps速率进行传输,同时还采用rs485专用的差分驱动器sn75als191芯片通过数字信号处理器(dsp)控制为编码器提供同步差分时钟信号。

27.作为优选,编码器与rs485芯片发送接收数据时,采用高速光耦芯片tlp113进行电气隔离,当数字信号处理器(dsp)向rs485芯片发出spiste信号,使de为固定高电平时,此时sn65hvd485ed芯片为rs485差分驱动器,将数字信号处理器(dsp)发出的spisimo信号通过di端口经b、a端转化为差分的data+和data-信号;当接收编码器数据信息时,数字信号处理器(dsp)发出spiste信号使re为固定低电平,此时sn65hvd485ed芯片为rs485差分接收器,将编码器传回的data+和data-位置信息经a、b端转换成串行数据通过ro端输入给数字信号处理器(dsp)进行解码。

28.作为优选,编码器的时钟信号是由数字信号处理器(dsp)发出的spiclk信号经过采用rs485单工差分驱动器的sn75als191芯片产生差分的clock+和clock-信号。

29.进一步结合附图1到附图10,本发明的具体实施方法如下。

30.在具体实施前,首先需要说明下绝对式光电编码器的相关特性,绝对式光电编码器具有一个endat2.2协议的全双工同步串行接口,提供13位绝对位置值,控制器与编码器之间通过(data+,data-,clock+,clock-)4根信号线交换数据。在控制时钟和模式指令激励下,位置信息被同步传输。双向endat2.2接口的时钟频率已达到16mhz,能满足高动态性能控制系统的要求,是基于rs-485电气标准的传输速度最快的纯数字位置编码器接口。endat接口编码器数据采集原理如附图1所示。由附图1我们知道编码器的接口为8芯单屏蔽电缆,其实际的接口和信号分配如附图2所示,由于编码器的两个up和0v信号已经内部连接,因此解码系统只需为其提供一组对+5v和0v的电源,即可使编码器正常工作。

31.结合上述背景,由于在本解码系统中无需对附加的增量信号a+,a-,b+,b-进行解码,因此我们只需编码器中的4条信号线和2条电源线即可完成与解码系统的通信,数据传输保持与解码系统的时钟信号同步。由此,我们设计了对应通信接口,如附图3所示。解码系统发送同步时钟脉冲用于编码器数据的同步传输,时钟脉冲相对于编码器端的时钟频率是

有电路传输延时的。传输周期从时钟的第一个下降沿开始,编码器保存测量值并计算位置值。因此,如附图4所标示,两个时钟脉冲(2t)之后,后续解码系统下降沿发送位置值模式指令“000111”,要求编码器发送绝对位置值,此时模式指令便随海德汉编码器的上升沿接收,然后经过若干个时钟脉冲(附图中以4个上升沿加箭头示意),解码系统的开始信号到前一个时钟上升沿用时td,编码器计算完绝对位置值后,从开始位向解码系统传输数据,接着是错误位,用于监测故障。然后编码器从最低有效位(lsb)开始传输绝对位置值,其长度取决于所用编码器,在系统中所用编码器绝对位置值长度为13位。位置值的传输以循环冗余校验(crc)结束。数据字结尾处,时钟信号必须置为高电平。10~30μs后或1.25~3.75μs(endat2.2可用参数调整的恢复时间tm)后,数据信号返回低电平,时钟信号启动下一次的数据传输。

32.本发明编码器的解码系统主要由dsp作为核心控制单位和解码电路以及电平转换电路组成,根据endat接口协议和电路电气特性自行设计接口电路进行数据采集与处理,严格遵循协议的时序要求和数据帧格式。通过rs485(差分信号)标准的收发元件,在解码系统发出的同步时钟激励下,数据(位置值和参数)在编码器和解码系统之间双向传输,附图5为解码系统输入电路。由于绝对式编码器的输出信号是符合rs485协议的+5v电平,因而需将其转换成可以输入dsp的+3.3v电平。同时,需要将dsp输出的同步时钟信号和数据发送给编码器,本专利申请中采用sn74lvc4245a芯片,其中rs485芯片电平转换状态表如下表所示。

[0033][0034]

dsp的spi接口信号端与sn74lvc4245a的b端数据总线连接,如附图6所示,因此,在b端的供电端vcb采用+3.3v供电,而在sn74lvc4245a的a端数据总线与解码电路高速光耦端连接,在a端的供电端vca采用+5v供电。当oe保持低电平时,且dir为低电平时,b端数据总线的数据向a端发送,此时,spiste作为通用i/o口使rs485芯片的方向控制数据的发送和接收,它使后续解码电路能够开始传输数据给dsp,spisimo为dsp相解码电路发送数据端,而spiclk为dsp发送的同步时钟信号。当oe保持低电平时,且dir为高电平时,a端数据总线的数据向b端发送,此时spisomi为编码器向dsp传输的串行数据,供dsp解析。经过电平转换之后,选用rs485通信的半双工低功率收发器sn65hvd485ed芯片与编码器进行数据传输。芯片中包含一个驱动器和一个接收器,且能以2.5mbps速率进行传输。选用rs485专用差分驱动器sn75als191芯片,通过dsp经该驱动器为编码器提供同步差分时钟信号。解码系统如附图7与附图8所示,经过实际分析,相比昂贵的全双工rs485专用解码芯片或额外的cpld(fpga)来处理编码器数据接收,这样使得系统结构更加紧凑,成本更低廉,且满足同样高质量的解码效果,保证了整个伺服系统达到了高性能的水准。

[0035]

在该解码系统中,采用的芯片sn65hvd485ed功能表如下表所示:

[0036][0037]

编码器与rs485芯片发送接收数据,同时为了减少电路前后的干扰,我们采用了高速光耦芯片tlp113实现电气隔离,其传输速率可达到10mbd(typ),当dsp向rs485芯片发出spiste信号,使de为固定高电平时,此时sn65hvd485ed为rs485差分驱动器,将dsp发出的spisimo信号通过di端口经b、a端转化为差分的data+和data-信号;当接收编码器数据信息时,dsp发出spiste信号使re为固定低电平,此时sn65hvd485ed为rs485差分接收器,将编码器传回的data+和data-位置信息经a、b端转换成串行数据通过ro端输入给dsp进行解码。同时编码器的时钟信号是由dsp发出的spiclk信号经过采用rs485单工差分驱动器sn75als191芯片产生差分的clock+和clock-信号,经实际验证半双工低功率收发器和单工差分线路驱动器的组合抗噪声干扰能力很强。

[0038]

具体实施时,本发明中涉及的高性能伺服系统绝对式编码器解码系统软件实现包括以下内容。解码系统中获取编码器的位置数据主要通过dsp的spi接口,在外设初始化程序中,包含了spi的初始化程序,其程序代码如下:

[0039]

void spi_init()

[0040]

{

[0041]

spiaregs.spiccr.bit.spiswreset=0;

[0042]

//复位spi接口

[0043]

spiaregs.spiccr.all=0x000f;//在spiclk的上//升沿传送数据且在下降沿锁存输入,当无spi//数据发送时,spiclk处于低电平。数据长度选//择16位。

[0044]

spiaregs.spictl.all=0xc;//spiclk信号延迟//半个周期,使能主动工作模式,禁止talk,禁//止中断使能

[0045]

spiaregs.spists.all=0x0000;

[0046]

//spi状态寄存器清零

[0047]

spiaregs.spibrr=0x12;//lspclk低速时钟频率//为37.5mhz时波特率约为1.97mhz

[0048]

spiaregs.spifftx.all=0xc028;//spi fifo增强//使能,设置tx fifo中断使能级别为8

[0049]

spiaregs.spiccr.all=0x8f;//使能spi接口

[0050]

}

[0051]

dsp发送模式指令给编码器是通过中断方式实现的,通过spi的程序初始化设置,设置了数据长度和通信速率,使能增强型fifo发送和接收,采用8级中断发送和接收数据,即每发送或接收完8个数据后触发一次中断,spi发送中断程序流程如附图9所示,具体中断程序如下:

[0052]

interrupt void spitxinta_isr(void)

[0053]

//spi发送数据中断程序

[0054]

{

[0055]

if(count_spi_in==0)

[0056]

//当count_spi_in=0时开始发送模式指令

[0057]

{

[0058]

gpiodataregs.gpfset.bit.gpiof3=1;

[0059]

//将spiste作为通用i/o口设置为高电平,使//收发器sn65hvd485ed为驱动器发送模式指令

[0060]

spiaregs.spitxbuf=0xc7ff;//给编码器发送模//式“000111”要求编码器发送绝对位置值

[0061]

spiaregs.spitxbuf=0;//为了继续保持spiclk时//钟信号,给发送寄存器中放入零数值

[0062]

spiaregs.spitxbuf=0;//为了继续保持spiclk时//钟信号,给发送寄存器中放入零数值

[0063]

count_spi_in=1;

[0064]

//当count_spi_in=1时禁止发送模式指令

[0065]

count_spi_out=0;

[0066]

//当count_spi_out=0时可以接收编码器的数据

[0067]

}

[0068]

spiaregs.spifftx.bit.txffintclr=1;

[0069]

//清除发送中断标志位

[0070]

piectrlregs.pieack.all|=pieack_group6;//spi中断使能

[0071]

spiaregs.spifftx.all&=(~0x0020);

[0072]

//spi fifo使能,设置tx fifo中断使能级别为8

[0073]

}

[0074]

当dsp完成指令模式的发送中断后,同样需要通过中断方式来接收数据,spi接收中断信号到来,dsp就进入中断服务子程序,将接收到的数据存放在spirxbuf中。当所有数据传输完成后,将这些数据赋给相应的变量。这里要注意的是,dsp的spirxbuf是16位数据,而编码器发送的数据是13位,所以在dsp接收到数据以后需要做处理,把低位到高位发送的绝对位置值可以通过查表转换成实际的数据格式。中断程序流程如图10所示,具体程序代码如下:。

[0075]

[0076]

[0077][0078]

本专利申请中涉及的技术术语的名词解释如下:

[0079]

endat接口是heidenhain专为编码器设计的数字式、全双工同步串行的数据传输协议。

[0080]

spi是串行外设接口(serial peripheral interface)。

[0081]

数字信号处理(digital signal processing,简称dsp)。

[0082]

cpld(complex programmable logic device)复杂可编程逻辑器件。

[0083]

fpga(field-programmable gate array)现场可编程门阵列。

[0084]

通过实践证明,本发明中提出的绝对式编码器解码系统实现方法利用dsp的spi接口实现了基于endat2.2协议的绝对式光电编码器的绝对位置值解码,从硬件设计中未采用昂贵的专用解码芯片,也没有采用额外的cpld(fpga)来处理编码器数据,通过半双工和单工的rs485来完成与编码器的通信和数据交换,大大简化系统设计,降低产品成本,并且实现对装有绝对位置值传感器伺服电机的高精度控制。采用软件的方式处理编码器数据,通过crc检验提高了传输可靠性。不但可满足系统获取位置信息的需要,还可以灵活地对通信错误进行诊断和处理。可以避免程序长时间的延时,还可以在对电机进行解耦之前得到编码器的位置信息。诊断方法物理概念清晰,实现简单,具有良好的应用价值。

[0085]

以上对本发明及其实施方式进行了描述,该描述没有限制性,附图中所示的也只是本发明的实施方式之一,实际的方式并不局限于此;比如可以选用fpga或cpld细分电路进行解码来实现硬件电路,还可以选择绝对位置值精度更高的编码器满足解码精度要求。总而言之如果本领域的普通技术人员受其启示,在不脱离本发明创造宗旨的情况下,不经创造性的设计出与该技术方案相似的结构方式及实施例,均应属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1