基于卷积神经网络的RISC-V协处理系统和方法与流程

基于卷积神经网络的risc-v协处理系统和方法

技术领域

1.本发明涉及数据处理技术领域,具体是指一种基于卷积神经网络的risc-v协处理系统和方法

背景技术:

2.现有卫星的在轨道处理系统以固定算法的硬件优化为核心,设计难度大,通用性差,功能升级困难。同时由于资源和成本的约束,在轨道实时数据处理能力的限制。以上两点导致内部最终用户获取情报产品的速度时间也只能在小时级,与国际先进水平仍存在差距,无法满足日益增长的军事与民用卫星侦测需求。随着集成芯片产业的快速发展,人工智能、深度学习与基于嵌入式系统的实时识别已经在民用应用中得到实现,具有人工智能云检功能的嵌入式实时处理相机是未来星载相机发展的重要方向。

3.星上实时智能云检测方法是在地面,首先通过对多种卫星的不同传感器所获得的遥感图像中云的空间纹理及统计特征进行分析,建立云特征模型、利用分类学习算法对样本进行分类训练。在轨验证期间,软件将对空域卷积去除噪声,然后突出云的边缘特征,接着对图像进行纹理和统计特征提取,根据图像云覆盖率、云厚度以及云破碎度对图像质量进行综合评价,剔除云层遮挡的无效数据。所以在星上云检工作中,其主要的算法核心是卷积神经网络运算以及其变形的算法u-net神经网络。

4.目前cnn或者u-net网络主要依靠大规模的矩阵运算提取目标特征值并进行分类与分割处理,其主要瓶颈在于卷积层消耗了大量的运算资源与存储资源,且市面上通用处理器未对该类运算做加速处理。

技术实现要素:

5.基于以上技术问题,本发明提供了一种基于卷积神经网络的risc-v协处理系统和方法,解决了现有单处理器系统进行卷积运算时,运算效率低、存储空间占用大的问题。

6.为解决以上技术问题,本发明采用的技术方案如下:

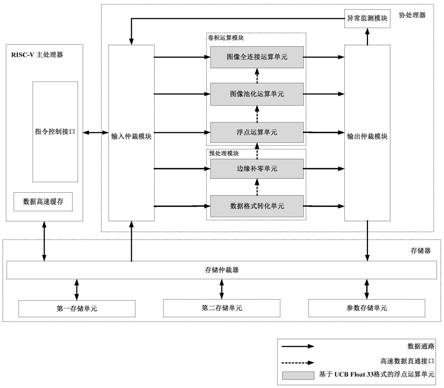

7.一种基于卷积神经网络的risc-v协处理系统,包括存储器、risc-v主处理器和协处理器;存储器用于存储数据,存储器与risc-v主处理器、协处理器连接,risc-v主处理器和协处理器可对存储器内数据进行读写;risc-v主处理器用于发送risc-v功能指令;协处理器用于接收risc-v功能指令,根据接收到的risc-v功能指令搭建卷积神经网络,从存储器中读取图像数据,基于卷积神经网络对图像数据进行运算处理得到输出数据,将输出数据存入存储器。

8.进一步的,协处理器包括预处理模块、卷积运算模块、输入仲裁模块和输出仲裁模块;预处理模块包括数据格式转换单元和边缘补零单元,卷积运算模块包括浮点运算单元、图像池化运算单元和图像全连接运算单元;输入仲裁模块用于对接收的控制信号和数据信号进行仲裁,将接收的控制信号和数据信号分发到数据格式转换单元、边缘补零单元、浮点运算单元、卷积运算单元、图像池化运算单元或图像全连接运算单元;输出仲裁模块用于对

输出的控制信号和数据信号进行仲裁,将输出的控制信号和数据信号分发到存储器或异常监测模块;异常监测模块用于对输出的数据信号进行实时监测;异常监测模块的输入端口与输出仲裁模块连接,其输出端口与输入仲裁模块连接。

9.进一步的,数据格式转换单元用于对图像数据进行格式转换,边缘补零单元用于对图像数据进行边缘补零。

10.进一步的,浮点运算单元采用ucb float 33位格式编译运行,浮点运算单元用于将ieee float 32位浮点数格式转换为ucb float 33位进行运算和将ucb float 33位浮点数格式转换为ieee float 32位进行存储。

11.进一步的,risc-v功能指令包括第一指令、第二指令、第三指令、第四指令和第五指令;第一指令用于配置图像数据格式转换参数,第二指令用于配置图像数据边缘补零参数,第三指令用于配置图像数据卷积运算参数,第四指令用于配置图像数据池化运算参数,第五指令用于配置图像数据全连接运算参数。

12.进一步的,图像数据经数据格式转换单元格式转换后,写回存储器的存储单元为边缘补零单元读取数据的单元;图像数据经边缘补零单元边缘补零后,写回存储器的存储单元为卷积运算单元读取数据的单元;图像数据经卷积运算单元卷积运算后,写回存储器的存储单元为图像池化运算单元读取数据的单元;图像数据经图像池化运算单元池化运算后,写回存储器的存储单元为图像全连接运算单元或者边缘补零单元读取数据的单元。

13.进一步的,存储器包括存储模块和存储仲裁模块;存储模块包括第一存储单元和第二存储单元,第一存储单元和第二存储单元用于乒乓读写,存储仲裁模块用于对存储模块读写的数据进行仲裁分发。

14.进一步的,存储模块还包括参数存储单元,参数存储单元用于预加载卷积神经网络的训练参数数据,训练参数数据包括权重数据和偏置数据。

15.进一步的,risc-v主处理器通过c语言或汇编语言将risc-v功能指令封装为api函数形式传递给协处理器,协处理器具有相应的api函数接口。

16.一种基于卷积神经网络的risc-v协处理方法,方法基于上述的基于卷积神经网络的risc-v协处理系统,包括:

17.risc-v主处理器向协处理器发送risc-v功能指令;

18.协处理器接收risc-v功能指令,根据接收到的risc-v功能指令搭建卷积神经网络,从存储器中读取图像数据,基于卷积神经网络对图像数据进行运算处理得到输出数据,将输出数据存入存储器;

19.risc-v主处理器从存储器中读取输出数据进行后续处理。

20.与现有技术相比,本发明的有益效果是:

21.本发明设计自主可控的高速可配置处理器,配合星上实时处理软硬件系统,颠覆了现有卫星在轨处理系统以固定算法的硬件优化为核心的设计方案,可以实现空间多源异构数据的快速融合与在轨智能处理,显著提高空间海量数据的使用效能,并且大幅降低星上系统设计难度,提高系统通用性和功能可升级性。具体包括:

22.1、本发明提出的方法,将训练好的卷积网络权重与偏置参数预加载到存储单元中,从外部获取图像数据,并由处理器软件进行配置卷积运算参数;同时,采用协处理器方法可以直接并行地对图像数据预处理,卷积运算,写回,运算效率得到了很大的提升,节省

了处理器缓存搬运数据的时间。

23.2、本发明提出的方法,通过减小处理器卷积运算中多余数据缓存,降低了运算存储空间,同时增大了可进行图像卷积处理的图像尺寸。

24.3、本发明提出的方法,通过由协处理完成卷积网络运算,实现了处理器监测与协处理器运算的协同工作。

25.4、本发明提出的方法,通过实现协处理函数接口,让协处理器具备可编程可配置的能力,对卷积网络的开发与应用提供支持。

附图说明

26.此处所说明的附图用来提供对本发明的进一步理解,构成本技术的一部分,本发明的示意性实施例及其说明用于解释本发明,并不构成对本发明的不当限定。其中:

27.图1为基于卷积神经网络的risc-v协处理系统结构框图。

28.图2为卷积神经网络的基本结构示意图。

29.图3为图像数据卷积运算流水线结构示意图。

30.图4为协处理的risc-v功能指令格式(符合rv32i i-type格式)示意图。

31.图5为利用协处理api函数快速搭建卷积神经网络架构流程示意图。

32.图6为基于卷积神经网络的risc-v协处理方法流程示意图。

33.图7为risc-v主处理器与协处理器加速对m

×m×

n图像进行卷积网络运算的性能测试与现有单独risc-v主处理器进行卷积网络运算的性能测试对比示意图(m=64,n=3)。

34.图8为risc-v主处理器与协处理器加速对m

×m×

n图像进行卷积网络运算的存储空间消耗与现有单独risc-v主处理器进行卷积网络运算的存储空间消耗对比示意图(m=64,n=3)。

具体实施方式

35.为使本技术实施例的目的、技术方案和优点更加清楚,下面将结合本技术实施例的附图,对本技术实施例的技术方案进行清楚、完整地描述。显然,所描述的实施例是本技术的一部分实施例,而不是全部的实施例。基于所描述的本技术的实施例,本领域普通技术人员在无需创造性劳动的前提下所获得的所有其他实施例,都属于本技术保护的范围。

36.除非另外定义,本技术使用的技术术语或者科学术语应当为本技术所属领域内具有一般技能的人士所理解的通常意义。本技术中使用的“第一”、“第二”以及类似的词语并不表示任何顺序、数量或者重要性,而只是用来区分不同的组成部分。“包括”或者“包含”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。“连接”或者“相连”等类似的词语并非限定于物理的或者机械的连接,而是可以包括电性的连接,不管是直接的还是间接的。“上”、“下”、“左”、“右”等仅用于表示相对位置关系,当被描述对象的绝对位置改变后,则该相对位置关系也可能相应地改变。

37.参阅图1,在一些实施例中,一种基于卷积神经网络的risc-v协处理系统,包括存储器、risc-v主处理器和协处理器;存储器用于存储数据,存储器与risc-v主处理器、协处理器连接,risc-v主处理器和协处理器可对存储器内数据进行读写;risc-v主处理器用于

发送risc-v功能指令;协处理器用于接收risc-v功能指令,根据接收到的risc-v功能指令搭建卷积神经网络,从存储器中读取图像数据,基于卷积神经网络对图像数据进行运算处理得到输出数据,将输出数据存入存储器。

38.在本实施例中,从外部获取图像数据,并由risc-v主处理器向协处理器传递指令搭建卷积神经网络;同时,采用协处理器方法可以直接并行地对图像数据预处理,卷积运算,写回,从而使运算效率得到了很大的提升,节省了处理器缓存搬运数据的时间。通过risc-v主处理器直接传递协处理器的相关配置参数,减小了协处理器卷积运算中多余数据缓存,降低了运算存储空间,同时增大了可进行图像卷积处理的尺寸。通过由协处理完成卷积网络运算,实现了risc-v主处理器监测与协处理器运算的协同工作。

39.具体的,risc-v主处理器中包括指令控制接口和数据高速缓存接口。其中,指令控制接口与协处理其连接,用于传输risc-v功能指令;数据高速缓存接口与存储器连接,用于传输数据。

40.具体的,用于搭建卷积神经网络的配置参数主要包括输入配置参数和输出配置参数。其中,输入配置参数包括输入图像尺寸、数据输入地址、激活方式、池化大小与方式、运算操作、卷积核大小等;输出配置参数包括图像数据转换输出、输出图像尺寸、数据输出地址等。

41.具体的,协处理器为高速运算单元,最高可接入risc-v主处理器二倍频率的时钟信号。

42.具体的,risc-v功能指令符合rv32i指令集的i-type格式。自定义专用于协处理的risc-v功能指令,本实施例提供的自定义专用于协处理的risc-v用户指令格式(符合rv32i i-type格式)如图4所示。

43.其中,opocde操作码为7’b11101111,用于被识别为自定义协处理用户指令;rd为目标寄存器,与协处理器的参数寄存器映射;funct3为功能编码,与协处理器的使能寄存器映射;rs1为读取当前处理器通用寄存器地址,rs1对应的32位数据作为协处理器的基础地址数据;imm[11:0]为协处理器配置的架构参数。当处理器识别指令为自定义协处理用户指令,等效于在流水线中执行读取rs1通用寄存器的32位数据且无返回值的操作,对处理器流水线上的通用寄存器以及存储无影响,同时将卷积运算参数传递到协处理器。

[0044]

在一些实施例中,协处理器包括预处理模块、卷积运算模块、输入仲裁模块和输出仲裁模块;预处理模块包括数据格式转换单元和边缘补零单元,卷积运算模块包括浮点运算单元、图像池化运算单元和图像全连接运算单元;输入仲裁模块用于对接收的控制信号和数据信号进行仲裁,将接收的控制信号和数据信号分发到数据格式转换单元、边缘补零单元、浮点运算单元、卷积运算单元、图像池化运算单元或图像全连接运算单元;输出仲裁模块用于对输出的控制信号和数据信号进行仲裁,将输出的控制信号和数据信号分发到存储器或异常监测模块;异常监测模块用于对输出的数据信号进行实时监测;异常监测模块的输入端口与输出仲裁模块连接,其输出端口与输入仲裁模块连接。

[0045]

在本实施例中,采用了软硬件协调加速运算的方法,协处理器由risc-v主处理器控制其数据运算行为。

[0046]

其中,输入仲裁模块主要负责整体数据的控制与搬运,根据执行的risc-v功能指令,将数据分发到数据预加载单元和卷积运算单元。其接收的控制信号和数据信号主要是

risc-v主处理器发送的risc-v功能指令和从存储器读取的相关数据。

[0047]

其中,输出仲裁模块主要负责输出数据的控制与搬运,根据执行的risc-v功能指令,将输出数据分发到存储器或异常监测模块。

[0048]

其中,异常监测模块主要用于对输出数据的异常监测,并及时反馈异常数据,以提高异常数据处理的效率。

[0049]

其中,数据数据格式转换单元主要功能是对图像数据进行格式转换,由接口层提供参数信号控制,其具体内容包括:

[0050]

实现功能:将图像数据的存储起始地址到存储末地址的数据转换成目标数据的格式,如整数转32位浮点数,32位浮点数转化为整数。

[0051]

实现方式:根据控制信号使能对应的数据转换模块(整数转浮点inttofp,浮点转整数fptoint),并开始发起遍历所需的数据地址请求,从第一存储单元接收读取到的图像数据后输入到转换模块中,输出写回第二存储单元,完成读写乒乓操作。判断当前数据转换地址匹配存储末数据地址时,结束图像数据格式转换工作。

[0052]

其中,图像补零操作单元用于解决卷积操作存在两个问题:一是图像经过卷积操作后,尺寸越来越小,不适宜多次卷积操作;二是图像角落和边界的信息在卷积过程中被整合丢失。补零操作则很好地弥补了卷积的这个缺陷。卷积补零设计可以对图像数据进行边缘补零,避免图像在每次卷积运算后尺寸发生变化,有利于后续的图像不断地卷积与池化。

[0053]

具体的,逻辑补零采用的规则是保持确保卷积后的图像大小不变,需要在原图边长基础上(上下左右两边对称补零)填充f-1个单位的零元素(卷积核尺寸f

×

f)。原图尺寸为m

×m×

n,逻辑补零后尺寸为(m+f-1)

×

(m+f-1)

×

n。实现方式:乒乓读写的操作,以目标图像第一存储单元为信号请求发起端,原图像数据第二存储单元为信号响应端,根据目标图像的地址需求转换出原图像的地址,经补零操作单元判断是否逻辑补零,若判断为是,填入数据0后写回到目标图像第一存储单元中,若判断为否,填入图像数据写回目标图像第二存储单元。

[0054]

其中,对于浮点运算单元。优选的,浮点运算单元采用ucb float 33位格式编译运行,浮点运算单元用于将ieee float 32位浮点数格式转换为ucb float 33位进行运算和将ucb float 33位浮点数格式转换为ieee float 32位进行存储。

[0055]

其中,浮点运算采用了ucb float 33位格式编译运行。ieee754 32位编码所要求的非规格化数(denormal number),对于硬件实现是一种痛苦,会导致很大的延迟,cpu可以选择不支持它。如intel的cpu支持ftz和daz标志位,arm的cpu支持fz标志位,amd的某些cpu,其simd单指令多数据的浮点单元,只有一个逻辑单元负责处理denormal非规范化浮点数,当一个向量元素中出现了非规格化的结果,要专门花周期来处理。所以,协处理器的浮点运算单元沿用了risc-v ucb float 33浮点格式。相比于ieee float 32浮点格式,ucb float 33浮点格式存储库中的浮点单元以内部重新编码格式(指数具有一个附加位)工作,在微处理器运算中更有效地处理非规格化数,从而减少了内部浮点运算延迟,更有效监测运算输出。

[0056]

具体的,与ieee float 32标准格式一样,重新编码的格式具有正负号,指数和有效位数字段,但指数多了一位。因此,例如,标准的32位单精度被重新编码为33位:一位为符号,9位为编码指数(比平时多一位),23位为尾数。重新编码的格式通过几种方式简化了浮

图像补零8

×8–

1024

×

10241-10241-1024 图像卷积8

×8–

1024

×

10241-10243-10241卷积核3

×

3或4

×

410241024 图像池化4

×4–

1024

×

1024

ꢀꢀ

2图像全连接 10485761048576 [0062]

表2卷积神经网络结构可配置参数表

[0063]

其中,对于卷积运算单元,图像数据卷积运算流水线结构如图3所示,所述卷积运算过程包括:fetch(取数据)、execute(执行)、write back(写回)3个大的步骤,对3个大的步骤又可以细分为九级流水线设计:df-》mul-》add_0-》add_1-》add_2-》add_3-》add_4-》add_out-》relu_wb。

[0064]

上述九级流水线解析,具体包括:

[0065]

df,为数据地址请求与数据包接收;

[0066]

mul,为执行段中的多个浮点单元并行乘法运算;

[0067]

add_0~add_4,为卷积核浮点乘法运算后的累加;

[0068]

add_out,为最终卷积核累加的结果输出;

[0069]

relu_wb,为将运算结果经过激活函数后,写回到存储模块中;

[0070]

具体的,采用流水线的方式提高了运算的并行度,下一级的数据取回与上一级的数据卷积写回同时进行,避免了流水线出现空闲节拍而造成效率降低,且减少了多余的fma(floating point multiply and add)浮点运算单元。对于卷积运算中的浮点乘法,其卷积核内运算属于向量级运算,数据间不存在相关性,所以采用核向量并行运算方式,同时将运算结果输出到浮点累加单元。对应地,卷积核向量运算数据获取也是按照向量级进行,这样可以保证流水线各个单元运算的同步性。但是对于卷积运算中的浮点累加单元,其累加运算具有依赖性,即下一组的累加计算需要等待上一组累加计算结果得出,因此需要有合理的控制逻辑保障卷积计算在流水线的正确节拍上。本发明中将加法运算拆分整合到流水线设计中,保证上一数据的输出延时不影响下一个数据的输入,避免了浮点累加运算中的相关性数据等待,提高了卷积运行效率。

[0071]

其中,对于图像池化运算单元。池化单元,也称为抽象单元,主要功能是对卷积后的图像数据进行池化操作,采用的为三级流水线方式,实现了流水式提取区域内最大浮点数(max-pooling)或者平均浮点数值(mean-pooling),其主要作用是对特征图的数据进行采样,缩小数据规模。根据学术界的研究成果,池化区域的尺寸多为2

×

2与3

×

3,滑动步长为2。具体的,实施例中默认滑动步长为2,同时为了具有更好的兼容性,不仅支持这两种尺寸的池化计算,并对这两种尺寸池化计算定制数据并行输入输出,提高运算效率,还支持后续潜在的不同尺寸池化计算。独立设计的池化单元有着更高的灵活性,实现兼容不同规模与结构的卷积神经网络。池化操作较为简单,且输入数据复用度低,在整个卷积神经网络框架中消耗时间和硬件资源较少,故设计较为简洁。池化计算模块包含了输入数据缓冲区、控制器、最大池化计算模块、平均池化计算单元。池化操作开始时,池化控制器根据函数中输入的池化运算参数,从协处理器数据通路中将图像数据读入到池化流水线中,池化计算模块根据参数类型计算数据,运算完成后立即将计算结果写回数据存储单元。

[0072]

其中,对于图像全连接运算单元,全连接单元在整个构架中起到分类器的作用,全

连接操作是向量的乘加操作,完成输入特征行向量与权值矩阵相乘,输出为另一个行向量的计算。实现方式与卷积运算层相似,都是以流水线的方式完成浮点乘加运行并且写回到存储单元当中。由于全连接流水线运算路径较短,偏置数据最后加到浮点乘法的累加运算中对整体运算延时有明显的延迟影响,所以对偏置数据浮点加法采用了乘加旁路的方式,当判断为卷积运算当前阶段的最后一个浮点乘法时,将浮点乘法逻辑转换为浮点乘加结合逻辑,节省加法运算时钟周期。这个在保证数据运算正常执行情况下,这种旁路加入的方式降低整体运算时间,从而提升运算效率。

[0073]

具体的,数据格式转换单元用于对图像数据进行格式转换,边缘补零单元用于对图像数据进行边缘补零。

[0074]

优选的,risc-v功能指令包括第一指令、第二指令、第三指令、第四指令和第五指令;第一指令用于配置图像数据格式转换参数,第二指令用于配置图像数据边缘补零参数,第三指令用于配置图像数据卷积运算参数,第四指令用于配置图像数据池化运算参数,第五指令用于配置图像数据全连接运算参数。

[0075]

优选的,图像数据经数据格式转换单元格式转换后,写回存储器的存储单元为边缘补零单元读取数据的单元;图像数据经边缘补零单元边缘补零后,写回存储器的存储单元为卷积运算单元读取数据的单元;图像数据经卷积运算单元卷积运算后,写回存储器的存储单元为图像池化运算单元读取数据的单元;图像数据经图像池化运算单元池化运算后,写回存储器的存储单元为图像全连接运算单元或者边缘补零单元读取数据的单元。

[0076]

其中,通过对运算过程中存储单元进行合理分配,进一步减少存储空间的消耗。

[0077]

在一些实施例中,存储器包括存储模块和存储仲裁模块;存储模块包括第一存储单元和第二存储单元,第一存储单元和第二存储单元用于乒乓读写,存储仲裁模块用于对存储模块读写的数据进行仲裁分发。

[0078]

其中,存储模块分为第一存储单元和第二存储单元两个,可以利用其存储分开特性进行乒乓读写操作,以节约缓存空间。

[0079]

优选的,存储模块还包括参数存储单元,参数存储单元用于预加载卷积神经网络的训练参数数据,训练参数数据包括权重数据和偏置数据。

[0080]

其中,参数存储单元挂载到axi4总线上,可以通过pc端预加载文件方式、c程序预加载、bitstream预加载的方式提前将数据保存在参数存储层内,之后也可以通过pc端实时更新该存储层单元的参数数据。

[0081]

此外,risc-v主处理器、协处理器都从属于整个图像处理soc,为提高整个图像处理soc中存储器的利用率,图像处理soc还包括图像压缩模块,图像压缩模块与协处理器共享数据存储模块。图像压缩模块也是soc的组成部分,但其功能与协处理器无关,仅仅是在需要存储空间时,图像压缩模块与协处理器共享同一块存储空间。

[0082]

在一些实施例中,risc-v主处理器通过c语言或汇编语言将risc-v功能指令封装为api函数形式传递给协处理器,协处理器具有相应的api函数接口。

[0083]

其中,由于协处理器其配套定制有相应的risc-v api函数接口,用以接收risc-v api函数指令。通过协处理器函数接口,让协处理器具备可编程、可配置的能力,对卷积网络的开发与应用提供支持。通过配置输入参数、输出参数信息即可实现快速编程的功能,提升软件设计效率,实现星上图像云检算法硬件加速。

[0084]

此外,用户在利用该risc-v主处理器实现卷积神经网络架构运算时,只需要利用api接口函数,便可以直接设置输入图像、输出图像的配置参数,避免了c程序实现的繁杂或c程序编译过程中对某个数据优化或删减而出错。同时,协处理器运算进程由risc-v主处理器实时控制并监测,保证运算过程中的可视化与可调试性。

[0085]

具体的,通过将用户指令封装成通用的函数,定制通用卷积神经网络api接口,抽象化底层电路实现,便于对协处理器的功能直接调用与算法开发,以配置卷积核权重参数、卷积核偏置参数、图像数据格式转换参数、图像数据补零参数、图像数据卷积运算参数、图像数据池化运算参数和图像数据全连接运算参数为例,具体配置函数封装为:

[0086]

1、卷积核权重参数预加载函数,用于卷积运算中的权重数据读入,函数设置当前权重数据存放基础地址weight_addr以及卷积核权重尺寸length

×

length

×

c1_level

×

c2_level,api封装示例如下:

[0087]

void cnn_irq_weight(unsigned int weight_addr,unsigned int length,unsigned int c1_level,unsigned int c2_level);

[0088]

2、卷积核偏置参数预加载函数,用于卷积运算中的偏置数据读入,函数设置偏置数据存地址biases_addr以及卷积核偏置尺寸c2_level,注意卷积核权重尺寸与偏置尺寸的c2_level为同一个数据变量,api封装示例如下:

[0089]

void cnn_irq_biases(unsigned int biases_addr,unsigned int c2_level);

[0090]

3、图像数据格式转换函数,用于图像数据格式转换,转换后图像数据覆盖在原存储单元中。函数设置图像数据起始地址addr_start、图像尺寸length

×

length

×

c1与图像转换后目标地址target_addr,整数转浮点型控制使能,api封装示例如下:

[0091]

void cnn_irq_typing(int addr_start,int length,int c1_level,int target_addr,int int2fp_valid,int fp2int_valid);

[0092]

4、图像数据补零函数,用于图像边缘数据补零操作,由输入地址存储单元提供图像数据,逻辑补零操作后存放在输出地址存储单元。函数设置数据起始地址与图像尺寸length

×

length

×

c1_level读入,设置写回存储地址与输出补零图像尺寸target_length

×

target_length

×

c1_level,api封装示例如下:

[0093]

void cnn_irq_paddding(unsigned int addr_start,unsigned int length,unsigned int c1_level,unsigned int target_addr,unsigned int target_length);

[0094]

5、图像数据卷积函数,用于图像卷积运算,由输入地址存储单元提供图像数据,由输入权重地址、输入偏置地址存储单元提供参数数据,卷积运算结果存放在输出地址存储单元。函数设置数据起始地址与图像尺寸length

×

length

×

c1_level,设置卷积运算步长,设置写回存储地址与输出补零图像尺寸target_length

×

target_length

×

c2_level,api封装示例如下:

[0095]

void cnn_irq_aluing(unsigned int addr_start,unsigned int length,unsigned int c1_level,unsigned int stride,unsigned int target_addr,unsigned int target_length,unsigned int c2_level);

[0096]

6、图像数据池化函数,用于图像卷积后的池化运算,由输入地址存储单元提供图像数据,池化后数据存放在输出地址存储单元。函数设置数据起始地址addr_start,图像尺寸length

×

length

×

c2_level,池化尺寸,输出地址target_addr,输出图像尺寸target_

length

×

target_length

×

c2_level,api封装示例如下:

[0097]

void cnn_irq_pooling(unsigned int addr_start,unsigned int length,unsigned int c2_level,unsigned int pooling,unsigned int target_addr,unsigned int target_length);

[0098]

7、图像数据全连接函数,用于图像全连接卷积运算,由输入地址存储单元提供图像数据,全连接运算后数据存放在输出地址存储单元。函数设置数据起始地址addr_start,池化后输出图像尺寸target_length

×

target_length

×

c2_level,全连接第一层卷积单元个数fc1,输出地址target_addr,全连接下一层卷积单元个数fc2,api封装示例如下:

[0099]

void cnn_irq_fulling(int addr_start,int target_length,int c2_level,int fc1,int target_addr,int fc2,int weight_addr,int biases_addr)。

[0100]

结合上述api接口函数,参阅图5,利用上述协处理api函数可快速搭建卷积神经网络架构。优选的,每个api函数都会对协处理器运算状态进行循环监测与判断,判断为当前运算操作结束后,跳出当前定制api函数执行下一个阶段命令函数,避免数据之间读写冲突。

[0101]

参阅图6,在一些实施例中,还公开了一种基于卷积神经网络的risc-v协处理方法,方法基于上述的基于卷积神经网络的risc-v协处理系统,包括:

[0102]

s601,risc-v主处理器向协处理器发送risc-v功能指令;

[0103]

s602,协处理器接收risc-v功能指令,根据接收到的risc-v功能指令搭建卷积神经网络,从存储器中读取图像数据,基于卷积神经网络对图像数据进行运算处理得到输出数据,将输出数据存入存储器;

[0104]

s603,risc-v主处理器从存储器中读取输出数据进行后续处理。

[0105]

综合上述实施例,将risc-v主处理器与协处理器、risc-v主处理器在fpga测试板以相同的时钟频率a mhz进行性能与存储消耗测试(a=50),得到如图7、图8所示的测试结果:

[0106]

参阅图7,本技术提供的risc-v主处理器与协处理器加速对m

×m×

n图像进行卷积网络运算的性能测试与现有单独risc-v主处理器进行卷积网络运算的性能测试对比示意图。该性能测试中,在完成卷积图像层数输出的运行时间消耗中,单独risc-v主处理器完成的时间平均约为risc-v主处理器+协处理器加速完成的时间的16倍(m=64,n=3)。

[0107]

参阅图8,本技术提供的risc-v主处理器与协处理器加速对m

×m×

n图像进行卷积网络运算的存储空间消耗与现有单独risc-v主处理器进行卷积网络运算的存储空间消耗对比示意图。该存储空间消耗测试中,在完成卷积图像层数输出的存储空间消耗中,单独risc-v主处理器消耗的存储空间平均约为risc-v主处理器+协处理器加速消耗的存储空间的4倍(m=64,n=3)。

[0108]

由此可见,基于本技术的基于卷积神经网络的risc-v协处理系统的协处理方法,在运算速度与存储空间消耗上具有明显优势。

[0109]

如上即为本发明的实施例。上述实施例以及实施例中的具体参数仅是为了清楚表述发明的验证过程,并非用以限制本发明的专利保护范围,本发明的专利保护范围仍然以其权利要求书为准,凡是运用本发明的说明书及附图内容所作的等同结构变化,同理均应包含在本发明的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1