一种申威1621COME主板电路的制作方法

一种申威1621come主板电路

技术领域

1.本实用新型涉及服务器主板技术领域,具体为一种申威1621come主板电路。

背景技术:

2.申威服务器是国产的处理器,相比其他国产处理器,申威在性能上走在前列,申威1621处理器是其中一种,目前应用1621处理器的主板电路结构布局复杂,成本高。

技术实现要素:

3.为了解决现有电路布局复杂的问题,本实用新型提供了一种申威1621come主板电路,其电路布局简单,降低成本。

4.其技术方案是这样的:一种申威1621come主板电路,其包括1621处理器芯片,其特征在于,所述1621处理器芯片连接申威ich2芯片、四根ddr3、第一flash模块、第一jtag接口、pcie插条一,所述申威ich2芯片连接第二flash芯片、两根ddr3颗粒、pcie插条二、vga&lvds模块、rtc模块、以太网模块、uart串口、usb接口、sata接口、gpio模块、iic总线、第二jtag接口、电平转换模块,所述电平转换模块连接lpc总线、cpld,所述cpld连接第三jtag接口和所述电平转换模块。

5.其进一步特征在于,

6.所述rtc模块包括时钟芯片uha4,所述时钟芯片uha4的1脚和2脚连接晶振,所述晶振的5脚通过电阻rha126连接电阻rha363的一端和电源管理芯片qha2的6脚,所述晶振的6脚通过电阻rha123连接电阻rha362的一端和电源管理芯片qha2的3脚,所述时钟芯片uha4的7脚连接电容cha364一端和整流二极管dha2的2脚,所述整流二极管dha2的3脚连接所述申威ich2芯片,所述整流二极管dha2的1脚连接电阻rha113一端,所述电阻rha113另一端通过保险丝bha49连接电容cha363一端、cha362一端、cha361一端、3.3v电源和所述时钟芯片uha4的8脚,所述电源管理芯片qha2的1脚连接电阻rha364一端和所述申威ich2芯片,所述电源管理芯片qha2的4脚连接电阻rha365一端和所述申威ich2芯片,所述电阻rha364另一端、电阻rha365另一端均连接vdd、所述电源管理芯片qha2的2脚和5脚;

7.所述第二flash模块包括门控制芯片uha2和flash芯片usp1,所述门控制芯片uha2的2脚、3脚、6脚均接地,所述门控制芯片uha2的4脚通过电阻rha97连接所述申威ich2芯片,所述申威ich2芯片的5脚连接vdd和电容cha359一端,所述电容cha359另一端接地,所述门控制芯片uha2的1脚连接所述flash芯片usp1的2脚、电阻rha104一端、电阻rha108一端,所述电阻rha104另一端连接vdd、电阻rha105一端、电阻rha103一端,所述电阻rha103另一端连接所述flash芯片usp1的3脚,所述flash芯片usp1的8脚连接vdd和电容cha360的一端,所述电容cha360另一端接地,所述flash芯片usp1的7脚通过电阻rha106连接vdd,所述电阻rha105另一端和所述flash芯片usp1的1脚、5脚、6脚均连接申威ich2芯片。

8.采用本实用新型后,将原本1621处理器芯片连接8根内存条直接减少为4根,运行经济模式,并对外围电路进行合理调整,结构布局简单,降低了成本。

附图说明

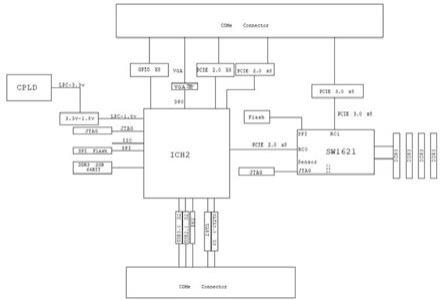

9.图1为本实用新型电路原路框图;

10.图2为rtc模块电路原理图;

11.图3为第二flash模块电路原理图。

具体实施方式

12.见图1,图2,图3所示,一种申威1621come主板电路,其包括1621处理器芯片,所述1621处理器芯片连接申威ich2芯片、四根ddr3、第一flash模块、第一jtag接口、pcie插条一,申威ich2芯片连接第二flash芯片、两根ddr3、pcie插条二、vga&lvds模块、rtc模块、以太网模块、uart串口、usb接口、sata接口、gpio模块、iic总线、第二jtag接口、电平转换模块,电平转换模块连接lpc总线、cpld,cpld连接第三jtag接口和电平转换模块。1621处理器芯片与申威ich2芯片之间通过pcie总线相连接,ich2芯片提供pcie、usb、vga、uart、lpc等接口信号,通过come连接器提供给底板使用。cpld芯片控制主板上电时序和复位。

13.rtc模块包括时钟芯片uha4,时钟芯片uha4的1脚和2脚连接晶振,晶振的5脚通过电阻rha126连接电阻rha363的一端和电源管理芯片qha2的6脚,晶振的6脚通过电阻rha123连接电阻rha362的一端和电源管理芯片qha2的3脚,时钟芯片uha4的7脚连接电容cha364一端和整流二极管dha2的2脚,整流二极管dha2的3脚连接申威ich2芯片,整流二极管dha2的1脚连接电阻rha113一端,电阻rha113另一端通过保险丝bha49连接电容cha363一端、cha362一端、cha361一端、3.3v电源和时钟芯片uha4的8脚,电源管理芯片qha2的1脚连接电阻rha364一端和申威ich2芯片,电源管理芯片qha2的4脚连接电阻rha365一端和申威ich2芯片,电阻rha364另一端、电阻rha365另一端均连接vdd、电源管理芯片qha2的2脚和5脚;

14.第二flash模块包括门控制芯片uha2和flash芯片usp1,门控制芯片uha2的2脚、3脚、6脚均接地,门控制芯片uha2的4脚通过电阻rha97连接申威ich2芯片,申威ich2芯片的5脚连接vdd和电容cha359一端,电容cha359另一端接地,门控制芯片uha2的1脚连接flash芯片usp1的2脚、电阻rha104一端、电阻rha108一端,电阻rha104另一端连接vdd、电阻rha105一端、电阻rha103一端,电阻rha103另一端连接flash芯片usp1的3脚,flash芯片usp1的8脚连接vdd和电容cha360的一端,电容cha360另一端接地,flash芯片usp1的7脚通过电阻rha106连接vdd,电阻rha105另一端和flash芯片usp1的1脚、5脚、6脚均连接申威ich2芯片。

技术特征:

1.一种申威1621come主板电路,其包括1621处理器芯片,其特征在于,所述1621处理器芯片连接申威ich2芯片、四根ddr3、第一flash模块、第一jtag接口、pcie插条一,所述申威ich2芯片连接第二flash芯片、两根ddr3颗粒、pcie插条二、vga&lvds模块、rtc模块、以太网模块、uart串口、usb接口、sata接口、gpio模块、iic总线、第二jtag接口、电平转换模块,所述电平转换模块连接lpc总线、cpld,所述cpld连接第三jtag接口和所述电平转换模块。2.根据权利要求1所述的一种申威1621come主板电路,其特征在于,所述rtc模块包括时钟芯片uha4,所述时钟芯片uha4的1脚和2脚连接晶振,所述晶振的5脚通过电阻rha126连接电阻rha363的一端和电源管理芯片qha2的6脚,所述晶振的6脚通过电阻rha123连接电阻rha362的一端和电源管理芯片qha2的3脚,所述时钟芯片uha4的7脚连接电容cha364一端和整流二极管dha2的2脚,所述整流二极管dha2的3脚连接所述申威ich2芯片,所述整流二极管dha2的1脚连接电阻rha113一端,所述电阻rha113另一端通过保险丝bha49连接电容cha363一端、cha362一端、cha361一端、3.3v电源和所述时钟芯片uha4的8脚,所述电源管理芯片qha2的1脚连接电阻rha364一端和所述申威ich2芯片,所述电源管理芯片qha2的4脚连接电阻rha365一端和所述申威ich2芯片,所述电阻rha364另一端、电阻rha365另一端均连接vdd、所述电源管理芯片qha2的2脚和5脚。3.根据权利要求2所述的一种申威1621come主板电路,其特征在于,所述第二flash模块包括门控制芯片uha2和flash芯片usp1,所述门控制芯片uha2的2脚、3脚、6脚均接地,所述门控制芯片uha2的4脚通过电阻rha97连接所述申威ich2芯片,所述申威ich2芯片的5脚连接vdd和电容cha359一端,所述电容cha359另一端接地,所述门控制芯片uha2的1脚连接所述flash芯片usp1的2脚、电阻rha104一端、电阻rha108一端,所述电阻rha104另一端连接vdd、电阻rha105一端、电阻rha103一端,所述电阻rha103另一端连接所述flash芯片usp1的3脚,所述flash芯片usp1的8脚连接vdd和电容cha360的一端,所述电容cha360另一端接地,所述flash芯片usp1的7脚通过电阻rha106连接vdd,所述电阻rha105另一端和所述flash芯片usp1的1脚、5脚、6脚均连接申威ich2芯片。

技术总结

本实用新型涉及服务器主板技术领域,具体为一种申威1621COME主板电路,其电路布局简单,降低成本,其包括1621处理器芯片,其特征在于,所述1621处理器芯片连接申威ICH2芯片、四根DDR3、第一FLASH模块、第一JTAG接口、PCIE插条一,所述申威ICH2芯片连接第二FLASH芯片、两根DDR3颗粒、PCIE插条二、VGA&LVDS模块、RTC模块、以太网模块、UART串口、USB接口、SATA接口、GPIO模块、IIC总线、第二JTAG接口、电平转换模块,所述电平转换模块连接LPC总线、CPLD,所述CPLD连接第三JTAG接口和所述电平转换模块。CPLD连接第三JTAG接口和所述电平转换模块。CPLD连接第三JTAG接口和所述电平转换模块。

技术研发人员:方伟迪 黄胜顶 蒋小铂 李强 徐江川 刘鑫

受保护的技术使用者:上海君众信息科技有限公司

技术研发日:2021.11.24

技术公布日:2022/4/13

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1