用于自容式仪器的超低功耗的大容量数据存储方法与流程

[0001]

本发明涉及自容式仪器的数据存储技术领域,尤其涉及一种超低功耗的大容量数据存储方法。

背景技术:

[0002]

在一些自容式仪器应用场景中,自容式仪器由电池供电,需要长期独立工作,并且工作期间记录的大量数据都需要记录在自容式仪器本地,比如深海水温水深监测仪、海底节点地震勘探仪器、移动式数字地震仪、环境监测仪器等。

[0003]

自容式仪器被投放到工作环境后往往需要长期工作数月,供电十分不便,只能依靠自身携带的电池供电,同时便携自容式仪器整体设计上往往有体积、机械尺寸等限制,因此能装配的电池的数量、体积也有限。故自容式仪器需要具有低功耗的特性才能保证自容式仪器可以长时间而不掉电。自容式仪器工作期间不与外界通讯,期间采集的数据量往往多达几十甚至上百gb,这些数据只能存储在本地,等到作业结束,自容式仪器回收后才将数据回读。

[0004]

自容式仪器内部的电路往往比较复杂,需要控制数据采集、数据存储、数据传输、电路供电等各个模块元件的运行,此时简单的mcu微控制器不能胜任电路的控制中心的功能,通常使用fpga或者soc作为电路的控制中心。fpga主要通过其可编程的特性定制出自容式仪器内部的控制电路,实现仪器内部各个元器件的协调工作,并具有数据处理,接口通讯等功能。soc不仅具有fpga可编程逻辑的功能,还支持软件的开发,灵活性更大。

[0005]

自容式仪器工作期间需要存储的数据往往在几十gb到上百gb,要存储这些数据,sd卡和emmc flash是容量适合的存储芯片。sd卡和emmc flash都是将闪存控制器和nand flash封装在一起,两者协议兼容,sd卡是基于mmc协议发展起来的,只不过sd卡单独封装,而emmc是bga封装,更适合在pcb焊接且emmc的读写速度更优一些。

[0006]

常规的做法是用soc芯片控制sd卡或者emmc flash芯片。使用soc实现软硬件协同设计主要的考虑点是通过软件来控制sd卡或者emmc flash。sd卡或者emmc flash协议比较复杂,通常采用软件控制,相关的资料包括软件代码和驱动程序比较丰富,技术开发难度较低。

[0007]

soc控制sd卡或者emmc flash的常规方法有3个问题。第一个问题是自容式仪器源源不断的采集数据,而flash一直工作在写入模式,功耗将会很大。自容式仪器在长达数月的工作期间源头数据率一般较低且平缓,如果flash一直工作在写入模式以便及时写入这些数据的话flash芯片功耗为几百毫瓦,具体数值和数据源速率有关,数据源速率越快,flash的写入操作就越频繁,功耗越大。

[0008]

第二个问题是为了方便地控制sd卡或者emmc flash使用soc作为电路主控制器,这和使用fpga相比带来了更大的功耗。如果只是控制电路其他元件的工作,fpga就可以胜任。emmc flash控制比较复杂,使用soc控制flash会简化开发者的设计工作和降低设计难度,但这是以增加功耗为代价的。soc的功耗往往是同等逻辑量fpga的数倍。如果可以实现

fpga硬件逻辑直接控制emmc flash的技术,就可以减少电路主控制器带来的功耗。

[0009]

第三个问题是常规的主控制器芯片fpga和soc主要都是基于sram工艺的,不具备低功耗的特性。fpga和soc两的大主流厂商intel和xilinx的产品占据了90%的市场,但是intel和xilinx的fpga和soc是基于sram架构的,不具备低功耗的特性。另一种非易失flash架构的fpga和soc技术上显著特征是具有更低的功耗,适合追求超低功耗的应用场景,典型厂商为microsemi。

[0010]

故目前亟需一种降低自容式仪器数据存储功耗的存储方法,以便解决自容式仪器低功耗设计和大容量数据存储等场景需求的问题。

技术实现要素:

[0011]

有鉴于此,本发明的主要目的在于提供一种超低功耗的大容量数据存储方法,以期部分地解决上述技术问题中的至少之一。

[0012]

为了实现上述目的,作为本发明的一方面,提供了一种数据存储方法,包括以下内容:

[0013]

自容式仪器上电后启动一次emmc flash初始化;

[0014]

作业过程中,待存储数据先缓存在低功耗sram中,此时emmc flash处于极低功耗睡眠模式;

[0015]

当sram接近满之后触发转运过程,此时唤醒emmc flash,数据从sram中转运到emmc flash,即sram向emmc flash发起一次单块写的写操作请求;

[0016]

转运完成后emmc flash再次进入睡眠模式;

[0017]

自容式仪器作业过程中不断执行上述sram和emmc flash组合存储的循环;

[0018]

当自容式仪器回收到地面后,将通过多块读的方式快速读出数据;

[0019]

所述方法中采用基于flash架构的低功耗fpga作为自容式仪器的控制中心;

[0020]

通过fpga硬件逻辑实现存储控制,包括对emmc flash和sram的控制。

[0021]

其中,所述fpga硬件逻辑实现emmc flash控制的方法为根据emmc协议设计出初始化流程和读写操作应该下发的指令内容和预期响应,并通过ahb lite总线主机接口读写mmc core内部寄存器实现和emmc flash芯片的通讯;emmc flash初始化和读写控制过程中,除了cmd0复位指令没有响应外,其他指令都会收到emmc flash给出的响应。

[0022]

其中,用户逻辑控制mmc core向emmc flash下发指令与获取响应的过程具体包括:

[0023]

每次下发指令需要写指令序号寄存器和写指令参数寄存器;

[0024]

当mmc core收到完整的指令序号和指令参数后会生成起始位、停止位和crc校验,并发起对应指令;

[0025]

当mmc core接收到来自emmc flash芯片的响应后,会将mmc core的状态寄存器的响应接收标志位置位;

[0026]

用户逻辑在下发指令后不断查询mmc core的状态寄存器;

[0027]

当检测到响应接收标志位置位后再查询mmc core的中断状态寄存器;如果中断状态寄存器置位,则报错,否则进入下一步读取mmc core的响应寄存器内容。

[0028]

其中,所述emmc flash初始化具体包括:

[0029]

上电后启动初始化;

[0030]

下发cmd0复位指令使emmc flash进入空闲状态;

[0031]

依次下发cmd1、cmd2、cmd3和cmd9分别查询flash芯片的ocr寄存器、cid寄存器、设置相对地址和查询csd寄存器,了解emmc flash芯片的出厂性能和允许的操作;

[0032]

下发cmd7使emmc flash进入传输模式;

[0033]

下发cmd16设置读写操作时的块长度,并修改mmc core中的块长度寄存器数值;

[0034]

下发cmd6设置emmc flash的数据总线为8比特位宽;

[0035]

初始化完成。

[0036]

其中,所述单块写具体包括:

[0037]

下发单块写对应的指令cmd24并读取响应;

[0038]

向mmc core内部的写入数据寄存器传递待写入flash的数据;

[0039]

查询mmc core内部的单块操作中断状态寄存器,等待mmc core完成单块写操作;

[0040]

写mmc core内部的单块操作中断清除寄存器,使得单块操作中断状态寄存器复位;

[0041]

等待编程完成,编程过程数据线最低位会被拉低,编程完成后8根数据线都会被拉高;

[0042]

写操作完成。

[0043]

其中,所述多块读的控制流程具体包括:

[0044]

下发指令cmd23设置多块操作的块数量;

[0045]

改写mmc core内部的块数量寄存器的值;

[0046]

下发多块读指令cmd18,指令参数为flash芯片的读地址;

[0047]

查询mmc core的多块操作中断状态寄存器;

[0048]

从mmc core的读出数据寄存器中读取所读数据,单个块的数据量为512字节,故应读数据字节量为512*块数量;

[0049]

改写mmc core内部的多块操作中断清除寄存器,使得多块操作中断状态寄存器复位;

[0050]

读操作完成。

[0051]

基于上述技术方案可知,本发明的数据存储方法相对于现有技术至少具有如下有益效果的一部分:

[0052]

本发明提出一种超低功耗的大容量存储方法,解决自容式仪器低功耗设计和大容量数据存储等场景需求的问题,比如深海水温水深监测仪、海底节点地震勘探仪器、移动式数字地震仪等。在这些场景中,自容式仪器由电池供电,需要长期独立工作,并且工作期间记录的大量数据都需要记录在自容式仪器本地。低功耗的大容量存储方法可以满足大容量数据存储和自容式仪器长时间运行的要求。

附图说明

[0053]

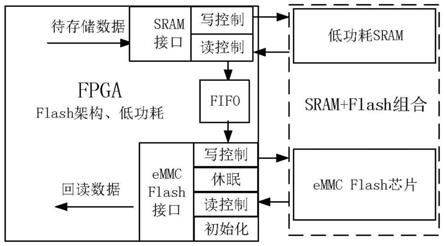

图1为本发明实施例提供的低功耗大容量数据存储方法示意图;

[0054]

图2为本发明实施例提供的sram和flash组合存储数据流过程图;

[0055]

图3为本发明实施例提供的基于sram(左)和flash(右)架构fpga可编程单元结构

对比;

[0056]

图4为本发明实施例提供的mmc core内部结构图;

[0057]

图5为本发明实施例提供的硬件逻辑控制emmc flash的逻辑框图;

[0058]

图6为本发明实施例提供的emmc flash初始化流程图;

[0059]

图7为本发明实施例提供的用户逻辑控制mmc core下发指令与获取响应过程图;

[0060]

图8为本发明实施例提供的emmc flash写操作控制流程图;

[0061]

图9为本发明实施例提供的读操作控制流程图。

具体实施方式

[0062]

本发明提出一种超低功耗的大容量存储方法,解决自容式仪器低功耗设计和大容量数据存储等场景需求的问题。比如深海水温水深监测仪、海底节点地震勘探仪器、移动式数字地震仪等。在这些场景中,自容式仪器由电池供电,需要长期独立工作,并且工作期间记录的大量数据都需要记录在自容式仪器本地。低功耗的大容量存储方法可以满足大容量数据存储和自容式仪器长时间运行的要求。本发明所提出的方法有三个关键设计:一是采用sram芯片+emmc flash芯片组合的方式极大地降低emmc flash芯片本身的功耗。二是选择基于flash架构的fpga降低主控制器的功耗。三是通过fpga硬件逻辑控制emmc flash,比soc软件控制emmc flash进一步降低了主控制器的功耗。

[0063]

具体的,本发明公开了一种数据存储方法,包括以下内容:

[0064]

自容式仪器上电后启动一次emmc flash初始化;

[0065]

作业过程中,待存储数据先缓存在低功耗sram中,此时emmc flash处于极低功耗睡眠模式;

[0066]

当sram接近满之后触发转运过程,此时唤醒emmc flash,数据从sram中转运到emmc flash,即sram向emmc flash发起一次单块写的写操作请求;

[0067]

转运完成后emmc flash再次进入睡眠模式;

[0068]

自容式仪器作业过程中不断执行上述sram和emmc flash组合存储的循环;

[0069]

当自容式仪器回收到地面后,将通过多块读的方式快速读出数据;

[0070]

所述方法中采用基于flash架构的低功耗fpga作为自容式仪器的控制中心;

[0071]

通过fpga硬件逻辑实现存储控制,包括对emmc flash和sram的控制。

[0072]

其中,所述fpga硬件逻辑实现emmc flash控制的方法为根据emmc协议设计出初始化流程和读写操作应该下发的指令内容和预期响应,并通过ahb lite总线主机接口读写mmc core内部寄存器实现和emmc flash芯片的通讯;emmc flash初始化和读写控制过程中,除了cmd0复位指令没有响应外,其他指令都会收到emmc flash给出的响应。

[0073]

其中,用户逻辑控制mmc core向emmc flash下发指令与获取响应的过程具体包括:

[0074]

每次下发指令需要写指令序号寄存器和写指令参数寄存器;

[0075]

当mmc core收到完整的指令序号和指令参数后会生成起始位、停止位和crc校验,并发起对应指令;

[0076]

当mmc core接收到来自emmc flash芯片的响应后,会将mmc core的状态寄存器的响应接收标志位置位;

[0077]

用户逻辑在下发指令后不断查询mmc core的状态寄存器;

[0078]

当检测到响应接收标志位置位后再查询mmc core的中断状态寄存器;如果中断状态寄存器置位,则报错,否则进入下一步读取mmc core的响应寄存器内容。

[0079]

其中,所述emmc flash初始化具体包括:

[0080]

上电后启动初始化;

[0081]

下发cmd0复位指令使emmc flash进入空闲状态;

[0082]

依次下发cmd1、cmd2、cmd3和cmd9分别查询flash芯片的ocr寄存器、cid寄存器、设置相对地址和查询csd寄存器,了解emmc flash芯片的出厂性能和允许的操作;

[0083]

下发cmd7使emmc flash进入传输模式;

[0084]

下发cmd16设置读写操作时的块长度,并修改mmc core中的块长度寄存器数值;

[0085]

下发cmd6设置emmc flash的数据总线为8比特位宽;

[0086]

初始化完成。

[0087]

其中,所述单块写具体包括:

[0088]

下发单块写对应的指令cmd24并读取响应;

[0089]

向mmc core内部的写入数据寄存器传递待写入flash的数据;

[0090]

查询mmc core内部的单块操作中断状态寄存器,等待mmc core完成单块写操作;

[0091]

写mmc core内部的单块操作中断清除寄存器,使得单块操作中断状态寄存器复位;

[0092]

等待编程完成,编程过程数据线最低位会被拉低,编程完成后8根数据线都会被拉高;

[0093]

写操作完成。

[0094]

其中,所述多块读的控制流程具体包括:

[0095]

下发指令cmd23设置多块操作的块数量;

[0096]

改写mmc core内部的块数量寄存器的值;

[0097]

下发多块读指令cmd18,指令参数为flash芯片的读地址;

[0098]

查询mmc core的多块操作中断状态寄存器;

[0099]

从mmc core的读出数据寄存器中读取所读数据,单个块的数据量为512字节,故应读数据字节量为512*块数量;

[0100]

改写mmc core内部的多块操作中断清除寄存器,使得多块操作中断状态寄存器复位;

[0101]

读操作完成。

[0102]

为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明作进一步的详细说明。

[0103]

如图1所示,为低功耗大容量存储方法的示意图;该方法有三个关键设计:一是采用sram芯片+emmc flash芯片组合的方式极大地降低emmc flash芯片本身的功耗。二是选择基于flash架构的fpga降低主控制器的功耗。三是通过fpga硬件逻辑控制emmc flash,比soc软件控制emmc flash进一步降低了主控制器的功耗。以下逐条详述。

[0104]

第一,采用低功耗sram芯片+emmc flash芯片组合的方式大幅降低emmc flash芯片本身的功耗。自容式仪器工作期间,源源不断的采集数据,如果直接用emmc flash存储数

据,那么emmc flash保持在写入模式的功耗为几百毫瓦。然而,emmc flash芯片本身具有一种休眠模式,该模式下emmc flash芯片的功耗只有约1毫瓦,相比写入模式的功耗低了两个数量级,可以忽略不计。为了使emmc flash进入休眠模式同时该存储的数据又不丢失,那就需要在数据源和emmc flash之间加入一级缓存。低功耗的静态随机存储器sram是非常合适的缓存材料。它功耗低,读写功耗一般只有几毫瓦,并且容量较大,实际选用时可以根据具体应用场景选择合适容量的sram。sram和flash组合存储的完整数据流过程如图2所示,采集到的数据首先存放在sram中,此时emmc flash处于休眠状态,当sram缓存接近满的时候,再唤醒emmc flash将读出sram缓存的数据再写入flash,写入完成后flash再次进入休眠模式。按此循环完成数据存储,就可以实现完成数据存储的同时,使得emmc flash几乎处于极低功耗的休眠模式,从而使得emmc flash和sram合计总平均功耗可降低至10mw以内。

[0105]

第二,选择基于flash架构的fpga降低主控制器的功耗。主要的fpga和soc是基于sram架构,不具备低功耗的特性,典型厂商为intel和xilinx。而基于flash架构的fpga最显著的特性就是低功耗,典型厂商为microsemi。如图3所示为基于sram(左)和flash(右)架构fpga可编程单元结构对比图,基于flash技术的fpga和soc每个可编程的开关都是由单个个晶体管构成,而基于sram技术的fpga每个可编程开关是由6个晶体管构成,因此基于flash架构的fpga的开关消耗功耗要比基于sram架构的fpga低很多。另外基于flash架构的fpga由于掉电非易失,不需要配置过程,所以只有静态功耗和动态功耗,相比基于sram架构的fpga省去了上电功耗和配置功耗。根据microsemi公司的评测结果,基于flash架构的fpga和soc比基于sram架构的同级别fpga和soc的总功耗低30%到50%。

[0106]

第三,实现了fpga硬件逻辑实时控制emmc flash,比soc软件控制emmc flash显著降低了主控制器的功耗。emmc协议基通过命令和数据总线实现通讯。对emmc flash的每次操作由命令(主机到设备)和响应(设备到主机)组成,指令和响应复用一根指令线,在涉及数据读写时还伴随着数据线上的数据传输。为了实现fpga硬件逻辑实时控制emmc flash的技术,设计了完整的基于mmc core的初始化和读写控制状态机。首先根据emmc协议设计出emmc初始化流程和读写操作应该下发的指令内容和预期响应,然后读写mmc core内部的指令、状态、响应和数据寄存器,最终实现对emmc flash芯片的控制。

[0107]

本实施例选取的自容式仪器存储电路选择的emmc flash芯片型号为闪迪公司的sdinadf4-64g-h,容量为64gb。选择低功耗sram芯片的型号为cy62167ev18ll-55bvxi,存储容量为2gb,该sram功耗极低,典型读写功耗为4mw@1mhz时钟频率,无操作时空闲状态功耗只有几微瓦。自容式仪器工作时,如图1低功耗大容量存储方法的示意图所示,设置sram的接近满深度为可以缓存约1分钟的采集数据,sram缓存数据的这1分钟里emmc flash处于休眠状态,功耗只有1毫瓦左右,相比emmc flash的写入模式的几百毫瓦功耗可以忽略不计。而从sram读出数据再写入flash的过程很快,只有不到1秒钟,flash仅仅在这1秒不到的时间里处于写入模式。因此在一个读写循环里,flash几乎都处于休眠状态。emmc flash进入休眠模式可以通过下发休眠指令实现。实际上emmc flash底层是基于inand flash的,inand的一个独特的特点是自动进入和退出休眠模式。在完成一个操作后,如果没有收到进一步的命令emmc flash将进入自动休眠模式。当控制器访问处于休眠模式时的emmc flash,向emmc flash发出的任何命令都将使它退出休眠并作出响应。实际运用中为了操控简便,运用了emmc flash这种自动休眠的特性,每次读取sram数据再写入flash的过程结束

core的指令序号寄存器中写入数值1,并向指令参数寄存器写入数值32

’

hc0ff8080作为cmd1的指令参数,当mmc core收到完整的指令序号和指令参数后会会生成起始位、停止位和crc校验,并发起对应指令。当mmc core接收到来自emmc flash芯片的响应后,会将mmc core的状态寄存器的响应接收标志位置位。用户逻辑在下发指令后不断查询mmc core的状态寄存器,当检测到响应接收标志位置位后再查询mmc core的中断状态寄存器,如果中断状态寄存器置位,则报错,否则进入下一步读取mmc core的响应状态寄存器内容,至此一个完整的与mmc core交互的指令下发与响应接收过程完成。

[0120]

emmc flash读写操作支持单块读写和多块读写。自容式仪器的采集过程源头数据速率平缓,因此emmc flash写操作选择单块写的方式,相比多块写具有设计简单、fpga资源占用少的优点。在自容式仪器回收到地面之后,要求快速的读出存储数据,因此emmc flash读操作采用多块读的方式,相比单块读,速率快好几倍,具体值和设置一次读操作读取块数有关,比如设置一次读出16个块时读出速率超过100mbps。

[0121]

emmc flash单块写的流程如图8所示。具体过程如下。

[0122]

1)下发单块写对应的指令cmd24并读取响应,该过程与图7描述的常规下发指令过程相同。

[0123]

2)向mmc core内部的写入数据寄存器传递待写入flash的数据。单块写的数据量为512字节。当传递的待写数据量达到512字节时传递完成。mmc core会将这些数据加上起始位、停止位和crc校验后按规定时序发给emmc flash芯片。当mmc core完成该过程后会将内部的单块操作中断状态寄存器写完成标志位置位。

[0124]

3)查询mmc core内部的单块操作中断状态寄存器,等待mmc core完成单块写操作。

[0125]

4)写mmc core内部的单块操作中断清除寄存器,使得单块操作中断状态寄存器复位。因为在上一步中单块操作中断状态寄存器的写完成标志位已经置位,因此需要将其复位,这样在写入下一个块的数据时块操作中断状态寄存器仍然可以正确的提示写操作完成情况。

[0126]

5)等待编程完成。emmc flash芯片在收到待写数据后需要时间编程,将这些数据写入非易失存储介质,编程过程数据线最低位会被拉低以提示编程尚未完成。编程完成后8根数据线都会被拉高。

[0127]

6)写操作完成。

[0128]

emmc flash多块读的控制流程如图9所示。具体过程如下。

[0129]

1)下发指令cmd23设置多块操作的块数量为16,该过程与图7描述的指令下发过程相同。

[0130]

2)改写mmc core内部的块数量寄存器的值为16。

[0131]

3)下发多块读指令cmd18,指令参数为flash芯片的读地址。该过程与图7描述的指令下发过程相同。

[0132]

4)查询mmc core的多块操作中断状态寄存器。当mmccore收到来自emmc flash芯片的读出数据后,会将多块操作中断状态寄存器的读完成标志位置位。

[0133]

5)从mmc core的读出数据寄存器中读取所读数据,单个块的数据量为512字节,故应读数据字节量为512*16(块数量)。

[0134]

6)改写mmc core内部的多块操作中断清除寄存器,使得多块操作中断状态寄存器复位。因为在上一步中多块操作中断状态寄存器的读完成标志位已经置位,因此需要将其复位,这样在下一次多块读操作时多块操作中断状态寄存器仍然可以正确的提示读操作完成情况。

[0135]

7)读操作完成。

[0136]

完整的存储流程结合图1低功耗大容量存储方法的示意图和图2sram和flash组合存储数据流过程可知。上电后启动一次emmc flash初始化。自容式仪器作业过程中,数据首先缓存在sram中,每当sram接近满之后触发转运过程,发起一次flash写操作请求。emmc flash写操作为单块写方式。写操作请求发起后,从sram读出一个块的数据并存入转运fifo。转运fifo用于sram和emmc flash之间的跨时钟域同步和数据缓存。emmc flash写控制模块收到flash写操作请求执行写操作,并将转运fifo中的一块数据写入emmc flash。如此循环执行转运直到sram接近空则此次转运完成,flash自动进入休眠,直到下一次sram接近满触发转运过程时被唤醒。当从sram读数据操作时,待存储的数据暂存在fpga内部的小容量fifo中。当自容式仪器回收到地面后,将通过多块读的方式快速将工作期间记录的数据读出。

[0137]

综上所述,本发明提出的一种超低功耗的大容量存储方法具有存储容量大、功耗低的优点,解决自容式仪器在低功耗设计和大容量数据存储等场景需求的问题,典型应用场景如深海水温水深监测仪、海底节点地震勘探仪器、移动式数字地震仪等。本发明专利选用emmc flash芯片作为存储器件,emmc flash芯片的存储容量从8gb到128gb不等,可以适配自容式仪器不同的数据量需求。自容式仪器常规存储大量数据的做法是使用soc控制emmc flash功耗在几百毫瓦,而本发明专利的显著优势是低功耗。本发明专利中的三种关键技术都大幅降低了功耗。第一,应用sram芯片+emmc flash芯片组合的方式极大地降低emmc flash芯片本身的功耗,应用该技术可以将存储芯片的功耗从几百毫瓦降低到10mw以内。第二,采用基于flash架构的fpga降低主控制器的功耗。根据microsemi公司的测试结论,基于flash架构的fpga比基于sram架构的fpga功耗低30%到50%。实现了fpga硬件逻辑实时控制emmc flash,比soc软件控制emmc flash进一步降低了主控制器的功耗。

[0138]

以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1