传感器装置的制作方法

1.本公开涉及一种传感器装置。

背景技术:

2.作为对诸如固态成像元件等传感器元件进行冷却的手段,已知的是内置有珀耳帖(peltier)元件的气密性密封封装(例如,参见专利文献1)。

3.引用文献列表

4.专利文献

5.专利文献1:jp 2003-258221 a

技术实现要素:

6.技术问题

7.本公开提出了一种能够提高检测感度的传感器装置。

8.问题的解决方案

9.根据本公开,提供了一种传感器装置。所述传感器装置包括珀耳帖元件;热连接到所述珀耳帖元件的冷却面的传感器元件;和面对所述传感器元件的受光面并由硼硅酸盐玻璃制成的窗构件。

附图说明

10.图1是示出根据本公开实施方案的传感器元件的示意性构成的图。

11.图2是示出根据本公开实施方案的传感器元件的各像素的像素电路的图。

12.图3是示出根据本公开实施方案的像素的结构的截面图。

13.图4是示出电荷发出像素的像素配置的像素阵列区域的平面图。

14.图5是示出根据本公开实施方案的传感器元件的示意性截面构成的图。

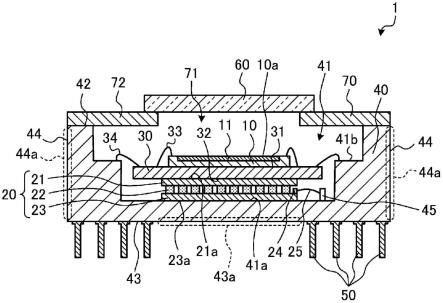

15.图6是示出根据本公开实施方案的传感器装置的构成例的截面图。

16.图7是示出根据本公开实施方案的传感器装置的构成例的仰视图。

17.图8是示出根据本公开实施方案的珀耳帖元件的冷却基板的构成例的俯视图。

18.图9是示出根据本公开实施方案的珀耳帖元件的散热基板的构成例的俯视图。

19.图10是示出根据本公开实施方案的珀耳帖元件的构成例的俯视图。

20.图11是示出实施例和参考例的窗构件的透过率的波长依赖性的图。

21.图12是示出根据本公开实施方案的变形例1的传感器装置的构成例的截面图。

22.图13是示出根据本公开实施方案的变形例2的传感器装置的构成例的截面图。

23.图14是示出根据本公开实施方案的变形例3的传感器装置的构成例的仰视图。

24.图15a是示出根据本公开实施方案的其他示例的传感器元件的基板构成的图。

25.图15b是示出根据本公开实施方案的其他示例的传感器元件的基板构成的图。

26.图16是示出根据本公开实施方案的其他示例的传感器元件的层叠基板的电路构

成例的图。

27.图17是示出根据本公开实施方案的其他示例的传感器元件的像素的等效电路的图。

28.图18是示出根据变形例4的电荷发出像素的像素配置的像素阵列区域的平面图。

29.图19是示出根据本公开实施方案的变形例4的像素的结构的截面图。

30.图20是示出根据本公开实施方案的变形例5的传感器装置的构成例的截面图。

31.图21是示出根据本公开实施方案的变形例6的传感器装置的构成例的截面图。

32.图22是示出根据本公开实施方案的变形例7的传感器装置的构成例的截面图。

33.图23是示出根据本公开实施方案的变形例8的传感器装置的构成例的截面图。

34.图24是示出根据本公开实施方案的变形例9的传感器装置的构成例的截面图。

35.图25是示出根据本公开实施方案的变形例10的传感器装置的构成例的截面图。

具体实施方式

36.在下文中,将参照附图详细说明本公开的各实施方案。注意,在以下的各实施方案中,对相同的部分标注相同的附图标记,并省略重复说明。

37.作为对诸如固态成像元件等传感器元件进行冷却的手段,已知的是内置有珀耳帖(peltier)元件的气密性密封封装。在气密性密封封装中,蓝宝石玻璃用作允许检测光透过内部的窗构件。

38.然而,在上述技术中,蓝宝石玻璃具有吸收率增大的波长区域,使得入射光被蓝宝石玻璃吸收。因此,存在检测感度降低的问题。

39.因此,期望实现能够克服上述问题并提高传感器装置的检测感度的技术。

40.[传感器元件的构成]

[0041]

首先,将参照图1~图5说明根据本实施方案的传感器元件10的构成。图1是示出根据本公开实施方案的传感器元件10的示意性构成的图。

[0042]

图1的传感器元件10包括:像素阵列区域103,其中像素102在使用例如单晶硅(si)作为半导体的半导体基板112上以矩阵状二维配置;和在其周边的周边电路区域161(参见图4)。周边电路区域161包括垂直驱动电路104、列信号处理电路105、水平驱动电路106、输出电路107、控制电路108等。

[0043]

像素102包括:由半导体薄膜制成的光电转换单元;和多个像素晶体管。多个像素晶体管包括例如复位晶体管、放大晶体管和选择晶体管这三个mos晶体管。

[0044]

控制电路108接收输入时钟和给出操作模式等指令的数据,并且输出诸如传感器元件10的内部信息等数据。即,控制电路238基于垂直同步信号、水平同步信号和主时钟生成作为垂直驱动电路234、列信号处理电路235、水平驱动电路236等的操作的基准的时钟信号和控制信号。

[0045]

然后,控制电路108将生成的时钟信号和控制信号输出到垂直驱动电路104、列信号处理电路105、水平驱动电路106等。

[0046]

垂直驱动电路104包括例如移位寄存器,选择预定的像素驱动配线 110,将用于驱动像素102的脉冲供给到选择的像素驱动配线110,并且以行为单位驱动像素102。

[0047]

即,垂直驱动电路104以行为单位在垂直方向上顺次选择性地扫描像素阵列区域

103中的各像素102。然后,垂直驱动电路104将基于根据各像素102的光电转换单元中的接收光量而产生的信号电荷的像素信号通过垂直信号线109供给到列信号处理电路105。

[0048]

列信号处理电路105针对像素102的每列配置,并且针对每列对从一行的像素102输出的信号执行诸如噪声去除等信号处理。例如,列信号处理电路105执行诸如相关双采样(cds)和ad转换等信号处理以去除各像素固有的固定模式噪声。

[0049]

水平驱动电路106包括例如移位寄存器,并且顺次输出水平扫描脉冲以顺次选择各个列信号处理电路105,从而使像素信号从各个列信号处理电路105输出到水平信号线111。

[0050]

输出电路107对从各个列信号处理电路105通过水平信号线111顺次供给的信号执行信号处理,并且输出经处理的信号。例如,输出电路 107可以仅进行缓冲,或者可以进行黑电平调整、列变化校正、各种数字信号处理等。输入/输出端子113与外部交换信号。

[0051]

如上所述构成的传感器元件10是被称为列ad方式的cmos图像传感器,其中针对每列配置执行cds处理和ad转换处理的列信号处理电路105。

[0052]

图2是示出根据本公开实施方案的传感器元件10的各像素的像素电路的图。各像素102包括光电转换单元121、电容元件122、复位晶体管 123、放大晶体管124和选择晶体管125。

[0053]

光电转换单元121由使用诸如ingaas等化合物半导体的半导体薄膜制成,并且产生与接收光量相对应的电荷(信号电荷)。预定的偏置电压 va被施加到光电转换单元121。

[0054]

电容元件122累积在光电转换单元121中产生的电荷。电容元件122 可以包括例如pn结电容器、mos电容器或配线电容器中的至少一种。

[0055]

当由复位信号rst导通时,复位晶体管123将累积在电容元件122 中的电荷排出到源极(接地)而复位电容元件122的电位。

[0056]

放大晶体管124根据电容元件122的累积电位而输出像素信号。即,放大晶体管124构成经由垂直信号线109连接的作为恒电流源的负载 mos(未示出)和源极跟随器电路。

[0057]

结果,指示对应于累积在电容元件122中的电荷水平的像素信号被从放大晶体管124经由选择晶体管125输出到列信号处理电路105(参见图1)。

[0058]

选择晶体管125在像素102被选择信号sel选择时导通,并将像素 102的像素信号经由垂直信号线109输出到列信号处理电路105。传输信号trx、选择信号sel和复位信号rst通过其传输的各信号线对应于图1中的像素驱动配线110。

[0059]

图3是示出根据本公开实施方案的像素102的结构的截面图。尽管稍后将说明细节,但是像素阵列区域103内的各像素102根据图3中的复位晶体管123的控制差异被分为普通像素102a和电荷发出像素102b。

[0060][0061]

另一方面,普通像素102a和电荷发出像素102b的像素结构基本相同,因此下文中可以简单地作为像素102说明。注意,电荷发出像素102b 配置在像素阵列区域103(参见图1)的最外侧。

[0062]

图2中说明的各像素102的电容元件122、复位晶体管123、放大晶体管124和选择晶体管125的读出电路在由诸如单晶硅等单晶材料制成的半导体基板112上针对每个像素102形成。

[0063]

注意,图3未示出形成在半导体基板112上的电容元件122、复位晶体管123、放大晶体管124和选择晶体管125的附图标记。

[0064]

在半导体基板112的作为光入射侧的上侧,在像素阵列区域103的整个表面上形成作为光电转换单元121的n型半导体薄膜141。n型半导体薄膜141由ingap、inalp、ingaas、inalas或具有黄铜矿结构的化合物半导体制成。

[0065]

具有黄铜矿结构的化合物半导体是能够获得高的光吸收系数和在宽的波长范围内的高感度的材料,并且优选用作光电转换用的n型半导体薄膜141。

[0066]

这种具有黄铜矿结构的化合物半导体是使用诸如cu、al、ga、in、 s和se等iv族元素周围的元素构成的,并且其例子包括cugains系混晶、cualgains系混晶和cualgainsse系混晶等。

[0067]

此外,作为n型半导体薄膜141的材料,除了上述化合物半导体之外,还可以使用非晶硅、锗(ge)、量子点光电转换膜、有机光电转换膜等。注意,假设在本公开中使用ingaas的化合物半导体作为n型半导体薄膜141。

[0068]

在n型半导体薄膜141的作为半导体基板112侧的下侧,针对每个像素102形成构成像素电极的高浓度p型层142。此外,例如,在针对每个像素102分别形成的高浓度p型层142之间,使用诸如inp等化合物半导体形成隔离各像素102的作为像素分离区域的n型层143。n型层143不仅具有作为像素分离区域的功能,而且还具有防止暗电流的作用。

[0069]

另一方面,在n型半导体薄膜141的作为光入射侧的上侧,使用像素分离区域用的诸如inp等化合物半导体,形成具有比n型半导体薄膜 141更高浓度的n型层144。

[0070]

该高浓度n型层144用作防止在n型半导体薄膜141中产生的电荷逆向流动的阻挡层。作为高浓度n型层144的材料,例如,可以使用inp、 ingaas和inalas等化合物半导体。

[0071]

防反射膜145形成在作为阻挡层的高浓度n型层144上。作为防反射膜145的材料,例如,可以使用氮化硅(sin)、氧化铪(hfo2)、氧化铝 (al2o3)、氧化锆(zro2)、氧化钽(ta2o5)、氧化钛(tio2)等。

[0072]

高浓度n型层144或防反射膜145中的任一者还用作上下夹持n型半导体薄膜141的电极之中的上侧的上部电极,并且预定电压va被施加到作为上部电极的高浓度n型层144或防反射膜145。

[0073]

滤色器146和片上透镜147进一步形成在防反射膜145上。滤色器146是透过红色(r)、绿色(g)和蓝色(b)中的任一种的光(波长光)的滤波器,并且例如,在像素阵列区域103中以所谓的拜耳(bayer)阵列配置。

[0074]

钝化层151和绝缘层152形成在构成像素电极的高浓度p型层142 和作为像素分离区域的n型层143的下侧。此外,连接电极153a和153b 以及凸块电极154形成为贯通钝化层151和绝缘层152。

[0075]

连接电极153a和153b以及凸块电极154将构成像素电极的高浓度 p型层142与累积电荷的电容元件122电气连接。

[0076]

普通像素102a和电荷发出像素102b如上所述地构成,并且具有相同的像素结构。然而,控制复位晶体管123的方法在普通像素102a和电荷发出像素102b之间是不同的。

[0077]

在普通像素102a中,根据光电转换单元121的电荷产生期间(受光期间)、受光开始前的电容元件122的电位的复位期间等,复位晶体管123 基于复位信号rst而导通/断开。另

一方面,在电荷发出像素102b中,复位晶体管123被控制为始终导通。

[0078]

结果,在光电转换单元121中产生的电荷被排出到接地,并且恒定电压va总是被施加到电荷发出像素102b。

[0079]

图4是示出电荷发出像素102b的像素配置的像素阵列区域103的平面图。像素阵列区域103配置在形成有垂直驱动电路104、列信号处理电路105等的周边电路区域161的内侧。像素阵列区域103的最外侧的一行和一列被设置为电荷发出像素102b在其内配置的电荷发出区域162。

[0080]

注意,电荷发出区域162可以包括至少包含位于矩形的像素阵列区域103的最外侧的一行和一列的多行和多列。

[0081]

在位于矩形的像素阵列区域103的各边的最外侧的列和行中的像素102中,由于来自作为化合物半导体的光电转换单元121的加工部界面(加工部端面)的影响可能会产生暗电流,如图3所示。

[0082]

特别地,当形成在半导体基板112上的读出电路是源极跟随器型电路的情况下,像素的电位差随着电荷的累积而减小,因此暗电流成分由于光晕(blooming)而影响挨着的相邻像素。

[0083]

因此,在本实施方案中,位于矩形的像素阵列区域103的各边的最外侧的列和行中的像素102设定为被控制成使得复位晶体管123总是导通的电荷发出像素102b。

[0084]

结果,电荷从作为光电转换单元121的n型半导体薄膜141的加工部的端面(加工部界面)的喷出被集中并排出到电荷发出像素102b。结果,可以防止电荷流入电荷发出区域162内侧的普通像素102a。

[0085]

如上所述,根据本实施方案,可以抑制由于电荷从n型半导体薄膜 141的加工部界面的喷出而导致的图像质量劣化。

[0086]

图5是示出根据本公开实施方案的传感器元件10的示意性截面构成的图。传感器元件10例如适用于使用诸如iii-v族半导体等化合物半导体材料的红外传感器。

[0087]

例如,传感器元件10对于波长在可见区域(例如,380nm以上且小于780nm)到短红外区域(例如,780nm以上且小于2500nm)的光具有光电转换功能。传感器元件10例如设置有二维配置的多个受光单位区域(像素102)。图5示出了对应于三个像素102的部分的截面构成。

[0088]

传感器元件10具有元件基板180和电路板190的层叠结构。元件基板180的一个面是光入射面(光入射面s1),与光入射面s1相对的面(另一面)是与电路板190的接合面(接合面s2)。

[0089]

元件基板180从靠近电路板190的位置顺次具有第一电极181的配线层180w、半导体层180s、第二电极185和钝化膜186。

[0090]

半导体层180s具有被绝缘膜187覆盖的与配线层180w相对的表面和端面(侧面)。电路板190包括与元件基板180的接合面s2接触的配线层192w以及隔着配线层192w与元件基板180相对的支撑基板191。

[0091]

作为有效像素区域的元件区域r1设置在元件基板180的中央部,并且半导体层180s配置在元件区域r1中。换句话说,设置有半导体层180s 的区域是元件区域r1。

[0092]

围绕元件区域r1的周边区域r2设置在元件区域r1的外侧。在元件基板180的周边

区域r2中,埋入层188与绝缘膜187一起设置。在传感器元件10中,光从元件基板180的光入射面s1经由钝化膜186、第二电极185和第二接触层184入射到半导体层180s上。

[0093]

由半导体层180s光电转换的信号电荷经由配线层180w移动,并且被电路板190读出。在下文中,将说明每个部分的构成。

[0094]

配线层180w跨着元件区域r1和周边区域r2设置,并且具有与电路板190的接合面s2。在传感器元件10中,元件基板180的接合面s2 设置在元件区域r1和周边区域r2中。例如,元件区域r1的接合面s2 与周边区域r2的接合面s2构成同一平面。

[0095]

如后所述,在传感器元件10中,周边区域r2的接合面s2通过设置埋入层188而形成。

[0096]

配线层180w包括例如在层间绝缘膜189a和189b中的第一电极181 和接触电极189ea和189eb。例如,层间绝缘膜189b配置在电路板190 侧,层间绝缘膜189a配置在第一接触层182侧,并且这些层间绝缘膜189a和189b被层叠。

[0097]

层间绝缘膜189a和189b由例如无机绝缘材料制成。无机绝缘材料的示例包括氮化硅、氧化铝、氧化硅(sio2)和氧化铪等。层间绝缘膜189a 和189b可以由相同的无机绝缘材料制成。

[0098]

第一电极181是被供给用于读出在光电转换层183中产生的信号电荷(空穴或电子,在下文中,为方便起见,假定信号电荷作为空穴进行说明)的电压的电极(阳极),并且针对每个像素102设置在元件区域r1中。

[0099]

设置在配线层180w中的第一电极181经由层间绝缘膜189a和绝缘膜187的连接孔与半导体层180s(更具体地,后述的第一接触层182)接触。相邻的第一电极181由层间绝缘膜189b电气分离。

[0100]

第一电极181由例如钛、钨、氮化钛(tin)、铂和金、锗、钯、锌、镍和铝中的任何单质或者包含至少其中一种的合金制成。

[0101]

第一电极181可以是由这样的构成材料制成的单膜或者通过组合两种以上获得的层叠膜。例如,第一电极181由钛和钨的层叠膜制成。

[0102]

接触电极189ea被构造成将第一电极181和电路板190电气连接,并且针对元件区域r1中的每个像素102设置。相邻的接触电极189ea 由层间绝缘膜189b电气分离。

[0103]

接触电极189eb将第二电极185与电路板190的配线(后述的配线 192cb)电气连接,并且配置在周边区域r2中。例如,接触电极189eb 在与接触电极189ea相同的过程中形成。接触电极189ea和189eb使用例如铜(cu)焊盘构成并且露出于接合面s2。

[0104]

半导体层180s从更靠近配线层180w的位置开始包括例如第一接触层182、光电转换层183和第二接触层184。第一接触层182、光电转换层183和第二接触层184具有相同的平面形状,并且它们的端面在平面图中配置在相同的位置。

[0105]

第一接触层182例如对于所有像素102共用地设置,并且配置在绝缘膜187和光电转换层183之间。第一接触层182被构造成将相邻的像素102电气分离,并且第一接触层182设置有例如多个扩散区域182a。

[0106]

当使用带隙大于形成光电转换层183的化合物半导体材料的带隙的化合物半导体材料来形成第一接触层182时,也可以抑制暗电流。第一接触层182可以由例如n型inp制成。

[0107]

设置在第一接触层182上的扩散区域182a彼此分开地配置。扩散区域182a针对每

个像素102配置,并且第一电极181分别连接到各扩散区域182a。

[0108]

扩散区域182a被构造成针对每个像素102读出在光电转换层183 中产生的信号电荷,并且包含例如p型杂质。p型杂质的示例包括zn等。

[0109]

以这种方式,在扩散区域182a和扩散区域182a以外的第一接触层 182之间形成pn结界面,使得相邻的像素102电气分离。扩散区域182a 例如设置在第一接触层182的厚度方向上,并且还设置在光电转换层183 的厚度方向的一部分中。

[0110]

在第一电极181和第二电极185之间(更具体地,在第一接触层182 和第二接触层184之间)的光电转换层183例如对于所有像素102共用地设置。

[0111]

光电转换层183吸收预定波长的光以产生信号电荷,并且例如由诸如i-型的iii-v族半导体等化合物半导体材料制成。形成光电转换层183 的化合物半导体材料的示例包括ingaas、inassb、inas、insb、hgcdte 等。

[0112]

此外,光电转换层183可以由ge制成。光电转换层183能够将具有从可见区域到短红外区域的波长的光进行光电转换。

[0113]

例如,第二接触层184对于所有像素102共用地设置。第二接触层 184设置在光电转换层183和第二电极185之间,并且与两者接触。

[0114]

第二接触层184是从第二电极185排出的电荷在那里移动的区域,并且由例如含有n型杂质的化合物半导体制成。第二接触层184可以由例如n型inp制成。

[0115]

第二电极185与第二接触层184接触地设置在第二接触层184上(光入射侧),例如作为对于各像素102共用的电极。第二电极185被构造成排出在光电转换层183中产生的电荷之中的未用作信号电荷的电荷(阴极)。

[0116]

例如,当从第一电极181读出作为信号电荷的空穴时,可以通过例如第二电极185排出电子。第二电极185由能够透过诸如红外线等入射光的导电膜制成。第二电极185可以由例如氧化铟锡(ito)、itio (in2o

3-tio2)等制成。

[0117]

钝化膜186从光入射面s1侧覆盖第二电极185。钝化膜186可以具有防反射功能。钝化膜186可以由例如氮化硅、氧化铝、氧化硅、氧化钽等制成。

[0118]

绝缘膜187设置在第一接触层182和配线层180w之间,并且覆盖第一接触层182的端面、光电转换层183的端面、第二接触层184的端面和第二电极185的端面。此外,绝缘膜187在周边区域r2中与钝化膜 186接触。

[0119]

绝缘膜187例如包含诸如氧化硅(sio

x

)和氧化铝等氧化物。可以使用包括多个膜的层叠结构来形成绝缘膜187。

[0120]

绝缘膜187可以由例如硅(si)系绝缘材料制成,例如氧氮化硅 (sion)、含碳氧化硅(sioc)、氮化硅和碳化硅(sic)。

[0121]

埋入层188被构造成在传感器元件10的制造过程中填充临时基板 (未示出)和半导体层180s之间的台阶。由于在本实施方案中形成埋入层 188,因此由半导体层180s和临时基板之间的台阶引起的制造过程中的缺陷的发生被抑制,后面将说明细节。

[0122]

周边区域r2中的埋入层188设置在配线层180w和钝化膜186之间,并且具有例如半导体层180s的厚度以上的厚度。这里,埋入层188围绕半导体层180s,因此形成半导体层180s周围的区域(周边区域r2)。

[0123]

结果,可以在周边区域r2中设置与电路板190的接合面s2。埋入层188的厚度可以

减小,只要接合面s2形成在周边区域r2中,但优选的是,埋入层188在厚度方向上覆盖半导体层180s,使得半导体层180s 的整个端面被埋入层188覆盖。

[0124]

埋入层188隔着绝缘膜187覆盖半导体层180s的整个端面,从而有效地抑制水分进入半导体层180s。

[0125]

埋入层188的接合面s2侧的表面被平坦化,并且配线层180w在周边区域r2中设置在埋入层188的平坦化表面上。埋入层188例如可以由诸如氧化硅、氮化硅、氧氮化硅、含碳氧化硅和碳化硅等无机绝缘材料制成。

[0126]

埋入层188设置有贯通电极188v。贯通电极188v被构造成将第二电极185与电路板190的配线(后述的配线192cb)连接,并且部分地设置在钝化膜186上。

[0127]

贯通电极188v的一侧从钝化膜186上方贯通钝化膜186,并且连接到第二电极185。贯通电极188v的另一侧从钝化膜186上方贯通钝化膜 186、绝缘膜187、埋入层188和层间绝缘膜189a,并且连接到接触电极 189eb。

[0128]

电路板190的支撑基板191被构造成支撑配线层192w,并且由例如硅(si)制成。配线层192w包括例如在层间绝缘膜192a中的接触电极 192ea和192eb、像素电路192ca、配线192cb和焊盘电极192p。

[0129]

层间绝缘膜192a由例如无机绝缘材料制成。无机绝缘材料的示例包括氮化硅、氧化铝、氧化硅和氧化铪等。

[0130]

接触电极192ea被构造成将第一电极181和像素电路192ca电气连接,并且在元件基板180的接合面s2处与接触电极189ea接触。相邻的接触电极192ea由层间绝缘膜192a电气分离。

[0131]

接触电极192eb被构造成将第二电极185和电路板190的配线 192cb电气连接,并且在元件基板180的接合面s2处与接触电极189eb 接触。接触电极192eb例如在与接触电极192ea相同的过程中形成。

[0132]

贯通电极188v可以在未设置接触电极189eb和192eb的情况下连接到配线192cb。接触电极192ea和192eb例如由铜焊盘制成,并且露出于电路板190的面对元件基板180的面。

[0133]

即,例如,cu-cu接合形成在接触电极189ea和接触电极192ea之间以及在接触电极189eb和接触电极192eb之间。

[0134]

像素电路192ca针对每个像素102设置,并且与接触电极192ea 连接。像素电路192ca构成roic。连接到接触电极192eb的配线192cb 例如连接到预定电位。

[0135]

以这种方式,在光电转换层183中产生的电荷中的一种(例如,空穴) 从第一电极181经由接触电极189ea和192ea读出到像素电路192ca。

[0136]

此外,在光电转换层183中产生的电荷中的另一种(例如,电子)从第二电极185经由贯通电极188v和接触电极189eb和192eb排出到预定电位。

[0137]

焊盘电极192p被构造成用于与外部电气连接。传感器元件10设置有贯通元件基板180并到达焊盘电极192p的孔h,并且经由该孔h实现与外部的电气连接。例如,通过诸如引线接合或凸块等方法来实现连接。

[0138]

[传感器装置的构成]

[0139]

接下来,将说明根据本实施方案的传感器装置1的构成。图6是示出根据本公开实

施方案的传感器装置1的构成例的截面图,图7是示出根据本公开实施方案的传感器装置1的构成例的仰视图。

[0140]

根据本实施方案的传感器装置1是具有内部被气密性密封的封装结构并且由内部的传感器元件10接收透过窗构件60的光的传感器装置。注意,在以下的说明中,为了便于表示上下方向,将传感器装置1中设置有窗构件60的一侧定义为上侧。

[0141]

如图6所示,根据本实施方案的传感器装置1包括传感器元件10、珀耳帖元件20、中继基板30、封装基板40、多个针脚端子50、窗构件 60和支撑构件70。多个针脚端子50对应于外部端子的示例。

[0142]

传感器元件10在作为主面(图中的上面)的受光面10a上具有有效像素区域11。将接收到的光转换成电气信号的多个像素102(参见图1)形成在有效像素区域11中。

[0143]

根据本实施方案的传感器元件10例如是诸如ingaas图像传感器等短波红外(short wave infrared,swir)图像传感器。即,根据本实施方案的传感器元件10具有将包含短波红外区域的光(例如,波长为400nm~2500 nm的光)转换为电气信号的像素。

[0144]

珀耳帖元件20包括冷却基板21、柱状部22和散热基板23,并且冷却基板21、柱状部22和散热基板23从上方顺次层叠。

[0145]

图8是示出根据本公开实施方案的珀耳帖元件20的冷却基板21的构成例的俯视图。如图8所示,在冷却基板21的面对柱状部22的面(图 6中的下面)上形成有使用铜薄膜等形成的具有预定图案的金属层ml1。注意,为了便于理解,图8示出了俯视图中的金属层ml1的配置。

[0146]

图9是示出根据本公开实施方案的珀耳帖元件20的散热基板23的构成例的俯视图。如图9所示,在散热基板23的面对柱状部22的面(图 6中的上面)上形成有使用铜薄膜等形成的具有预定图案的金属层ml2。此外,在散热基板23中的金属层ml2的预定部位设置有一对电极24。

[0147]

然后,柱状部22被夹在图8所示的冷却基板21和图9所示的散热基板23之间,由此形成如图10所示的珀耳帖元件20。图10是示出根据本公开实施方案的珀耳帖元件20的构成例的俯视图。

[0148]

如图10所示,冷却基板21的金属层ml1和散热基板23的金属层 ml2对准,并且柱状部22配置在金属层ml1和金属层ml2这二者被配置的部位。

[0149]

结果,在珀耳帖元件20的内部,由金属层ml1、金属层ml2和柱状部22形成的一笔画的(unicursal)电气电路形成在一个电极24和另一个电极24之间。

[0150]

此外,柱状部22包括柱状的p型热电半导体和柱状的n型热电半导体。p型热电半导体和n型热电半导体的各自一端与金属层ml1连接,另一端与金属层ml2连接。然后,柱状部22的p型热电半导体和n型热电半导体经由金属层ml1和金属层ml2交替地串联连接。

[0151]

结果,当在珀耳帖元件20中直流电流从n型热电半导体侧流动时,冷却基板21从冷却面21a(参见图6)吸收热量以将其冷却,并且散热基板23将冷却基板21吸收的热量从散热面23a(参见图6)散发出去。

[0152]

冷却面21a是冷却基板21的与接合有柱状部22的面(即,配置有金属层ml1的面)相对侧的面。散热面23a是散热基板23的与接合有柱状部22的面(即,配置有金属层ml2的面)相对侧的面。

[0153]

返回到图6进行说明。中继基板30配置在珀耳帖元件20的冷却面 21a和传感器元件10之间。例如,传感器元件10经由粘合剂(未示出)等与中继基板30的前面31接合,并且珀耳帖元件20的冷却面21a经由粘合剂(未示出)等与中继基板30的背面32接合。

[0154]

结果,传感器元件10经由中继基板30与珀耳帖元件20的冷却面 21a热连接。

[0155]

此外,中继基板30在表面或内部具有配线层(未示出),并且通过该配线层来中继传感器元件10和封装基板40之间的电气连接。

[0156]

例如,中继基板30的配线层和传感器元件10通过接合导线33电气连接。此外,中继基板30的配线层和设置在封装基板4的台阶部41b中的接合焊盘(未示出)通过接合导线34电气连接。结果,中继基板30可以中继传感器元件10和封装基板40之间的电气连接。

[0157]

中继基板30例如是由陶瓷制成的插入基板。此外,中继基板30不限于由陶瓷制成的基板,并且可以是由树脂等制成的印刷基板。

[0158]

封装基板40由诸如氧化铝(al2o3)、氮化铝(aln)和氮化硅(si3n4)等具有高热导率的陶瓷制成,并且收容传感器元件10、珀耳帖元件20和中继基板30。

[0159]

封装基板40是由诸如氧化铝等陶瓷制成的多层基板,并且例如是针栅阵列(pga)基板。如图6所示,封装基板40具有第一面(例如,上面42) 和位于第一面的相对侧的第二面(例如,底面43)。

[0160]

在封装基板40中,在位于上面42和底面43之间的内部以多层设置多个配线。这些配线连接到设置在封装基板40的底面43上的多个端子 (例如,针脚端子50)。

[0161]

例如,封装基板40具有大致长方体形状,并且在上面42形成有凹部41。然后,珀耳帖元件20、中继基板30和传感器元件10从下方顺次层叠在凹部41的底面41a上。

[0162]

此外,凹部41在比底面41a高的位置设置有台阶部41b。然后,设置在台阶部41b处的接合焊盘和中继基板30的对应配线层通过接合导线 34电气连接。

[0163]

此外,设置在台阶部41b处的接合焊盘经由形成在封装基板40的表面或内部的配线层(未示出)电气连接到设置在封装基板40的底面43上的针脚端子50。即,封装基板40具有将中继基板30和针脚端子50之间的电气连接进行中继的中继基板的功能。

[0164]

以这种方式,由于在台阶部41b处形成接合焊盘,因此可以缩短接合焊盘和中继基板30之间的距离。结果,可以缩短接合导线34的长度,使得可以降低封装基板40和中继基板30之间的配线电阻。

[0165]

因此,根据本实施方案,可以提高传感器装置1的电气特性。

[0166]

封装基板40的底面43和多个侧面44中的每一个是大致平坦的。如图7所示,多个针脚端子50以矩阵状并排配置在封装基板40的底面43 上,并且在未配置多个针脚端子50的区域中设置有平坦的底部散热区域 43a。

[0167]

此外,如图6所示,在封装基板40的多个侧面44上分别设置有平坦的侧部散热区域44a。

[0168]

针脚端子50由导电材料(例如,金属)制成并且呈大致圆柱状。然后,针脚端子50的一端与从封装基板40的底面43露出的配线层电气和机械地连接,并且针脚端子50从底面43向下延伸。

[0169]

在本实施方案中,当多个针脚端子50电气连接到外部装置(未示出) 时,电力、控制信号等从外部装置输入到传感器装置1,并且来自传感器元件10的电气信号被输出到外

部装置。

[0170]

注意,通过设置在封装基板40中的凹部41的底面41a上的端子45 和连接到端子45的接合导线25,从外部装置向珀耳帖元件20的电极24 进行电力供给。

[0171]

窗构件60被设置成面对传感器元件10的受光面10a(即,有效像素区域11),并且由作为透光材料的硼硅酸盐玻璃制成。在根据本实施方案的传感器装置1中,透过窗构件60的光被传感器元件10的有效像素区域11接收。

[0172]

支撑构件70配置在传感器元件10和窗构件60之间,并且支撑窗构件60。支撑构件70具有开口部71和框架部72。开口部71形成为面对传感器元件10的受光面10a(即,有效像素区域11),并允许入射光通过。框架部72具有框架形状,配置成围绕开口部71,并且支撑窗构件60。

[0173]

然后,窗构件60附接到支撑构件70以覆盖开口部71,从而由支撑构件70支撑。窗构件60和支撑构件70使用低熔点玻璃等无间隙地彼此接合。

[0174]

此外,支撑构件70接合到封装基板40的上面42以覆盖封装基板 40的凹部41。支撑构件70和封装基板40使用现有的方法无间隙地接合。

[0175]

以这种方式,由于窗构件60和支撑构件70无间隙地接合并且支撑构件70和封装基板40无间隙地接合,因此封装基板40的凹部41的内部可以被气密性地密封在传感器装置1中。

[0176]

注意,在气密性地密封封装基板40的凹部41的内部的情况下,优选的是,执行气密性密封使得凹部41的内部处于低湿度状态。此外,支撑构件70可以由诸如金属材料和陶瓷材料等各种材料制成。

[0177]

在上述根据本实施方案的传感器装置1中,通过使用硼硅酸盐玻璃形成窗构件60,可以提高传感器装置1的检测感度。

[0178]

图11是示出实施例和参考例的窗构件60的透过率的波长依赖性的图。图11示出了作为实施例的由硼硅酸盐玻璃制成的窗构件60的透过率,并且示出了作为参考例的由蓝宝石玻璃制成的窗构件60的透过率。

[0179]

如图11所示,在参考例的窗构件60中,在可见区域和短波红外区域(例如,400nm~2500nm的波长)中存在透过率降低的区域。另一方面,在实施例的窗构件60中,透过率在整个可见区域和短波红外区域中显示出稳定的高值。

[0180]

以这种方式,由于窗构件60由透过率在整个可见区域和短波红外区域中显示出稳定的高值的硼硅酸盐玻璃制成,因此可以增加在整个可见区域和短波红外区域中传感器元件10中的接收光量。

[0181]

因此,根据本实施方案,可以提高传感器装置1的检测感度。

[0182]

此外,在本实施方案中,窗构件60由结晶各向同性的硼硅酸盐玻璃制成,因此可以抑制光学特性(例如,透过率)受到结晶的轴方向的影响。因此,根据本实施方案可以实现光学特性的偏差小的传感器装置1。

[0183]

此外,在本实施方案中,窗构件60由热膨胀系数小且韧性高的硼硅酸盐玻璃制成,因此可以提高传感器装置1的热冲击性。

[0184]

此外,在本实施方案中,窗构件60由加工比较容易的硼硅酸盐玻璃制成,因此可以降低传感器装置1的加工成本。

[0185]

此外,在本实施方案中,优选在传感器装置1中设置有包括开口部 71和框架部72并支撑窗构件60的支撑构件70。结果,与窗构件60直接接合到封装基板40的上面42的情况相比,可以减小比较容易破裂的窗构件60的面积,因此可以抑制由于窗构件60的破裂造成的传感器装置1的缺陷。

[0186]

因此,根据本实施方案,可以提高传感器装置1的可靠性。

[0187]

此外,在本实施方案中,框架部72在平面图中可以配置在有效像素区域11的外侧,并且开口部71的面积可以大于有效像素区域11的面积。例如,在本实施方案中,开口部71相对于有效像素区域11的开口角度优选为30

°

以上。

[0188]

结果,来自传感器装置1的检测对象的光可以被引导到有效像素区域11而不被支撑构件70阻挡。因此,根据本实施方案可以稳定地检测到检测对象。

[0189]

此外,在本实施方案中,窗构件60优选配置成覆盖开口部71。即,在本实施方案中,窗构件60的面积优选大于开口部71的面积。结果,可以增大窗构件60和支撑构件70之间的盈余部分,因此可以抑制窗构件60和支撑构件70之间间隙的产生。

[0190]

因此,根据本实施方案,可以稳定地进行封装基板40的凹部41的内部的气密性密封。注意,根据本实施方案的窗构件60不限于以覆盖开口部71的方式配置的情况,也可以将与开口部71大致相等尺寸的窗构件60配置为嵌入开口部71。

[0191]

此外,在本实施方案中,传感器元件10热连接到珀耳帖元件20的冷却面21a。因此,即使在使用诸如swir图像传感器等在操作期间产生高热量的传感器元件10的情况下,传感器元件10也可以稳定地操作。

[0192]

此外,在本实施方案中,如图6所示,珀耳帖元件20的冷却面21a 优选比与传感器元件10的受光面10a相对的面大。即,珀耳帖元件20 的冷却面21a优选在平面图中比传感器元件10大。

[0193]

结果,整个传感器元件10可以被珀耳帖元件20均匀地冷却,使得传感器元件10可以更稳定地操作。

[0194]

注意,图6的示例示出了珀耳帖元件20的冷却面21a在平面图中比传感器元件10大的情况。然而,珀耳帖元件20的冷却面21a可以具有与传感器元件10的尺寸大致相等的尺寸,或者如图12所示,珀耳帖元件20的冷却面21a可以小于传感器元件10。图12是示出根据本公开实施方案的变形例1的传感器装置1的构成例的截面图。

[0195]

如图12所示,在平面图中,通过使珀耳帖元件20的冷却面21a比传感器元件10小,可以减小凹部41,从而可以使传感器装置1小型化。

[0196]

此外,在本实施方案中,优选的是,在收容传感器元件10和珀耳帖元件20的封装基板40中,封装基板40中的凹部41的底面41a与珀耳帖元件20的散热面23a热连接。

[0197]

结果,在气密性密封珀耳帖元件20和传感器元件10的传感器装置 1中,传感器元件10中产生的热量可以经由珀耳帖元件20和封装基板 40有效地散发到外部。

[0198]

此外,在本实施方案中,珀耳帖元件20和传感器元件10在低湿度状态下被气密性地密封,因此可以抑制当珀耳帖元件20的冷却面21a被冷却时在冷却面21a上产生结露。

[0199]

此外,在本实施方案中,封装基板40由陶瓷制成,使得传感器装置1的传感器元件10可以具有多个像素。其原因将在下文中说明。

[0200]

图13是示出根据本公开实施方案的变形例2的传感器装置1的构成例的截面图,并

且示出了包括金属制的封装基板90的传感器装置1。如图13所示,在变形例2的传感器装置1中,传感器元件10、珀耳帖元件 20和中继基板30被收容在金属制的封装基板90的凹部91中。

[0201]

此外,在凹部91的底面91a上设置有多个柱状的针脚端子95。注意,在针脚端子95和封装基板90之间设置有绝缘性密封构件96,以确保针脚端子95之间的绝缘性。

[0202]

此外,针脚端子95的一端从封装基板90的底面93向下方突出,并且针脚端子95的另一端通过凹部91内的接合导线34与中继基板30电气连接。

[0203]

这里,在图13的示例中,封装基板90由导电性的金属材料构成,因此需要确保各针脚端子95与密封构件96的绝缘性。即,在图13的示例中,需要用于设置密封构件96的空间,因此难以缩短相邻针脚端子95 之间的距离,从而难以在封装基板90上高密度地配置多个针脚端子95。

[0204]

另一方面,在图6的示例中,封装基板40由绝缘性陶瓷制成,因此不需要单独设置用于确保绝缘性的部件。因此,在图6的示例中,由于封装基板40由陶瓷制成,因此可以缩短相邻针脚端子50之间的距离。

[0205]

此外,在由陶瓷制成的封装基板40中,配线层可以三维地设置在封装基板40的内部,因此即使在大量的针脚端子50配置在底面43上的情况下,也可以对于所有的针脚端子50单独地进行配线。

[0206]

即,即使当在本实施方案中传感器元件10具有多个像素时,从所有像素输出的信号也可以被发送到对应的针脚端子50。因此,根据本实施方案,可以增加传感器装置1的传感器元件10的像素。

[0207]

注意,即使当如图13所示地传感器装置1的封装基板90由金属制成时,通过使用硼硅酸盐玻璃制作窗构件60,也可以提高传感器装置1 的检测感度。

[0208]

此外,在图7所示的实施方案中,多个针脚端子50和珀耳帖元件20优选设置在平面图中的不同位置。结果,散热装置(未示出)可以在底面43上直接附接在对应于珀耳帖元件20的位置(即,珀耳帖元件20的正下方)。

[0209]

即,在本实施方案中,从珀耳帖元件20的散热面23a传递到封装基板40的底面43的热量可以被散热装置散发出去而不受针脚端子50的阻碍。因此,根据本实施方案,可以提高传感器装置1的散热性。

[0210]

此外,在本实施方案中,如图7所示,优选在封装基板40的底面 43上在对应于珀耳帖元件20的位置处设置比珀耳帖元件20更宽且更平坦的底部散热区域43a。

[0211]

结果,可以在底部散热区域43a中设置面积比珀耳帖元件20大的散热装置,从而可以进一步提高传感器装置1的散热性。

[0212]

此外,在本实施方案中,如图7所示,多个针脚端子50可以沿着底面43的彼此相对的两边设置。结果,散热装置可以配置为从封装基板40 突出,从而可以进一步提高传感器装置1的散热性。

[0213]

注意,底部散热区域43a不限于比珀耳帖元件20宽的情况,并且如图14所示,可以具有与珀耳帖元件20的尺寸大致相等的尺寸。图14是示出根据本公开实施方案的变形例3的传感器装置1的构成例的仰视图。

[0214]

如图14所示,即使底部散热区域43a的尺寸与珀耳帖元件20的尺寸大致相等,底部

散热区域43a也被配置成与珀耳帖元件20重叠,使得来自珀耳帖元件20的热量可以通过散热装置无任何问题地散发出去。

[0215]

此外,在本实施方案中,如图14所示,多个针脚端子50也可以在平面图中围绕珀耳帖元件20设置。结果,可以在封装基板40上设置多个针脚端子50,从而散热装置可以配置为从封装基板40突出。因此,根据图14的示例,传感器装置1的传感器元件10的像素可以进一步增加。

[0216]

此外,在本实施方案中,如图6所示,可以在封装基板40的侧面 44上设置平坦的侧部散热区域44a。结果,可以在侧部散热区域44a中设置散热装置(未示出),从而可以进一步提高传感器装置1的散热性。

[0217]

注意,在本实施方案中已经说明了在封装基板40的底面43和侧面44上设置平坦的底部散热区域43a和侧部散热区域44a的示例,但是底部散热区域43a和侧散热区域44a不限于平坦的情况。

[0218]

例如,当在底部散热区域43a和侧部散热区域44a中设置凹凸时,可以增加底部散热区域43a和侧部散热区域44a的表面积,因此可以在不单独设置散热装置的情况下提高传感器装置1的散热性。

[0219]

此外,在本实施方案中,优选设置中继封装基板40和传感器元件 10之间的电气连接的中继基板30。结果,可以使封装基板40和传感器元件10之间的配线的厚度比接合导线33和34厚,从而可以降低封装基板40和传感器元件10之间的配线电阻。

[0220]

因此,根据本实施方案,可以提高传感器装置1的电气特性。此外,在本实施方案中,通过在中继基板30上安装各种安装部件(例如,电容器、电阻器等),可以使传感器装置1多功能化。

[0221]

此外,在本实施方案中,传感器元件10优选是swir图像传感器。结果,传感器装置1可以执行利用波长比可见光更长的光的感测。

[0222]

注意,根据本实施方案的传感器元件10不限于swir图像传感器。例如,根据本实施方案的传感器元件10可以是互补金属氧化物半导体 (cmos)图像传感器、电荷耦合器件(ccd)图像传感器等,其具有将可见区域中的光转换为电气信号的像素。

[0223]

接下来,将参照图115a~17说明根据本实施方案的传感器元件是具有将可见区域中的光转换为电气信号的像素的cmos图像传感器的情况。

[0224]

图15a和图15b是示出根据本公开实施方案的其他示例的传感器元件10a的基板构成的图。传感器元件10a(参照图16)是其中封装有通过层叠下侧基板211和上侧基板212而形成的层叠基板213的半导体封装。

[0225]

上侧基板212的上表面上形成有红色(r)、绿色(g)或蓝色(b)的滤色器(未示出)和片上透镜(未示出)。此外,上侧基板212经由被构造成保护片上透镜的玻璃保护基板(未示出)和玻璃密封树脂(未示出)以无空腔结构连接。

[0226]

例如,如图15a所示,其中执行光电转换的像素单元二维排列的像素区域221以及控制像素单元的控制电路222形成在上侧基板212上。此外,诸如处理从像素单元输出的像素信号的信号处理电路等逻辑电路 223形成在下侧基板211上。

[0227]

可选择地,如图15b所示,可以在上侧基板212上仅形成像素区域 221,并且控制电路222和逻辑电路223可以形成在下侧基板211上。

[0228]

如上所述,在本公开中,逻辑电路223或者控制电路222和逻辑电路223两者形成并层叠在与像素区域221的上侧基板212不同的下侧基板211上。结果,与像素区域221、控制电路222和逻辑电路223沿着平面方向配置在一个半导体基板上的情况相比,可以减小传感器元件10a 的尺寸。

[0229]

以下,将至少形成有像素区域221的上侧基板212称为像素传感器基板,将至少形成有逻辑电路223的下侧基板211称为逻辑基板。

[0230]

图16是示出根据本公开实施方案的其他示例的传感器元件10a的层叠基板213的电路构成例的图。层叠基板213包括其中各像素232以二维阵列状配置的像素阵列单元233、垂直驱动电路234、列信号处理电路235、水平驱动电路236、输出电路237、控制电路238、输入/输出端子239等。

[0231]

像素232包括作为光电转换元件的光电二极管和多个像素晶体管。稍后将参照图17说明像素232的电路构成例。

[0232]

此外,像素232也可以具有共享的像素结构。这种像素共享结构包括多个光电二极管、多个传输晶体管、一个共享浮动扩散部(浮动扩散区域)以及每个共享的其他像素晶体管。即,在共享像素中,构成多个单位像素的光电二极管和传输晶体管被构造成共享每个其他像素晶体管。

[0233]

控制电路238接收输入时钟和给出操作模式等指令的数据,并且输出诸如层叠基板213的内部信息等数据。即,控制电路238基于垂直同步信号、水平同步信号和主时钟生成作为垂直驱动电路234、列信号处理电路235、水平驱动电路236等的操作的基准的时钟信号和控制信号。

[0234]

然后,控制电路238将生成的时钟信号和控制信号输出到垂直驱动电路234、列信号处理电路235、水平驱动电路236等。

[0235]

垂直驱动电路234包括例如移位寄存器,选择预定的像素驱动配线 240,将用于驱动像素232的脉冲供给到选择的像素驱动配线240,并且以行为单位驱动像素232。

[0236]

即,垂直驱动电路234以行为单位在垂直方向上顺次选择性地扫描像素阵列单元233中的各像素232。然后,垂直驱动电路234将基于根据各像素232的光电转换单元中的接收光量而产生的信号电荷的像素信号通过垂直信号线241供给到列信号处理电路235。

[0237]

列信号处理电路235针对像素232的每列配置,并且针对每列对从一行的像素232输出的信号执行诸如噪声去除等信号处理。例如,列信号处理电路235执行诸如cds和ad转换等信号处理以去除各像素固有的固定模式噪声。

[0238]

水平驱动电路236包括例如移位寄存器,并且顺次输出水平扫描脉冲以顺次选择各个列信号处理电路235,从而使像素信号从各个列信号处理电路235输出到水平信号线242。

[0239]

输出电路237对从各个列信号处理电路235通过水平信号线242顺次供给的信号进行信号处理,并且输出经处理的信号。例如,输出电路 237可以仅执行缓冲,或者可以执行黑电平调整、列变化校正、各种数字信号处理等。输入/输出端子239与外部交换信号。

[0240]

如上所述构成的层叠基板213是被称为列ad方式的cmos图像传感器,其中针对每个像素列配置执行cds处理和ad转换处理的列信号处理电路235。

[0241]

图17是示出根据本公开实施方案的其他示例的传感器元件10a的像素232的等效

电路的图。图17中所示的像素232示出了实现电子式全局快门功能的构成。

[0242]

像素232包括光电二极管251、第一传输晶体管252、存储单元253、第二传输晶体管254、fd 255、复位晶体管256、放大晶体管257、选择晶体管258和排出晶体管259。注意,光电二极管251是光电转换元件的示例,fd 255是浮动扩散区域。

[0243]

光电二极管251是光电转换单元,其产生并累积与接收光量相对应的电荷(信号电荷)。光电二极管251的阳极端子接地,阴极端子经由第一传输晶体管252连接到存储单元253。此外,光电二极管251的阴极端子还连接到被构造成排出不必要的电荷的排出晶体管259。

[0244]

当被传输信号trx导通时,第一传输晶体管252读出由光电二极管 251产生的电荷并将其传输到存储单元253。存储单元253是临时保持电荷直到电荷被传输到fd 255时的电荷保持单元。

[0245]

当被传输信号trg导通时,第二传输晶体管254读出保持在存储单元253中的电荷并将其传输到fd 255。

[0246]

fd 255是电荷保持单元,其保持从存储器单元253读出的电荷以便作为信号读出电荷。当被复位信号rst导通时,随着累积在fd 2中的电荷55被排出到恒电压源vdd,复位晶体管256将fd 255的电位复位。

[0247]

放大晶体管257输出与fd 255的电位对应的像素信号。即,放大晶体管257与作为恒电流源的负载mos 260形成源极跟随器电路。

[0248]

然后,指示对应于累积在fd 255中的电荷水平的像素信号从放大晶体管257经由选择晶体管258输出到列信号处理电路235(参见图16)。负载mos 260例如配置在列信号处理电路235内。

[0249]

选择晶体管258在像素232被选择信号sel选择时导通,并且将像素232的像素信号经由垂直信号线241输出到列信号处理电路235。

[0250]

当被排出信号ofg导通时,排出晶体管259将累积在光电二极管 251中的不必要的电荷排出到恒电压源vdd。传输信号trx和trg、复位信号rst、排出信号ofg和选择信号sel经由像素驱动配线240 从垂直驱动电路234供给。

[0251]

接下来,将简要说明像素232的操作。首先,在开始曝光之前,通过将高电平的排出信号ofg供给到排出晶体管259使排出晶体管259导通,将累积在光电二极管251中的电荷排出到恒电压源vdd,并且所有像素的光电二极管251都被复位。

[0252]

在光电二极管251被复位后,当排出晶体管259被低电平的排出信号ofg断开时,在像素阵列单元233的所有像素中开始曝光。

[0253]

当经过预定的曝光时间时,在像素阵列单元233的所有像素中第一传输晶体管252被传输信号trx导通,并且累积在光电二极管251中的电荷被传输到存储单元253。

[0254]

在第一传输晶体管252断开之后,保持在各像素232的存储单元253 中的电荷以行为单位被顺次地读出到列信号处理电路235。在读出操作中,读出行的像素232的第二传输晶体管254被传输信号trg导通,并且保持在存储单元253中的电荷被传输到fd 255。

[0255]

然后,当选择晶体管258被选择信号sel导通时,指示对应于累积在fd 255中的电荷水平的信号从放大晶体管257经由选择晶体管258输出到列信号处理电路235。

[0256]

如上所述,在图17的示例中,可以执行全局快门方式的操作(成像),其中对于像素

阵列单元233的所有像素将曝光时间设定为相同,在曝光结束之后电荷临时保持在存储单元253中,并且以行为单位从存储单元 253顺次地读出电荷。

[0257]

注意,像素232的电路构成不限于图17中所示的构成。例如,也可以采用不包括存储单元253并且通过所谓的滚动快门方式执行操作的电路构成。

[0258]

[其他变形例]

[0259]

接下来,将参照图18~25说明根据本实施方案的其他变形例。图18 是示出根据变形例4的电荷发出像素的像素配置的像素阵列区域103的平面图。

[0260]

在变形例4中,检测用作基准的黑电平的光学黑(opb)区域形成作为像素阵列区域103的一部分。变形例4的像素结构是在opb区域形成为像素阵列区域103的一部分的情况下的像素结构。

[0261]

如图18所示,在opb区域163形成为像素阵列区域103的一部分的情况下,opb区域163包括位于矩形的像素阵列区域103的各边的最外侧的多列和多行。.然后,opb区域163中的最内侧的一行和一列被设定为电荷发出区域162。

[0262]

像素阵列区域103的opb区域163内侧的区域是有效像素区域,其中配置有输出与接收光量相对应的像素信号的普通像素102a(参见图 19)。

[0263]

图19是示出根据本公开实施方案的变形例4的像素102的结构的截面图。如图19所示,opb像素102c(102ca和102cb)配置在opb区域 163中。

[0264]

代替滤色器146和片上透镜147,opb像素102c具有形成在作为光电转换单元121的n型半导体薄膜141的上侧的遮光膜165。遮光膜165 例如由诸如钨、铝和金等金属材料构成。

[0265]

在opb区域163中,例如,形成三行或三列的三个opb像素102c 并排配置。然后,它们当中的最内侧的opb像素102c(靠近像素阵列区域103的中心)是用于电荷发出的opb像素102cb,类似于上述实施方案,其被控制为使得复位晶体管123始终导通。

[0266]

另一方面,形成三行或三列的三个opb像素102c并排配置的opb 区域163中的外侧的两个opb像素102c是被进行黑电平读出控制的用于黑电平读出的opb像素102ca。变形例4的其他构成类似于上述实施方案。

[0267]

例如,当传感器元件10的像素阵列区域103被高照度光照射时,在与opb区域163最相邻的普通像素102a中有时会出现光晕。然后,在这种情况下,存在着相邻的opb像素102c(即,opb区域163中的最内侧的opb像素102c)受到影响的可能性。

[0268]

此外,存在着入射在与opb区域163最相邻的普通像素102a上的光泄漏到相邻的opb像素102c中而在相邻的opb像素102c中出现光晕的可能性。

[0269]

因此,在变形例4中,opb区域163中的最内侧的opb像素102c 设定为被控制成使得复位晶体管123始终导通的用于电荷发出的opb像素102cb。

[0270]

结果,通过用于电荷发出的opb像素102cb可以防止出现光晕,并且可以防止电荷流入相邻的用于黑电平读出的opb像素102ca。因此,根据变形例4可以抑制由光晕的出现导致的图像质量劣化。

[0271]

此外,在上述实施方案中已经说明了传感器装置1的外部端子是针脚端子50的示例,但是传感器装置1的外部端子不限于针脚端子50。图 20是示出根据本公开实施方案的变形例5的传感器装置1的构成例的截面图。

[0272]

如图20所示,变形例5的传感器装置1与本实施方案的传感器装置 1的不同之处在于,代替针脚端子50,设置连接器98作为外部端子。连接器98设置在与底面43上的珀耳帖元件20相对应的位置(即,珀耳帖元件20的正下方)不同的位置,并且与从封装基板40的底面43露出的配线层电气连接。

[0273]

在变形例5中,当连接器98电气连接到外部装置(未示出)时,电力、控制信号等从外部装置输入到传感器装置1,并且来自传感器元件10的电气信号被输出到外部装置。

[0274]

在变形例5中,使用连接器98构成外部端子,使得传感器装置1可以容易地附接到外部装置(未示出)。注意,在本公开中,传感器装置1 的外部端子不限于针脚端子50和连接器98,并且可以采用各种外部端子。

[0275]

图21是示出根据本公开实施方案的变形例6的传感器装置1的构成例的截面图。如图21所示,在变形例6的传感器装置1中,在封装基板 40的面对珀耳帖元件20的散热面23a的面(本公开中的底面41a)的至少一部分上设置有金属制的散热构件46。

[0276]

即,在变形例6的传感器装置1中,散热构件46露出于底面41a。注意,在变形例6的传感器装置1中,也可以在珀耳帖元件20的散热面 23a与底面41a之间夹入粘合剂等。

[0277]

散热构件46例如由诸如铜、铝和钨等高热导率的金属制成。即,在变形例6的封装基板40中,从珀耳帖元件20的散热面23a到底部散热区域43a的热传递路径的至少一部分由热导率比陶瓷高的金属制成。

[0278]

结果,可以提高从珀耳帖元件20的散热面23a到底部散热区域43a 的热传递效率。因此,根据变形例6,可以提高传感器装置1的散热性。

[0279]

此外,在变形例6中,散热构件46优选贯穿封装基板40的面对珀耳帖元件20的散热面23a的面(底面41a)与底面43之间。结果,可以降低从底面41a到底部散热区域43a的热阻,从而可以进一步提高传感器装置1的散热性。

[0280]

此外,在变形例6中,如图21所示,散热构件46优选设置在封装基板40的面对珀耳帖元件20的散热面23a的整个面上。结果,可以进一步降低从底面41a到底部散热区域43a的热阻,从而可以进一步提高传感器装置1的散热性。

[0281]

注意,散热构件46不限于设置在封装基板40的面对珀耳帖元件20 的散热面23a的整个面上的情况。图22是示出根据本公开实施方案的变形例7的传感器装置1的构成例的截面图。

[0282]

如图22所示,封装基板40可以设置有贯穿面对珀耳帖元件20的散热面23a的面(底面41a)与底面43之间的多个过孔状散热构件46。即使在图22所示的示例中,也可以降低从底面41a到底散热区域43a的热阻,从而可以进一步提高传感器装置1的散热性。

[0283]

注意,在变形例6和变形例7中已经说明了散热构件46由金属材料制成的示例,但是散热构件46不必限于金属材料,并且可以是热导率比形成封装基板40的陶瓷高的材料。例如,具有高热导率的陶瓷材料可以用作散热构件46。

[0284]

此外,在变形例6和变形例7中已经说明了散热构件46被设置为露出于封装基板40的面对珀耳帖元件20的散热面23a的面的示例,但是散热构件46不必露出于该表面。

[0285]

例如,散热构件46可以配置成埋在封装基板40中的珀耳帖元件20 的正下方。即,散热构件46可以配置成在平面图中与珀耳帖元件20重叠。结果,可以降低从底面41a到底部散热区域43a的热阻,从而可以进一步提高传感器装置1的散热性。

[0286]

此外,散热构件46也可以配置在珀耳帖元件20的正下方以外的部分的位置。

[0287]

图23是示出根据本公开实施方案的变形例8的传感器装置1的构成例的截面图。如图23所示,变形例8的传感器装置1与本实施方案的不同之处在于珀耳帖元件20的构成。

[0288]

具体地,在变形例8中,封装基板40与珀耳帖元件20的散热基板 23一体地构成。即,在变形例8中,图9所示的金属层ml2不是设置在散热基板23上,而是设置在封装基板40中的凹部41的底面41a上,并且柱状部22和冷却基板21层叠在底面41a的金属层ml2上而构成珀耳帖元件20。

[0289]

以这种方式,由于封装基板40与珀耳帖元件20的散热基板23一体地构成,因此可以降低散热基板23和封装基板40之间的界面处的热阻。此外,在变形例8中,可以省略散热基板23,从而可以缩短从传感器元件10到底部散热区域43a的热传递路径。

[0290]

因此,根据变形例8,可以提高传感器装置1的散热性。

[0291]

图24是示出根据本公开实施方案的变形例9的传感器装置1的构成例的截面图。如图24所示,变形例9的传感器装置1与本实施方案及变形例8的不同之处在于珀耳帖元件20的构成。

[0292]

具体地,在变形例9中,中继基板30与珀耳帖元件20的冷却基板 21一体地构成。即,在变形例9中,图8所示的金属层ml1不是设置在冷却基板21上,而是设置在中继基板30的背面32上,中继基板30进一步层叠在层叠的散热基板23和柱状部22上而构成珀耳帖元件20。

[0293]

以这种方式,由于中继基板30与珀耳帖元件20的冷却基板21一体地构成,因此可以降低中继基板30和冷却基板21之间的界面处的热阻。此外,在变形例9中,可以省略冷却基板21,从而可以缩短从传感器元件10到底部散热区域43a的热传递路径。

[0294]

因此,根据变形例9,可以提高传感器装置1的散热性。

[0295]

图25是示出根据本公开实施方案的变形例10的传感器装置1的构成例的截面图。如图25所示,变形例10的传感器装置1与本实施方案的不同之处在于未设置中继基板30。

[0296]

即,在变形例10中,传感器元件10直接接合到珀耳帖元件20的冷却面21a。此外,传感器元件10与封装基板40之间的电气连接通过接合导线33直接实现。

[0297]

由于在变形例10中可以省略中继基板30,因此可以缩短从传感器元件10到底部散热区域43a的热传递路径。因此,根据变形例10,可以提高传感器装置1的散热性。

[0298]

此外,在变形例10中,通过省略中继基板30,可以减小凹部41,从而可以使传感器装置1小型化。

[0299]

[效果]

[0300]

根据本实施方案的传感器装置1包括珀耳帖元件20;热连接到珀耳帖元件20的冷却面21a的传感器元件10(10a);和面对传感器元件10 (10a)的受光面10a并由硼硅酸盐玻璃制成的窗构件60。

[0301]

结果,可以提高传感器装置1的检测感度。

[0302]

此外,在根据本实施方案的传感器装置1中,在传感器元件10(10a) 的受光面10a上配置有接收来自窗构件60的入射光的有效像素区域11。

[0303]

结果,可以提高传感器装置1的检测感度。

[0304]

此外,根据本实施方案的传感器装置1还包括配置在传感器元件10 (10a)和窗构

件60之间的支撑构件70。此外,支撑构件70具有允许入射光通过的开口部71和支撑窗构件60的框架部72。

[0305]

结果,可以提高传感器装置1的可靠性。

[0306]

此外,在根据本实施方案的传感器装置1中,框架部72在平面图中配置在有效像素区域11的外侧。

[0307]

结果,可以稳定地检测检测对象。

[0308]

此外,在根据本实施方案的传感器装置1中,开口部71的面积大于有效像素区域11的面积。

[0309]

结果,可以稳定地检测检测对象。

[0310]

此外,在根据本实施方案的传感器装置1中,窗构件60被配置成覆盖开口部71。

[0311]

结果,可以稳定地执行封装基板40的凹部41的内部的气密性密封。

[0312]

此外,在根据本实施方案的传感器装置1中,珀耳帖元件20的冷却面21a大于传感器元件10(10a)的与受光面10a相对的面。

[0313]

结果,整个传感器元件10(10a)可以被珀耳帖元件20均匀地冷却,从而可以更稳定地操作传感器元件10(10a)。

[0314]

此外,根据本实施方案的传感器装置1还包括封装基板40,所述封装基板热连接到珀耳帖元件20的散热面23a并且收容珀耳帖元件20和传感器元件10(10a)。

[0315]

结果,在将珀耳帖元件20和传感器元件10(10a)气密性密封的传感器装置1中,传感器元件10(10a)中产生的热量可以经由珀耳帖元件20 和封装基板40有效地散发到外部。

[0316]

此外,本实施方案的传感器装置1还包括中继基板30,所述中继基板30配置在珀耳帖元件20的冷却面21a和传感器元件10(10a)之间,并且对封装基板40和传感器元件10(10a)之间的电气连接进行中继。

[0317]

因此,可以改善传感器装置1的电气特性。

[0318]

此外,在根据本实施方案的传感器装置1中,传感器元件10是swir 图像传感器。

[0319]

结果,利用波长比可见光更长的光的感测可以由传感器装置1执行。

[0320]

尽管关于本公开实施方案给出了以上说明,但是本公开的技术范围不限于上述实施方案,并且可以在不背离本公开范围的情况下进行各种修改。此外,可以适当地组合不同实施方案和变形例中的构成要素。

[0321]

例如,在上述实施方案中已经说明了其中封装基板40的端子45和珀耳帖元件20的电极24通过接合导线25电气连接的示例,但是端子45 和电极24不限于通过接合导线25连接的情况。例如,端子45和电极24 也可以通过引线等电气连接。

[0322]

此外,本说明书中记载的效果仅仅是示例性的,并不限制本文的公开内容,还可以实现本文中未记载的其他效果。

[0323]

注意,本技术还可以具有以下构成。

[0324]

(1)一种传感器装置,包括:

[0325]

珀耳帖元件;

[0326]

热连接到所述珀耳帖元件的冷却面的传感器元件;和

[0327]

面对所述传感器元件的受光面并由硼硅酸盐玻璃制成的窗构件。

[0328]

(2)根据上述(1)所述的传感器装置,其中

[0329]

在所述传感器元件的受光面上配置有接收来自所述窗构件的入射光的有效像素区域。

[0330]

(3)根据上述(2)所述的传感器装置,还包括

[0331]

配置在所述传感器元件和所述窗构件之间的支撑构件,

[0332]

其中所述支撑构件具有允许入射光通过的开口部和支撑所述窗构件的框架部。

[0333]

(4)根据上述(3)所述的传感器装置,其中

[0334]

所述框架部在平面图中配置在所述有效像素区域的外侧。

[0335]

(5)根据上述(3)或(4)所述的传感器装置,其中

[0336]

所述开口部的面积大于所述有效像素区域的面积。

[0337]

(6)根据上述(3)~(5)中任一项所述的传感器装置,其中

[0338]

所述窗构件被配置成覆盖所述开口部。

[0339]

(7)根据上述(1)~(6)中任一项所述的传感器装置,其中

[0340]

所述珀耳帖元件的冷却面大于所述传感器元件的与所述受光面相对的面。

[0341]

(8)根据上述(1)~(7)中任一项所述的传感器装置,还包括

[0342]

封装基板,所述封装基板热连接到所述珀耳帖元件的散热面并且收容所述珀耳帖元件和所述传感器元件。

[0343]

(9)根据上述(8)所述的传感器装置,还包括

[0344]

中继基板,所述中继基板配置在所述珀耳帖元件的冷却面和所述传感器元件之间,并且对所述封装基板和所述传感器元件之间的电气连接进行中继。

[0345]

(10)根据上述(1)~(9)中任一项所述的传感器装置,其中

[0346]

所述传感器元件是短波红外(swir)图像传感器。

[0347]

附图标记列表

[0348]

1 传感器装置

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

10,10a 传感器元件

[0349]

10a 受光面

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

11 有效像素区域

[0350]

20 珀耳帖元件

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

21 冷却基板

[0351]

21a 冷却面

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

22 柱状部

[0352]

23 散热基板

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

23a 散热面

[0353]

30 中继基板

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

40 封装基板

[0354]

41 凹部

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

41a 底面

[0355]

43 底面

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

43a 底部散热区域

[0356]

44 侧面

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

44a 侧部散热区域

[0357]

46 散热构件

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

50 针脚端子(外部端子的示例)

[0358]

60 窗构件

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

70 支撑构件

[0359]

71 开口部

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

72 框架部

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1