半导体装置、电子设备、车辆的制作方法

1.本说明书中公开的发明涉及半导体装置、电子设备以及车辆。

背景技术:

2.以往,大多数半导体装置具备过电流保护电路作为异常保护电路之一。例如,在车载ipd(intelligent power device,智能功率器件)中,设有将流向功率晶体管的输出电流限制为过电流设定值以下的过电流保护电路,以便即使在与功率晶体管连接的负载短路的情况下器件也不会被破坏。

3.此外,作为与上述相关的现有技术的一例,能够举出日本特开2015-46954号公报。

4.然而,在现有的半导体装置中,对于过电流保护电路的规模缩小(甚至产品价格低廉化),还有进一步研究的余地。

技术实现要素:

5.本说明书中公开的发明的目的在于,鉴于由本技术的发明者发现的上述课题,提供一种能够简易地实现过电流保护的半导体装置、电子设备以及车辆。

6.例如,本说明书中公开的半导体装置具有:栅极分割型的功率晶体管,其构成为,根据多个栅极控制信号对多个通道区域进行个别控制;栅极控制电路,其构成为,生成上述多个栅极控制信号;以及过电流保护电路,其构成为,当流向上述功率晶体管的输出电流超过阈值时,将上述多个通道区域的至少一个断开。

7.此外,对于本发明中的其它特征、要素、步骤、优点以及特性,根据以下接下来的最佳方式的详细的说明、与之相关的附图可更加清楚。

附图说明

8.图1是从一个方向观察半导体装置的立体图。

9.图2是表示半导体装置的电的构造的块电路图。

10.图3是用于说明半导体装置的通常动作以及有源钳位动作的电路图。

11.图4是主要的电信号的波形图。

12.图5是图1所示的区域v的剖面立体图。

13.图6是通过实际测量来调查有源钳位耐量以及面积电阻率的关系的图表。

14.图7是用于说明半导体装置的通常动作的剖面立体图。

15.图8是用于说明半导体装置的有源钳位动作的剖面立体图。

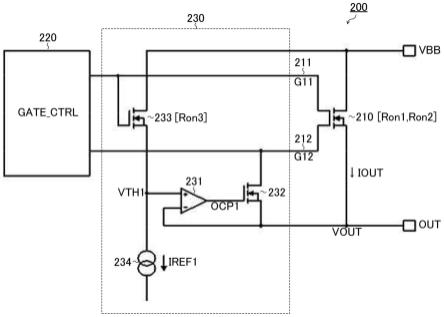

16.图9是表示过电流保护电路的第一构成例的图。

17.图10是表示第一构成例中的过电流保护动作的一例的图。

18.图11是表示过电流保护电路的第二构成例的图。

19.图12是表示第二构成例中的过电流保护动作的一例的图。

20.图13是表示车辆的一构成例的外观图。

具体实施方式

21.《半导体装置》

22.以下参照附图对半导体装置的各种实施方式进行说明。

23.图1是从一个方向观察半导体装置1的立体图。以下,对半导体装置1为高边侧的开关器件的方式例进行说明,但半导体装置1并不限定于高边侧的开关器件。半导体装置1通过对于各种构造的电的连接方式、功能进行调整,也能够作为低边侧的开关器件来提供。

24.参照图1,半导体装置1包括半导体层2。半导体层2包含硅。半导体层2形成为长方体形状的芯片状。半导体层2具有一方侧的第一主面3、另一方侧的第二主面4、以及连接第一主面3及第二主面4的侧面5a、5b、5c、5d。

25.第一主面3以及第二主面4在从它们的法线方向z观察的俯视(以下简称为“俯视”。)下形成四边形状。侧面5a以及侧面5c沿第一方向x延伸,在与第一方向x交叉的第二方向y上相互对置。侧面5b以及侧面5d沿第二方向y延伸,在第一方向x上相互对置。具体而言,第二方向y与第一方向x正交。

26.在半导体层2划分出输出区域6以及输入区域7。输出区域6划分为侧面5c侧的区域。输入区域7划分为侧面5a侧的区域。在俯视下,输出区域6的面积sout为输入区域7的面积sin以上(sin≤sout)。

27.面积sout与面积sin的比sout/sin也可以为1以上且10以下(1≤sout/sin≤10)。比sout/sin也可以为1以上且2以下、2以上且4以下、4以上且6以下、6以上且8以下、或者8以上且10以下。输入区域7的平面形状以及输出区域6的平面形状为任意的,并限定于特定的形状。当然,比sout/sin也可以超过0且小于1。

28.输出区域6包括作为绝缘栅极型的晶体管的一例的功率misfet(metal insulator semiconductor field effect transistor,金属绝缘体半导体场效应晶体管)9。功率misfet9包括栅极、漏极以及源极。

29.输入区域7包括作为控制电路的一例的控制器ic(integrated circuit,集成电路)10。控制器ic10包括实现各种功能的多种功能电路。多种功能电路包括基于来自外部的电信号生成对功率misfet9进行驱动控制的栅极控制信号的电路。控制器ic10与功率misfet9一起形成所谓ipd(intelligent power device,智能功率器件)。ipd也称为ipm(intelligent power module,智能功率模块)。

30.输入区域7通过区域分离构造8而与输出区域6电绝缘。在图1中,区域分离构造8由影线示出。虽然省略了具体的说明,但区域分离构造8也可以具有在沟槽中埋入绝缘体而成的沟槽绝缘构造。

31.在半导体层2之上,形成有多个(在该方式中为六个)电极11、12、13、14、15、16。在图1中,由影线示出多个电极11~16。多个电极11~16形成为通过导线(例如接合引线)等来进行外部连接的端子电极。多个电极11~16的个数、配置以及平面形状是任意的,不限定于图1所示的方式。

32.多个电极11~16的个数、配置以及平面形状根据功率misfet9的规格、控制器ic10的规格来调整。在该方式中,多个电极11~16包括漏电极11(电源电极)、源极电极12(输出

电极)、输入电极13、基准电压电极14、enable电极15以及sense电极16。

33.漏电极11形成于半导体层2的第二主面4之上。漏电极11与半导体层2的第二主面4电连接。漏电极11向功率misfet9的漏极、控制器ic10的各种电路传递电源电压vb。

34.漏电极11也可以包括ti层、ni层、au层、ag层以及al层中的至少一个。漏电极11也可以具有包括ti层、ni层、au层、ag层或者al层的单层构造。漏电极11也可以具有使ti层、ni层、au层、ag层以及al层中的至少两个以任意的形态层叠的层叠构造。

35.源极电极12在第一主面3形成于输出区域6之上。源极电极12与功率misfet9的源极电连接。源极电极12将由功率misfet9生成的电信号传递至外部。

36.输入电极13、基准电压电极14、enable电极15以及sense电极16在第一主面3分别形成于输入区域7之上。输入电极13传递用于驱动控制器ic10的输入电压。

37.基准电压电极14向控制器ic10传递基准电压(例如接地电压)。enable电极15传递用于使控制器ic10的一部分或者全部的功能有效或者无效的电信号。sense电极16传递用于检测控制器ic10的异常的电信号。

38.在半导体层2之上还形成有作为控制配线的一例的栅极控制配线17。栅极控制配线17选择性地引绕至输出区域6以及输入区域7。栅极控制配线17在输出区域6与功率misfet9的栅极电连接,在输入区域7与控制器ic10电连接。

39.栅极控制配线17将由控制器ic10生成的栅极控制信号传递至功率misfet9的栅极。栅极控制信号包括接通信号von以及断开信号voff,对功率misfet9的接通状态以及断开状态进行控制。

40.接通信号von比功率misfet9的栅极阈值电压vth高(vth<von)。断开信号voff比功率misfet9的栅极阈值电压vth低(voff<vth)。断开信号voff也可以是基准电压(例如接地电压)。

41.在该方式中,栅极控制配线17包括第一栅极控制配线17a、第二栅极控制配线17b以及第三栅极控制配线17c。第一栅极控制配线17a、第二栅极控制配线17b以及第三栅极控制配线17c相互电绝缘。

42.在该方式中,两个第一栅极控制配线17a引绕至不同的区域。另外,两个第二栅极控制配线17b引绕至不同的区域。另外,两个第三栅极控制配线17c引绕至不同的区域。

43.第一栅极控制配线17a、第二栅极控制配线17b以及第三栅极控制配线17c将相同或者不同的栅极控制信号传递至功率misfet9的栅极。栅极控制配线17的个数、配置、形状等是任意的,根据栅极控制信号的传递距离、应传递的栅极控制信号的个数来调整。

44.源极电极12、输入电极13、基准电压电极14、enable电极15、sense电极16以及栅极控制配线17也可以分别包含镍、钯、铝、铜、铝合金以及铜合金中的至少一种。

45.源极电极12、输入电极13、基准电压电极14、enable电极15、sense电极16以及栅极控制配线17也可以分别包含al-si-cu(铝-硅-铜)合金、al-si(铝-硅)合金、以及al-cu(铝-铜)合金中的至少一种。

46.源极电极12、输入电极13、基准电压电极14、enable电极15、sense电极16以及栅极控制配线17既可以包含同一种电极材料,也可以包含相互不同的电极材料。

47.图2是表示图1所示的半导体装置1的电的构造的块电路图。以下,以半导体装置1搭载于车辆的情况为例来进行说明。

48.半导体装置1包括漏电极11、源极电极12、输入电极13、基准电压电极14、enable电极15、sense电极16、栅极控制配线17、功率misfet9以及控制器ic10。

49.漏电极11与电源连接。漏电极11向功率misfet9以及控制器ic10提供电源电压vb。电源电压vb也可以为10v以上且20v以下。源极电极12与负载连接。

50.输入电极13也可以与mcu(micro controller unit)、dc/dc转换器、ldo(low drop out)等连接。输入电极13向控制器ic10提供输入电压。输入电压也可以为1v以上且10v以下。基准电压电极14与基准电压配线连接。基准电压电极14向功率misfet9以及控制器ic10提供基准电压。

51.enable电极15也可以与mcu连接。向enable电极15输入用于使控制器ic10的一部分或者全部的功能有效或者无效的电信号。sense电极16也可以与电阻器连接。

52.功率misfet9的栅极经由栅极控制配线17而与控制器ic10(后述的栅极控制电路25)连接。功率misfet9的漏极与漏电极11连接。功率misfet9的源极与控制器ic10(后述的电流检测电路27)以及源极电极12连接。

53.控制器ic10包括传感器misfet21、输入电路22、电流电压控制电路23、保护电路24、栅极控制电路25、有源钳位电路26、电流检测电路27、电源逆连接保护电路28以及异常检测电路29。

54.传感器misfet21的栅极与栅极控制电路25连接。传感器misfet21的漏极与漏电极11连接。传感器misfet21的源极与电流检测电路27连接。

55.输入电路22与输入电极13以及电流电压控制电路23连接。输入电路22也可以包括施密特触发器电路。输入电路22对施加于输入电极13的电信号的波形进行整形。由输入电路22生成的信号被输入至电流电压控制电路23。

56.电流电压控制电路23与保护电路24、栅极控制电路25、电源逆连接保护电路28以及异常检测电路29连接。电流电压控制电路23也可以包括逻辑电路。

57.电流电压控制电路23根据来自输入电路22的电信号以及来自保护电路24的电信号来生成各种电压。在该方式中,电流电压控制电路23包括驱动电压生成电路30、第一定电压生成电路31、第二定电压生成电路32以及基准电压

·

基准电流生成电路33。

58.驱动电压生成电路30生成用于驱动栅极控制电路25的驱动电压。驱动电压也可以设定为从电源电压vb减去预定值后的值。驱动电压生成电路30也可以生成从电源电压vb减去5v后的5v以上且15v以下的驱动电压。驱动电压被输入至栅极控制电路25。

59.第一定电压生成电路31生成用于驱动保护电路24的第一定电压。第一定电压生成电路31也可以包括齐纳二极管、调节器电路(在此为齐纳二极管)。第一定电压也可以为1v以上且5v以下。第一定电压被输入至保护电路24(具体而言,后述的负载开路检测电路35等)。

60.第二定电压生成电路32生成用于驱动保护电路24的第二定电压。第二定电压生成电路32也可以包括齐纳二极管、调节器电路(在此为调节器电路)。第二定电压也可以为1v以上且5v以下。第二定电压被输入至保护电路24(更具体而言,后述的过热保护电路36、低电压误动作抑制电路37)。

61.基准电压

·

基准电流生成电路33生成各种电路的基准电压以及基准电流。基准电压也可以为1v以上且5v以下。基准电流也可以为1ma以上且1a以下。基准电压以及基准电流

被输入至各种电路。在各种电路包括比较器的情况下,基准电压以及基准电流也可以被输入至该比较器。

62.保护电路24与电流电压控制电路23、栅极控制电路25、异常检测电路29、功率misfet9的源极以及传感器misfet21的源极连接。保护电路24包括过电流保护电路34、负载开路检测电路35、过热保护电路36以及低电压误动作抑制电路37。

63.过电流保护电路34保护功率misfet9免受过电流的影响。过电流保护电路34与栅极控制电路25以及传感器misfet21的源极连接。过电流保护电路34也可以包括电流监视电路。由过电流保护电路34生成的信号被输入至栅极控制电路25(更具体而言,后述的驱动信号输出电路40)。

64.负载开路检测电路35对功率misfet9的短路状态、打开状态进行检测。负载开路检测电路35与电流电压控制电路23以及功率misfet9的源极连接。由负载开路检测电路35生成的信号被输入至电流电压控制电路23。

65.过热保护电路36监视功率misfet9的温度,保护功率misfet9免受过度的温度上升的影响。过热保护电路36与电流电压控制电路23连接。过热保护电路36也可以包括感温二极管、热敏电阻等感温器件。由过热保护电路36生成的信号被输入至电流电压控制电路23。

66.低电压误动作抑制电路37抑制在电源电压vb小于预定值的情况下功率misfet9误动作。低电压误动作抑制电路37与电流电压控制电路23连接。由低电压误动作抑制电路37生成的信号被输入至电流电压控制电路23。

67.栅极控制电路25对功率misfet9的接通状态以及断开状态、以及传感器misfet21的接通状态以及断开状态进行控制。栅极控制电路25与电流电压控制电路23、保护电路24、功率misfet9的栅极以及传感器misfet21的栅极连接。

68.栅极控制电路25根据来自电流电压控制电路23的电信号以及来自保护电路24的电信号,来生成与栅极控制配线17的个数相应的多种栅极控制信号。多种栅极控制信号经由栅极控制配线17分别被输入至功率misfet9的栅极以及传感器misfet21的栅极。

69.具体叙述,栅极控制电路25具有对多个栅极控制信号进行个别控制的功能,以便通过根据施加于输入电极13的电信号(输入信号)来一并控制多个栅极控制信号,从而将功率misfet9接通/断开,另一方面,在有源钳位电路26动作时提高功率misfet9的接通电阻(关于详细内容将于后文叙述)。

70.更具体而言,栅极控制电路25包括振荡电路38、电荷泵电路39以及驱动信号输出电路40。振荡电路38根据来自电流电压控制电路23的电信号而振荡,生成预定的电信号。由振荡电路38生成的电信号被输入至电荷泵电路39。电荷泵电路39使来自振荡电路38的电信号升压。由电荷泵电路39升压后的电信号被输入至驱动信号输出电路40。

71.驱动信号输出电路40根据来自电荷泵电路39的电信号以及来自保护电路24(更具体而言,过电流保护电路34)的电信号来生成多种栅极控制信号。多种栅极控制信号经由栅极控制配线17被输入至功率misfet9的栅极以及传感器misfet21的栅极。传感器misfet21以及功率misfet9由栅极控制电路25同时控制。

72.有源钳位电路26保护功率misfet9免受反电动势的影响。有源钳位电路26与漏电极11、功率misfet9的栅极以及传感器misfet21的栅极连接。有源钳位电路26也可以包括多个二极管。

73.有源钳位电路26也可以包括相互依次偏置连接的多个二极管。有源钳位电路26也可以包括相互依次逆偏置连接的多个二极管。有源钳位电路26也可以包括相互偏置连接的多个二极管、以及相互逆偏置连接的多个二极管。

74.多个二极管也可以包括pn接合二极管、或者齐纳二极管、或者pn接合二极管以及齐纳二极管。有源钳位电路26也可以包括相互偏置连接的多个齐纳二极管。有源钳位电路26也可以包括相互逆偏置连接的齐纳二极管以及pn接合二极管。

75.电流检测电路27对流动于功率misfet9以及传感器misfet21的电流进行检测。电流检测电路27与保护电路24、异常检测电路29、功率misfet9的源极以及传感器misfet21的源极连接。电流检测电路27根据由功率misfet9生成的电信号以及由传感器misfet21生成的电信号,来生成电流检测信号。电流检测信号被输入至异常检测电路29。

76.电源逆连接保护电路28在电源逆连接时保护电流电压控制电路23、功率misfet9等免受逆电压的影响。电源逆连接保护电路28与基准电压电极14以及电流电压控制电路23连接。

77.异常检测电路29监视保护电路24的电压。异常检测电路29与电流电压控制电路23、保护电路24以及电流检测电路27连接。在过电流保护电路34、负载开路检测电路35、过热保护电路36以及低电压误动作抑制电路37的任一个产生了异常(电压的变动等)的情况下,异常检测电路29生成与保护电路24的电压相应的异常检测信号,并向外部输出。

78.更具体而言,异常检测电路29包括第一多路复用器电路41以及第二多路复用器电路42。第一多路复用器电路41包括两个输入部、一个输出部以及一个选择控制输入部。在第一多路复用器电路41的输入部分别连接有保护电路24以及电流检测电路27。在第一多路复用器电路41的输出部连接有第二多路复用器电路42。在第一多路复用器电路41的选择控制输入部连接有电流电压控制电路23。

79.第一多路复用器电路41根据来自电流电压控制电路23的电信号、来自保护电路24的电压检测信号以及来自电流检测电路27的电流检测信号,来生成异常检测信号。由第一多路复用器电路41生成的异常检测信号被输入至第二多路复用器电路42。

80.第二多路复用器电路42包括两个输入部以及一个输出部。在第二多路复用器电路42的输入部分别连接有第二多路复用器电路42的输出部以及enable电极15。在第二多路复用器电路42的输出部连接有sense电极16。

81.在enable电极15连接有mcu、在sense电极16连接有电阻器的情况下,从mcu向enable电极15输入接通信号,并从sense电极16导出异常检测信号。异常检测信号由与sense电极16连接的电阻器变换成电信号。基于该电信号来检测半导体装置1的状态异常。

82.图3是用于说明图1所示的半导体装置1的有源钳位动作的电路图。图4是图3所示的电路图的主要的电信号的波形图。

83.在此,使用在功率misfet9连接有感应性负载l的电路例来说明半导体装置1的通常动作以及有源钳位动作。例示利用了螺线管、马达、变压器、继电器等绕组(线圈)的器件作为感应性负载l。感应性负载l也称为l负载。

84.参照图3,功率misfet9的源极与感应性负载l连接。功率misfet9的漏极与漏电极11电连接。功率misfet9的栅极以及漏极与有源钳位电路26连接。在该电路例中,有源钳位电路26包括m个(m为自然数)齐纳二极管dz以及n个(n为自然数)pn接合二极管d。pn接合二

极管d相对于齐纳二极管dz逆偏置连接。

85.参照图3以及图4,若向断开状态的功率misfet9的栅极输入接通信号von,则功率misfet9从断开状态切换为接通状态(通常动作)。接通信号von具有栅极阈值电压vth以上(vth≤von)的电压。功率misfet9维持接通状态仅预定的接通时间ton。

86.若功率misfet9切换为接通状态,则漏极电流id开始从功率misfet9的漏极朝向源极流动。漏极电流id从零增加至预定的值而饱和。感应性负载l因漏极电流id的增加而积蓄感应性能量。

87.若向功率misfet9的栅极输入断开信号voff,则功率misfet9从接通状态切换为断开状态。断开信号voff具有小于栅极阈值电压vth的电压(voff<vth)。断开信号voff也可以是基准电压(例如接地电压)。

88.在功率misfet9从接通状态切换为断开状态的迁移时,感应性负载l的感应性能量作为反电动势施加于功率misfet9。由此,功率misfet9成为有源钳位状态(有源钳位动作)。若功率misfet9成为有源钳位状态,则源极电压vss急剧下降至小于基准电压(接地电压)的负电压。

89.此时,源极电压vss因有源钳位电路26的动作而被限制为从电源电压vb减去限制电压vl以及钳位接通电压vclp的电压以上的电压(vss≥vb-vl-vclp)。

90.换言之,若功率misfet9成为有源钳位状态,则功率misfet9的漏极

·

源极间的漏极电压vds急剧上升至钳位电压vdsscl。钳位电压vdsscl通过功率misfet9以及有源钳位电路26而被限制为加上钳位接通电压vclp以及限制电压vl的电压以下的电压(vds≤vclp+vl)。

91.在该方式中,限制电压vl是有源钳位电路26中的齐纳二极管dz的端子间电压vz以及pn接合二极管的端子间电压vf的总合(vl=m

·

vz+n

·

vf)。

92.钳位接通电压vclp是施加于功率misfet9的栅极

·

源极间的正电压(也就是,栅极电压vgs)。钳位接通电压vclp是栅极阈值电压vth以上(vth≤vclp)。因此,功率misfet9在有源钳位状态下维持接通状态。

93.在钳位电压vdsscl超过最大额定漏极电压vdss的情况(vdss<vdsscl)下,功率misfet9达到破坏。功率misfet9设计为钳位电压vdsscl成为最大额定漏极电压vdss以下(vdsscl≤vdss)。

94.在钳位电压vdsscl为最大额定漏极电压vdss以下的情况(vdsscl≤vdss)下,漏极电流id继续从功率misfet9的漏极朝向源极流动,感应性负载l的感应性能量在功率misfet9中被消耗(吸收)。

95.漏极电流id经由有源钳位时间tav而从功率misfet9断开之前的峰值iav减少为零。由此,栅极电压vgs成为基准电压(例如接地电压),功率misfet9从接通状态切换为断开状态。

96.功率misfet9的有源钳位耐量eac根据有源钳位动作时的功率misfet9的耐量来定义。更具体而言,有源钳位耐量eac根据功率misfet9从接通状态向断开状态迁移时、功率misfet9相对于因感应性负载l的感应性能量而产生的反电动势的耐量来定义。

97.更具体而言,有源钳位耐量eac根据功率misfet9相对于因钳位电压vdsscl而产生的能量的耐量来定义。例如,有源钳位耐量eac使用限制电压vl、钳位接通电压vclp、漏极电

流id以及有源钳位时间tav,由eac=(vl+vclp)

×

id

×

tav的式子来表示。

98.图5是图1所示的区域v的剖面立体图。此外,在本图中,为了便于说明,省略第一主面3的上部构造(源极电极12以及栅极控制配线17、以及层间绝缘层等)。

99.在本图的半导体装置1中,,在该方式中,半导体层2具有包括n

+

型的半导体基板51以及n型的外延层52的层叠构造。由半导体基板51形成半导体层2的第二主面4。由外延层52形成半导体层2的第一主面3。由半导体基板51以及外延层52形成半导体层2的侧面5a~5d。

100.外延层52具有小于半导体基板51的n型杂质浓度的n型杂质浓度。半导体基板51的n型杂质浓度也可以为1

×

10

18

cm

-3

以上且1

×

10

20

cm

-3

以下。外延层52的n型杂质浓度也可以为1

×

10

15

cm

-3

以上且1

×

10

18

cm

-3

以下。

101.外延层52具有小于半导体基板51的厚度tsub的厚度tepi(tepi<tsub)。厚度tsub也可以为50μm以上且450μm以下。厚度tsub也可以为50μm以上且150μm以下、150μm以上且250μm以下、250μm以上且350μm以下、或者350μm以上且450μm以下。

102.通过使厚度tsub降低,能够降低电阻值。厚度tsub通过研磨来调整。该情况下,半导体层2的第二主面4也可以是具有研磨痕的研磨面。

103.外延层52的厚度tepi优选为厚度tsub的1/10以下。厚度tepi也可以为5μm以上且20μm以下。厚度tepi也可以为5μm以上且10μm以下、10μm以上且15μm以下、或者15μm以上且20μm以下。厚度tepi优选为5μm以上且15μm以下。

104.半导体基板51作为漏极区域53形成于半导体层2的第二主面4侧。外延层52作为漂移区域54(漏极漂移区域)形成于半导体层2的第一主面3的表层部。漂移区域54的底部由半导体基板51以及外延层52的边界形成。以下,将外延层52称为漂移区域54。

105.在输出区域6中,在半导体层2的第一主面3的表层部形成有p型的主体区域55。主体区域55是成为功率misfet9的基础的区域。主体区域55的p型杂质浓度也可以为1

×

10

16

cm

-3

以上且1

×

10

18

cm

-3

以下。

106.主体区域55形成于漂移区域54的表层部。主体区域55的底部相对于漂移区域54的底部形成于第一主面3侧的区域。主体区域55的厚度也可以为0.5μm以上且2μm以下。主体区域55的厚度也可以为0.5μm以上且1μm以下、1μm以上且1.5μm以下、或者1.5μm以上且2μm以下。

107.功率misfet9包括第一misfet56(第一晶体管)以及第二misfet57(第二晶体管)。第一misfet56从第二misfet57电分离,独立地被控制。第二misfet57从第一misfet56电分离,独立地被控制。

108.也就是,功率misfet9构成为第一misfet56以及第二misfet57这双方在接通状态下进行驱动(全接通控制)。另外,功率misfet9构成为第一misfet56以接通状态而第二misfet57以断开状态进行驱动(第一半接通控制)。并且,功率misfet9构成为第一misfet56以断开状态而第二misfet57以接通状态进行驱动(第二半接通控制)。

109.在全接通控制的情况下,功率misfet9以所有电流路径开放的状态驱动。因此,半导体层2内的接通电阻相对地下降。另一方面,在第一半接通控制或者第二半接通控制的情况下,功率misfet9以一部分电流路径被切断的状态驱动。因此,半导体层2内的接通电阻相对地增加。

110.具体而言,第一misfet56包括多个第一fet(field effect transistor)构造58。

多个第一fet构造58在俯视下沿第一方向x空出间隔地排列,沿第二方向y分别以带状延伸。多个第一fet构造58在俯视下整体形成为条纹状。

111.在图5中,图示出了第一fet构造58的一端部侧的区域,并省略第一fet构造58的另一端部侧的区域的图示。此外,第一fet构造58的另一端部侧的区域的构造与第一fet构造58的一端部侧的区域的构造大致相同。以下,以第一fet构造58的一端部侧的区域的构造为例进行说明,省略对第一fet构造58的另一端部侧的区域的构造的说明。

112.在该方式中,各第一fet构造58包括第一沟槽栅极构造60。第一沟槽栅极构造60的第一宽度wt1也可以为0.5μm以上且5μm以下。第一宽度wt1是与第一沟槽栅极构造60延伸的方向(第二方向y)正交的方向(第一方向x)的宽度。

113.此外,第一宽度wt1也可以为0.5μm以上且1μm以下、1μm以上且1.5μm以下、1.5μm以上且2μm以下、2μm以上且2.5μm以下、2.5μm以上且3μm以下、3μm以上且3.5μm以下、3.5μm以上且4μm以下、4μm以上且4.5μm以下、或者4.5μm以上且5μm以下。第一宽度wt1优选为0.8μm以上且1.2μm以下。

114.第一沟槽栅极构造60贯通主体区域55并到达漂移区域54。第一沟槽栅极构造60的第一深度dt1也可以为1μm以上且10μm以下。第一深度dt1也可以为1μm以上且2μm以下、2μm以上且4μm以下、4μm以上且6μm以下、6μm以上且8μm以下、或者8μm以上且10μm以下。第一深度dt1优选为2μm以上且6μm以下。

115.第一沟槽栅极构造60包括一方侧的第一侧壁61、另一方侧的第二侧壁62、以及连接第一侧壁61及第二侧壁62的底壁63。以下,有时将第一侧壁61、第二侧壁62以及底壁63总称为“内壁”或者“外壁”。

116.在半导体层2内,第一侧壁61在与第一主面3之间所成的角度(锥形角)的绝对值也可以为超过90

°

且95

°

以下(例如91

°

左右)。在半导体层2内,第二侧壁62在与第一主面3之间所成的角度(锥形角)的绝对值也可以为超过90

°

且95

°

以下(例如91

°

左右)。第一沟槽栅极构造60也可以形成为在剖视下从第一主面3侧朝向底壁63侧而第一宽度wt1变窄的尖细形状(锥形形状)。

117.第一沟槽栅极构造60的底壁63相对于漂移区域54的底部位于第一主面3侧的区域。第一沟槽栅极构造60的底壁63形成为朝向漂移区域54的底部的凸弯曲状(u字状)。

118.第一沟槽栅极构造60的底壁63相对于漂移区域54的底部空出1μm以上且10μm以下的第一间隔it1地位于第一主面3侧的区域。第一间隔it1也可以为1μm以上且2μm以下、2μm以上且4μm以下、4μm以上且6μm以下、6μm以上且8μm以下、或者8μm以上且10μm以下。第一间隔it1优选为1μm以上且5μm以下。

119.在该方式中,第二misfet57包括多个第二fet构造68。多个第二fet构造68在俯视下沿第一方向x空出间隔地排列,沿第二方向y分别以带状延伸。

120.多个第二fet构造68沿与多个第一fet构造58相同的方向延伸。多个第二fet构造68在俯视下整体形成为条纹状。在该方式中,多个第二fet构造68以隔着一个第一fet构造58的形态与多个第一fet构造58交替地排列。

121.在图5中,图示出第二fet构造68的一端部侧的区域,并省略了第二fet构造68的另一端部侧的区域的图示。此外,第二fet构造68的另一端部侧的区域的构造与第二fet构造68的一端部侧的区域的构造大致相同。以下,以第二fet构造68的一端部侧的区域的构造为

例进行说明,并省略第二fet构造68的另一端部侧的区域的构造的说明。

122.在该方式中,各第二fet构造68包括第二沟槽栅极构造70。第二沟槽栅极构造70的第二宽度wt2也可以为0.5μm以上且5μm以下。第二宽度wt2是与第二沟槽栅极构造70延伸的方向(第二方向y)正交的方向(第一方向x)的宽度。

123.此外,第二宽度wt2也可以为0.5μm以上且1μm以下、1μm以上且1.5μm以下、1.5μm以上且2μm以下、2μm以上且2.5μm以下、2.5μm以上且3μm以下、3μm以上且3.5μm以下、3.5μm以上且4μm以下、4μm以上且4.5μm以下、或者4.5μm以上且5μm以下。第二宽度wt2优选为0.8μm以上且1.2μm以下。

124.第二沟槽栅极构造70的第二宽度wt2也可以为第一沟槽栅极构造60的第一宽度wt1以上(wt1≤wt2)。第二宽度wt2也可以为第一宽度wt1以下(wt1≥wt2)。第二宽度wt2优选与第一宽度wt1相等(wt1=wt2)。

125.第二沟槽栅极构造70贯通主体区域55并到达漂移区域54。第二沟槽栅极构造70的第二深度dt2也可以为1μm以上且10μm以下。第二深度dt2也可以为1μm以上且2μm以下、2μm以上且4μm以下、4μm以上且6μm以下、6μm以上且8μm以下、或者8μm以上且10μm以下。第二深度dt2优选为2μm以上且6μm以下。

126.第二沟槽栅极构造70的第二深度dt2也可以为第一沟槽栅极构造60的第一深度dt1以上(dt1≤dt2)。第二深度dt2也可以为第一深度dt1以下(dt1≥dt2)。此外,第二深度dt2优选与第一深度dt1相等(dt1=dt2)。

127.第二沟槽栅极构造70包括一方侧的第一侧壁71、另一方侧的第二侧壁72、以及连接第一侧壁71及第二侧壁72的底壁73。以下,有时将第一侧壁71、第二侧壁72以及底壁73总称为“内壁”或者“外壁”。

128.在半导体层2内,第一侧壁71在与第一主面3之间所成的角度(锥形角)的绝对值也可以为超过90

°

且95

°

以下(例如91

°

左右)。在半导体层2内,第二侧壁72在与第一主面3之间所成的角度(锥形角)的绝对值也可以为超过90

°

且95

°

以下(例如91

°

左右)。第二沟槽栅极构造70也可以形成为,在剖视下从第一主面3侧朝向底壁73侧而第二宽度wt2变窄的尖细形状(锥形形状)。

129.第二沟槽栅极构造70的底壁73相对于漂移区域54的底部位于第一主面3侧的区域。第二沟槽栅极构造70的底壁73形成为朝向漂移区域54的底部的凸弯曲状(u字状)。

130.第二沟槽栅极构造70的底壁73相对于漂移区域54的底部空出1μm以上且10μm以下的第二间隔it2地位于第一主面3侧的区域。第二间隔it2也可以为1μm以上且2μm以下、2μm以上且4μm以下、4μm以上且6μm以下、6μm以上且8μm以下、或者8μm以上且10μm以下。第二间隔it2优选为1μm以上且5μm以下。

131.在多个第一沟槽栅极构造60以及多个第二沟槽栅极构造70之间的区域分别划分出单元区域75。多个单元区域75在俯视下沿第一方向x空出间隔地排列,沿第二方向y分别以带状延伸。多个单元区域75沿与第一沟槽栅极构造60以及第二沟槽栅极构造70相同的方向延伸。多个单元区域75在俯视下整体形成为条纹状。

132.从第一沟槽栅极构造60的外壁向漂移区域54内扩展出第一空乏层。第一空乏层从第一沟槽栅极构造60的外壁朝向沿第一主面3的方向以及法线方向z扩展。同样,从第二沟槽栅极构造70的外壁向漂移区域54内扩展出第二空乏层。第二空乏层从第二沟槽栅极构造

70的外壁朝向沿第一主面3的方向以及法线方向z扩展。

133.第二沟槽栅极构造70以第二空乏层与第一空乏层重叠的形态,从第一沟槽栅极构造60空出间隔地排列。也就是,第二空乏层在单元区域75相对于第二沟槽栅极构造70的底壁73在第一主面3侧的区域与第一空乏层重叠。根据这种构造,能够抑制电场集中于第一沟槽栅极构造60以及第二沟槽栅极构造70,因此能够抑制击穿电压的下降。

134.第二空乏层优选相对于第二沟槽栅极构造70的底壁73在漂移区域54的底部侧的区域与第一空乏层重叠。根据这种构造,能够抑制电场集中于第一沟槽栅极构造60的底壁63以及第二沟槽栅极构造70的底壁73,因此能够适当地抑制击穿电压的下降。

135.第一沟槽栅极构造60以及第二沟槽栅极构造70的侧壁间的间距ps也可以为0.2μm以上且2μm以下。间距ps是在第一沟槽栅极构造60的第一侧壁61(第二侧壁62)以及第二沟槽栅极构造70的第二侧壁72(第一侧壁71)之间、与第一沟槽栅极构造60以及第二沟槽栅极构造70延伸的方向(第二方向y)正交的方向(第一方向x)的距离。

136.间距ps也可以为0.2μm以上且0.4μm以下、0.4μm以上且0.6μm以下、0.6μm以上且0.8μm以下、0.8μm以上且1.0μm以下、1.0μm以上且1.2μm以下、1.2μm以上且1.4μm以下、1.4μm以上且1.6μm以下、1.6μm以上且1.8μm以下、或者1.8μm以上且2.0μm以下。间距ps优选为0.3μm以上且1.5μm以下。

137.第一沟槽栅极构造60以及第二沟槽栅极构造70的中央部间的间距pc也可以为1μm以上且7μm以下。间距pc是在第一沟槽栅极构造60的中央部以及第二沟槽栅极构造70的中央部之间、与第一沟槽栅极构造60以及第二沟槽栅极构造70延伸的方向(第二方向y)正交的方向(第一方向x)的距离。

138.此外,间距pc也可以为1μm以上且2μm以下、2μm以上且3μm以下、3μm以上且4μm以下、4μm以上且5μm以下、5μm以上且6μm以下、或者6μm以上且7μm以下。间距pc优选为1μm以上且3μm以下。

139.更具体而言,第一沟槽栅极构造60包括第一栅极沟槽81、第一绝缘层82以及第一电极83。第一栅极沟槽81通过朝向第二主面4侧挖掘第一主面3而形成。

140.第一栅极沟槽81划分第一沟槽栅极构造60的第一侧壁61、第二侧壁62以及底壁63。以下,将第一沟槽栅极构造60的第一侧壁61、第二侧壁62以及底壁63也称为第一栅极沟槽81的第一侧壁61、第二侧壁62以及底壁63。

141.第一绝缘层82沿第一栅极沟槽81的内壁形成为膜状。第一绝缘层82在第一栅极沟槽81内划分凹状的空间。在第一绝缘层82中包覆第一栅极沟槽81的底壁63的部分沿第一栅极沟槽81的底壁63形成。由此,第一绝缘层82在第一栅极沟槽81内划分以u字状凹陷的u字空间。

142.第一绝缘层82包含氧化硅(sio2)、氮化硅(sin)、氧化铝(al2o3)、氧化锆(zro2)以及氧化钽(ta2o3)中的至少一种。

143.第一绝缘层82也可以具有包括从半导体层2侧依次层叠的sin层以及sio2层的层叠构造。第一绝缘层82也可以具有包括从半导体层2侧依次层叠的sio2层以及sin层的层叠构造。第一绝缘层82也可以具有由sio2层或者sin层构成的单层构造。在该方式中,第一绝缘层82具有由sio2层构成的单层构造。

144.第一绝缘层82包括从第一栅极沟槽81的底壁63侧朝向第一主面3侧依次形成的第

一底侧绝缘层84以及第一开口侧绝缘层85。

145.第一底侧绝缘层84包覆第一栅极沟槽81的底壁63侧的内壁。更具体而言,第一底侧绝缘层84相对于主体区域55的底部包覆第一栅极沟槽81的底壁63侧的内壁。第一底侧绝缘层84在第一栅极沟槽81的底壁63侧划分u字空间。第一底侧绝缘层84具有划分u字空间的平滑的内壁面。第一底侧绝缘层84与漂移区域54相接。第一底侧绝缘层84的一部分也可以与主体区域55相接。

146.第一开口侧绝缘层85包覆第一栅极沟槽81的开口侧的内壁。更具体而言,第一开口侧绝缘层85相对于主体区域55的底部在第一栅极沟槽81的开口侧的区域包覆第一栅极沟槽81的第一侧壁61以及第二侧壁62。第一开口侧绝缘层85与主体区域55相接。第一开口侧绝缘层85的一部分也可以与漂移区域54相接。

147.第一底侧绝缘层84具有第一厚度t1。第一开口侧绝缘层85具有小于第一厚度t1的第二厚度t2(t2<t1)。第一厚度t1是在第一底侧绝缘层84沿第一栅极沟槽81的内壁的法线方向的厚度。第二厚度t2是在第一开口侧绝缘层85沿第一栅极沟槽81的内壁的法线方向的厚度。

148.此外,第一厚度t1相对于第一栅极沟槽81的第一宽度wt1的第一比t1/wt1也可以为0.1以上且0.4以下。另外,第一比t1/wt1也可以为0.1以上且0.15以下、0.15以上且0.2以下、0.2以上且0.25以下、0.25以上且0.3以下、0.3以上且0.35以下、或者0.35以上且0.4以下。第一比t1/wt1优选为0.25以上且0.35以下。

149.此外,第一底侧绝缘层84的第一厚度t1也可以为以上且以下。第一厚度t1也可以为以上且以下、以上且以下、以上且以下、以上且以下、或者以上且以下。第一厚度t1优选为以上且以下。

150.第一厚度t1也可以根据第一栅极沟槽81的第一宽度wt1调整为以上且以下。第一厚度t1也可以为以上且以下、以上且以下、以上且以下、以上且以下、以上且以下、以上且以下、以上且以下、或者以上且以下。该情况下,能够通过第一底侧绝缘层84的厚化来提高半导体装置1的耐压。

151.第一开口侧绝缘层85的第二厚度t2也可以为第一底侧绝缘层84的第一厚度t1的1/100以上且1/10以下。第二厚度t2也可以为以上且以下。第二厚度t2也可以为以上且以下、以上且以下、以上且以下、或者以上且以下。第二厚度t2优选为以上且以下。

152.第一底侧绝缘层84以从包覆第一栅极沟槽81的第一侧壁61以及第二侧壁62的部分朝向包覆第一栅极沟槽81的底壁63的部分而第一厚度t1减少的形态形成。

153.在第一底侧绝缘层84中包覆第一栅极沟槽81的底壁63的部分的厚度比在第一底侧绝缘层84中包覆第一栅极沟槽81的第一侧壁61以及第二侧壁62的部分的厚度小。由第一底侧绝缘层84划分出的u字空间的底壁侧的开口宽度扩张相当于第一厚度t1减少的量。由

此,抑制u字空间的尖细。这种u字空间例如通过对第一底侧绝缘层84的内壁的蚀刻法(例如湿蚀刻法)来形成。

154.第一电极83隔着第一绝缘层82埋入于第一栅极沟槽81。对第一电极83施加包括接通信号von以及断开信号voff的第一栅极控制信号(第一控制信号)。在该方式中,第一电极83具有包括第一底侧电极86、第一开口侧电极87以及第一中间绝缘层88的绝缘分离型的分开电极构造。

155.第一底侧电极86隔着第一绝缘层82埋设于第一栅极沟槽81的底壁63侧。更具体而言,第一底侧电极86隔着第一底侧绝缘层84埋设于第一栅极沟槽81的底壁63侧。第一底侧电极86隔着第一底侧绝缘层84而与漂移区域54对置。第一底侧电极86的一部分也可以隔着第一底侧绝缘层84而与主体区域55对置。

156.第一底侧电极86在第一栅极沟槽81的开口侧且在第一底侧绝缘层84以及第一开口侧绝缘层85之间划分剖面观察时呈倒凹状的凹槽。根据这种构造,能够抑制相对于第一底侧电极86的局部的电场集中,因此能够抑制击穿电压的下降。尤其是,通过在第一底侧绝缘层84的扩张后的u字空间埋设第一底侧电极86,能够适当地抑制第一底侧电极86从上端部朝向下端部成为尖细形状。由此,能够适当地抑制相对于第一底侧电极86的下端部的局部的电场集中。

157.第一底侧电极86也可以包含导电性多晶硅、钨、铝、铜、铝合金以及铜合金中的至少一种。在该方式中,第一底侧电极86包含导电性多晶硅。导电性多晶硅也可以包含n型杂质或者p型杂质。此外,导电性多晶硅优选包含n型杂质。

158.第一开口侧电极87隔着第一绝缘层82埋设于第一栅极沟槽81的开口侧。更具体而言,第一开口侧电极87隔着第一开口侧绝缘层85埋设于在第一栅极沟槽81的开口侧划分出的倒凹状的凹槽。第一开口侧电极87隔着第一开口侧绝缘层85而与主体区域55对置。第一开口侧电极87的一部分也可以隔着第一开口侧绝缘层85而与漂移区域54对置。

159.第一开口侧电极87也可以包含导电性多晶硅、钨、铝、铜、铝合金以及铜合金中的至少一种。第一开口侧电极87优选包含与第一底侧电极86相同种类的导电材料。在该方式中,第一开口侧电极87包含导电性多晶硅。导电性多晶硅也可以包含n型杂质或者p型杂质。导电性多晶硅优选包含n型杂质。

160.第一中间绝缘层88介于第一底侧电极86以及第一开口侧电极87之间,使第一底侧电极86以及第一开口侧电极87电绝缘。更具体而言,第一中间绝缘层88在第一底侧电极86以及第一开口侧电极87之间的区域包覆从第一底侧绝缘层84露出的第一底侧电极86。第一中间绝缘层88包覆第一底侧电极86的上端部(更具体而言为突出部)。第一中间绝缘层88与第一绝缘层82(第一底侧绝缘层84)相连。

161.第一中间绝缘层88具有第三厚度t3。第三厚度t3小于第一底侧绝缘层84的第一厚度t1(t3<t1)。第三厚度t3也可以为第一厚度t1的1/100以上且1/10以下。第三厚度t3也可以为以上且以下。第三厚度t3也可以为以上且以下、以上且以下、以上且以下、或者以上且以下。第三厚度t3优选为以上且以下。

162.第一中间绝缘层88包括氧化硅(sio2)、氮化硅(sin)、氧化铝(al2o3)、氧化锆

(zro2)、氧化钽(ta2o3)中的至少一种。在该方式中,第一中间绝缘层88具有由sio2层构成的单层构造。

163.在该方式中,在第一开口侧电极87中从第一栅极沟槽81露出的露出部相对于第一主面3位于第一栅极沟槽81的底壁63侧。第一开口侧电极87的露出部形成为朝向第一栅极沟槽81的底壁63的弯曲状。

164.第一开口侧电极87的露出部由形成为膜状的第一盖绝缘层包覆。第一盖绝缘层在第一栅极沟槽81内与第一绝缘层82(第一开口侧绝缘层85)相连。第一盖绝缘层也可以包含氧化硅(sio2)。

165.各第一fet构造58还包括p型的第一通道区域91(第一通道)。第一通道区域91在主体区域55形成于隔着第一绝缘层82(第一开口侧绝缘层85)而与第一电极83(第一开口侧电极87)对置的区域。

166.第一通道区域91沿第一沟槽栅极构造60的第一侧壁61或第二侧壁62、或者第一侧壁61以及第二侧壁62形成。在该方式中,第一通道区域91沿第一沟槽栅极构造60的第一侧壁61以及第二侧壁62形成。

167.各第一fet构造58还包括形成于主体区域55的表层部的n

+

型的第一源极区域92。第一源极区域92在主体区域55内在与漂移区域54之间划定第一通道区域91。第一源极区域92的n型杂质浓度超过漂移区域54的n型杂质浓度。第一源极区域92的n型杂质浓度也可以为1

×

10

19

cm

-3

以上且1

×

10

21

cm

-3

以下。

168.在该方式中,各第一fet构造58包括多个第一源极区域92。多个第一源极区域92在主体区域55的表层部沿第一沟槽栅极构造60空出间隔地形成。更具体而言,多个第一源极区域92沿第一沟槽栅极构造60的第一侧壁61或第二侧壁62、或者第一侧壁61以及第二侧壁62形成。在该方式中,多个第一源极区域92沿第一沟槽栅极构造60的第一侧壁61以及第二侧壁62空出间隔地形成。

169.多个第一源极区域92的底部相对于主体区域55的底部位于第一主面3侧的区域。由此,多个第一源极区域92隔着第一绝缘层82(第一开口侧绝缘层85)而与第一电极83(第一开口侧电极87)对置。这样,第一misfet56的第一通道区域91在主体区域55形成于多个第一源极区域92以及漂移区域54所夹的区域。

170.各第一fet构造58还包括形成于主体区域55的表层部的p

+

型的第一接触区域93。第一接触区域93的p型杂质浓度超过主体区域55的p型杂质浓度。第一接触区域93的p型杂质浓度例如也可以为1

×

10

19

cm

-3

以上且1

×

10

21

cm

-3

以下。

171.在该方式中,各第一fet构造58包括多个第一接触区域93。多个第一接触区域93在主体区域55的表层部沿第一沟槽栅极构造60空出间隔地形成。更具体而言,多个第一接触区域93沿第一沟槽栅极构造60的第一侧壁61或第二侧壁62、或者第一侧壁61以及第二侧壁62形成。

172.在该方式中,多个第一接触区域93沿第一沟槽栅极构造60的第一侧壁61以及第二侧壁62空出间隔地形成。更具体而言,多个第一接触区域93相对于多个第一源极区域92以成为交替的排列的形态形成于主体区域55的表层部。多个第一接触区域93的底部相对于主体区域55的底部位于第一主面3侧的区域。

173.第二沟槽栅极构造70包括第二栅极沟槽101、第二绝缘层102以及第二电极103。第

二栅极沟槽101通过朝向第二主面4侧挖掘第一主面3而形成。

174.第二栅极沟槽101划分第二沟槽栅极构造70的第一侧壁71、第二侧壁72以及底壁73。以下,将第二沟槽栅极构造70的第一侧壁71、第二侧壁72以及底壁73也称为第二栅极沟槽101的第一侧壁71、第二侧壁72以及底壁73。

175.第二绝缘层102沿第二栅极沟槽101的内壁形成为膜状。第二绝缘层102在第二栅极沟槽101内划分凹状的空间。在第二绝缘层102包覆第二栅极沟槽101的底壁73的部分沿着第二栅极沟槽101的底壁73形成。由此,第二绝缘层102在第二栅极沟槽101内划分以u字状凹陷的u字空间。

176.第二绝缘层102包含氧化硅(sio2)、氮化硅(sin)、氧化铝(al2o3)、氧化锆(zro2)以及氧化钽(ta2o3)中的至少一种。

177.第二绝缘层102也可以具有包括从半导体层2侧依次层叠的sin层以及sio2层的层叠构造。第二绝缘层102也可以具有包括从半导体层2侧依次层叠的sio2层以及sin层的层叠构造。第二绝缘层102也可以具有由sio2层或者sin层构成的单层构造。在该方式中,第二绝缘层102具有由sio2层构成的单层构造。

178.第二绝缘层102包括从第二栅极沟槽101的底壁73侧朝向第一主面3侧依次形成的第二底侧绝缘层104以及第二开口侧绝缘层105。

179.第二底侧绝缘层104包覆第二栅极沟槽101的底壁73侧的内壁。更具体而言,第二底侧绝缘层104相对于主体区域55的底部包覆第二栅极沟槽101的底壁73侧的内壁。第二底侧绝缘层104在第二栅极沟槽101的底壁73侧划分u字空间。第二底侧绝缘层104具有划分u字空间的平滑的内壁面。第二底侧绝缘层104与漂移区域54相接。第二底侧绝缘层104的一部分也可以与主体区域55相接。

180.第二开口侧绝缘层105包覆第二栅极沟槽101的开口侧的内壁。更具体而言,第二开口侧绝缘层105相对于主体区域55的底部在第二栅极沟槽101的开口侧的区域包覆第二栅极沟槽101的第一侧壁71以及第二侧壁72。第二开口侧绝缘层105与主体区域55相接。第二开口侧绝缘层105的一部分也可以与漂移区域54相接。

181.第二底侧绝缘层104具有第四厚度t4。第二开口侧绝缘层105具有小于第四厚度t4的第五厚度t5(t5<t4)。第四厚度t4是在第二底侧绝缘层104中沿第二栅极沟槽101的内壁的法线方向的厚度。第五厚度t5是在第二开口侧绝缘层105中沿第二栅极沟槽101的内壁的法线方向的厚度。

182.第四厚度t4相对于第二栅极沟槽101的第二宽度wt2的第二比t4/wt2也可以为0.1以上且0.4以下。例如,第二比t4/wt2也可以为0.1以上且0.15以下、0.15以上且0.2以下、0.2以上且0.25以下、0.25以上且0.3以下、0.3以上且0.35以下、或者0.35以上且0.4以下。第二比t4/wt2优选为0.25以上且0.35以下。

183.第二比t4/wt2也可以为第一比t1/wt1以下(t4/wt2≤t1/wt1)。第二比t4/wt2也可以为第一比t1/wt1以上(t4/wt2≥t1/wt1)。另外,第二比t4/wt2也可以与第一比t1/wt1相等(t4/wt2=t1/wt1)。

184.第二底侧绝缘层104的第四厚度t4也可以为以上且以下。第四厚度t4也可以为以上且以下、以上且以下、以上且

以下、以上且以下、或者以上且以下。第四厚度t4优选为以上且以下。

185.第四厚度t4根据第二栅极沟槽101的第二宽度wt2而为以上且以下。第四厚度t4也可以为以上且以下、以上且以下、以上且以下、以上且以下、以上且以下、以上且以下、以上且以下、或者以上且以下。该情况下,能够通过第二底侧绝缘层104的厚化来提高半导体装置1的耐压。

186.第四厚度t4也可以为第一厚度t1以下(t4≤t1)。第四厚度t4也可以为第一厚度t1以上(t4≥t1)。第四厚度t4也可以与第一厚度t1相等(t4=t1)。

187.第二开口侧绝缘层105的第五厚度t5也可以小于第二底侧绝缘层104的第四厚度t4(t5<t4)。第五厚度t5也可以为第四厚度t4的1/100以上且1/10以下。也可以为以上且以下。第五厚度t5也可以为以上且以下、以上且以下、以上且以下、或者以上且以下。第五厚度t5优选为以上且以下。

188.第五厚度t5也可以为第二厚度t2以下(t5≤t2)。第五厚度t5也可以为第二厚度t2以上(t5≥t2)。第五厚度t5也可以与第二厚度t2相等(t5=t2)。

189.第二底侧绝缘层104以从包覆第二栅极沟槽101的第一侧壁71以及第二侧壁72的部分朝向包覆第二栅极沟槽101的底壁73的部分而第四厚度t4减少的形态形成。

190.在第二底侧绝缘层104中包覆第二栅极沟槽101的底壁73的部分的厚度比在第二底侧绝缘层104中包覆第二栅极沟槽101的第一侧壁71以及第二侧壁72的部分的厚度小。由第二底侧绝缘层104划分出的u字空间的底壁侧的开口宽度扩张相当于第四厚度t4的减少量。由此,抑制u字空间的尖细。这种u字空间例如通过对第二底侧绝缘层104的内壁的蚀刻法(例如湿蚀刻法)而形成。

191.第二电极103隔着第二绝缘层102埋入于第二栅极沟槽101。对第二电极103施加包括接通信号von以及断开信号voff的预定的第二栅极控制信号(第二控制信号)。

192.在该方式中,第二电极103具有包括第二底侧电极106、第二开口侧电极107以及第二中间绝缘层108的绝缘分离型的分开电极构造。在该方式中,第二底侧电极106与第一底侧电极86电连接。第二开口侧电极107与第一开口侧电极87电绝缘。

193.第二底侧电极106隔着第二绝缘层102埋设于第二栅极沟槽101的底壁73侧。更具体而言,第二底侧电极106隔着第二底侧绝缘层104埋设于第二栅极沟槽101的底壁73侧。第二底侧电极106隔着第二底侧绝缘层104而与漂移区域54对置。第二底侧电极106的一部分也可以隔着第二底侧绝缘层104而与主体区域55对置。

194.第二底侧电极106在第二栅极沟槽101的开口侧且在第二底侧绝缘层104以及第二开口侧绝缘层105之间划分剖面观察时呈倒凹状的凹槽。根据这种构造,能够抑制相对于第二底侧电极106的局部的电场集中,因此能够抑制击穿电压的下降。尤其是,通过在第二底侧绝缘层104的扩张后的u字空间埋设第二底侧电极106,能够适当地抑制第二底侧电极106

从上端部朝向下端部成为尖细形状。由此,能够适当地抑制相对于第二底侧电极106的下端部的局部的电场集中。

195.第二底侧电极106也可以包含导电性多晶硅、钨、铝、铜、铝合金以及铜合金中的至少一种。在该方式中,第二底侧电极106也可以包含导电性多晶硅。导电性多晶硅也可以包含n型杂质或者p型杂质。导电性多晶硅优选包含n型杂质。

196.第二开口侧电极107隔着第二绝缘层102埋设于第二栅极沟槽101的开口侧。更具体而言,第二开口侧电极107隔着第二开口侧绝缘层105埋设于在第二栅极沟槽101的开口侧划分出的倒凹状的凹槽。第二开口侧电极107隔着第二开口侧绝缘层105而与主体区域55对置。第二开口侧电极107的一部分也可以隔着第二开口侧绝缘层105而与漂移区域54对置。

197.第二开口侧电极107也可以包含导电性多晶硅、钨、铝、铜、铝合金以及铜合金中的至少一种。第二开口侧电极107优选包含与第二底侧电极106相同种类的导电材料。在该方式中,第二开口侧电极107包含导电性多晶硅。导电性多晶硅也可以包含n型杂质或者p型杂质。导电性多晶硅优选包括n型杂质。

198.第二中间绝缘层108介于第二底侧电极106以及第二开口侧电极107之间,使第二底侧电极106以及第二开口侧电极107电绝缘。更具体而言,第二中间绝缘层108在第二底侧电极106以及第二开口侧电极107之间的区域包覆从第二底侧绝缘层104露出的第二底侧电极106。第二中间绝缘层108包覆第二底侧电极106的上端部(更具体而言为突出部)。第二中间绝缘层108与第二绝缘层102(第二底侧绝缘层104)相连。

199.第二中间绝缘层108具有第六厚度t6。第六厚度t6小于第二底侧绝缘层104的第四厚度t4(t6<t4)。第六厚度t6也可以为第四厚度t4的1/100以上且1/10以下。第六厚度t6也可以为以上且以下。第六厚度t6也可以为以上且以下、以上且以下、以上且以下、或者以上且以下。第六厚度t6优选为以上且以下。

200.第六厚度t6也可以为第三厚度t3以下(t6≤t3)。第六厚度t6也可以为第三厚度t3以上(t6≥t3)。第六厚度t6也可以与第三厚度t3相等(t6=t3)。

201.第二中间绝缘层108包含氧化硅(sio2)、氮化硅(sin)、氧化铝(al2o3)、氧化锆(zro2)以及氧化钽(ta2o3)中的至少一种。此外,在该方式中,第二中间绝缘层108具有由sio2层构成的单层构造。

202.在该方式中,在第二开口侧电极107中从第二栅极沟槽101露出的露出部相对于第一主面3位于第二栅极沟槽101的底壁73侧。第二开口侧电极107的露出部形成为朝向第二栅极沟槽101的底壁73的弯曲状。

203.第二开口侧电极107的露出部由形成为膜状的第二盖绝缘层包覆。第二盖绝缘层在第二栅极沟槽101内与第二绝缘层102(第二开口侧绝缘层105)相连。第二盖绝缘层也可以包含氧化硅(sio2)。

204.各第二fet构造68还具有p型的第二通道区域111(第二通道)。更具体而言,第二通道区域111在主体区域55形成于隔着第二绝缘层102(第二开口侧绝缘层105)而与第二电极103(第二开口侧电极107)对置的区域。

205.更具体而言,第二通道区域111沿第二沟槽栅极构造70的第一侧壁71或第二侧壁72、或者第一侧壁71以及第二侧壁72形成。在该方式中,第二通道区域111沿第二沟槽栅极构造70的第一侧壁71以及第二侧壁72形成。

206.各第二fet构造68还包括形成于主体区域55的表层部的n

+

型的第二源极区域112。第二源极区域112在主体区域55内且在与漂移区域54之间划定第二通道区域111。

207.第二源极区域112的n型杂质浓度超过漂移区域54的n型杂质浓度。第二源极区域112的n型杂质浓度也可以为1

×

10

19

cm

-3

以上且1

×

10

21

cm

-3

以下。第二源极区域112的n型杂质浓度优选与第一源极区域92的n型杂质浓度相等。

208.在该方式中,各第二fet构造68包括多个第二源极区域112。多个第二源极区域112在主体区域55的表层部沿第二沟槽栅极构造70空出间隔地形成。具体而言,多个第二源极区域112沿第二沟槽栅极构造70的第一侧壁71或第二侧壁72、或者第一侧壁71以及第二侧壁72形成。在该方式中,多个第二源极区域112沿第二沟槽栅极构造70的第一侧壁71以及第二侧壁72空出间隔地形成。

209.在该方式中,各第二源极区域112沿第一方向x与各第一源极区域92对置。各第二源极区域112与各第一源极区域92形成为一体。在图5中,利用边界线区别示出第一源极区域92以及第二源极区域112,但实际上在第一源极区域92以及第二源极区域112之间的区域没有明确的边界线。

210.各第二源极区域112也可以以沿第一方向x与各第一源极区域92的一部分或者全部对置的方式,从各第一源极区域92沿第二方向y偏移地形成。也就是,多个第一源极区域92以及多个第二源极区域112也可以在俯视下以交错状排列。

211.多个第二源极区域112的底部相对于主体区域55的底部位于第一主面3侧的区域。由此,多个第二源极区域112隔着第二绝缘层102(第二开口侧绝缘层105)而与第二电极103(第二开口侧电极107)对置。这样,第二misfet57的第二通道区域111在主体区域55形成于多个第二源极区域112以及漂移区域54所夹的区域。

212.各第二fet构造68还包括形成于主体区域55的表层部的p

+

型的第二接触区域113。第二接触区域113的p型杂质浓度超过主体区域55的p型杂质浓度。第二接触区域113的p型杂质浓度也可以为1

×

10

19

cm

-3

以上且1

×

10

21

cm

-3

以下。第二接触区域113的p型杂质浓度优选与第一接触区域93的p型杂质浓度相等。

213.在该方式中,各第二fet构造68包括多个第二接触区域113。多个第二接触区域113在主体区域55的表层部沿第二沟槽栅极构造70空出间隔地形成。更具体而言,多个第二接触区域113沿第二沟槽栅极构造70的第一侧壁71或第二侧壁72、或者第一侧壁71以及第二侧壁72形成。多个第二接触区域113的底部相对于主体区域55的底部位于第一主面3侧的区域。

214.在该方式中,多个第二接触区域113沿第二沟槽栅极构造70的第一侧壁71以及第二侧壁72空出间隔地形成。更具体而言,多个第二接触区域113以相对于多个第二源极区域112成为交替的排列的形态形成于主体区域55的表层部。

215.参照图5,在该方式中,各第二接触区域113沿第一方向x而与各第一接触区域93对置。各第二接触区域113与各第一接触区域93形成为一体。

216.在图5中,为了与第一源极区域92以及第二源极区域112区别,将第一接触区域93

以及第二接触区域113统一用“p

+”的记号来表示。

217.各第二接触区域113也可以以沿第一方向x与各第一接触区域93的一部分或者全部对置的方式,从各第一接触区域93沿第二方向y偏移地形成。也就是,多个第一接触区域93以及多个第二接触区域113也可以在俯视下以交错状排列。

218.参照图5,在该方式中,主体区域55在半导体层2的第一主面3中从第一沟槽栅极构造60的一端部以及第二沟槽栅极构造70的一端部之间的区域露出。第一源极区域92、第一接触区域93、第二源极区域112以及第二接触区域113也可以在第一主面3中形成于第一沟槽栅极构造60的一端部以及第二沟槽栅极构造70的一端部所夹的区域。

219.同样,虽然未图示,但在该方式中,主体区域55在半导体层2的第一主面3中从第一沟槽栅极构造60的另一端部以及第二沟槽栅极构造70的另一端部之间的区域露出。第一源极区域92、第一接触区域93、第二源极区域112以及第二接触区域113也可以形成于第一沟槽栅极构造60的另一端部以及第二沟槽栅极构造70的另一端部所夹的区域。

220.参照图5,在半导体层2的第一主面3形成有多个(在此为两个)沟槽接触构造120。多个沟槽接触构造120包括一方侧的沟槽接触构造120以及另一方侧的沟槽接触构造120。

221.一方侧的沟槽接触构造120位于第一沟槽栅极构造60的一端部以及第二沟槽栅极构造70的一端部侧的区域。另一方侧的沟槽接触构造120位于第一沟槽栅极构造60的另一端部以及第二沟槽栅极构造70的另一端部侧的区域。

222.另一方侧的沟槽接触构造120具有与一方侧的沟槽接触构造120大致相同的构造。以下,以一方侧的沟槽接触构造120侧的构造为例进行说明,省略对另一方侧的沟槽接触构造120侧的构造的具体的说明。

223.沟槽接触构造120与第一沟槽栅极构造60的一端部以及第二沟槽栅极构造70的一端部连接。在该方式中,沟槽接触构造120在俯视下沿第一方向x以带状延伸。

224.沟槽接触构造120的宽度wtc也可以为0.5μm以上且5μm以下。宽度wtc是与沟槽接触构造120延伸的方向(第一方向x)正交的方向(第二方向y)的宽度。

225.宽度wtc也可以为0.5μm以上且1μm以下、1μm以上且1.5μm以下、1.5μm以上且2μm以下、2μm以上且2.5μm以下、2.5μm以上且3μm以下、3μm以上且3.5μm以下、3.5μm以上且4μm以下、4μm以上且4.5μm以下、或者4.5μm以上且5μm以下。宽度wtc优选为0.8μm以上且1.2μm以下。

226.宽度wtc优选与第一沟槽栅极构造60的第一宽度wt1相等(wtc=wt1)。宽度wtc优选与第二沟槽栅极构造70的第二宽度wt2相等(wtc=wt2)。

227.沟槽接触构造120贯通主体区域55并到达漂移区域54。沟槽接触构造120的深度dtc也可以为1μm以上且10μm以下。深度dtc也可以为1μm以上且2μm以下、2μm以上且4μm以下、4μm以上且6μm以下、6μm以上且8μm以下、或者8μm以上且10μm以下。深度dtc优选为2μm以上且6μm以下。

228.深度dtc优选与第一沟槽栅极构造60的第一深度dt1相等(dtc=dt1)。深度dtc优选与第二沟槽栅极构造70的第二深度dt2相等(dtc=dt2)。

229.沟槽接触构造120包括一方侧的第一侧壁121、另一方侧的第二侧壁122、、连接第一侧壁121及第二侧壁122的底壁123。以下,有时将第一侧壁121、第二侧壁122以及底壁123总称为“内壁”。第一侧壁121是与第一沟槽栅极构造60以及第二沟槽栅极构造70连接的连

接面。

230.第一侧壁121、第二侧壁122以及底壁123位于漂移区域54内。第一侧壁121以及第二侧壁122沿法线方向z延伸。第一侧壁121以及第二侧壁122也可以与第一主面3垂直地形成。

231.在半导体层2内,第一侧壁121在与第一主面3之间所成的角度(锥形角)的绝对值也可以为超过90

°

且95

°

以下(例如91

°

左右)。在半导体层2内,第二侧壁122在与第一主面3之间所成的角度(锥形角)的绝对值也可以为超过90

°

且95

°

以下(例如91

°

左右)。沟槽接触构造120也可以形成为在剖视下从半导体层2的第一主面3侧朝向底壁123侧而宽度wtc变窄的尖细形状(锥形形状)。

232.底壁123相对于漂移区域54的底部位于第一主面3侧的区域。底壁123形成为朝向漂移区域54的底部的凸弯曲状。底壁123相对于漂移区域54的底部空出1μm以上且10μm以下的间隔itc地位于第一主面3侧的区域。间隔itc也可以为1μm以上且2μm以下、2μm以上且4μm以下、4μm以上且6μm以下、6μm以上且8μm以下、或者8μm以上且10μm以下。间隔itc优选为1μm以上且5μm以下。

233.间隔itc优选与第一沟槽栅极构造60的第一间隔it1相等(itc=it1)。间隔itc优选与第二沟槽栅极构造70的第二间隔it2相等(itc=it2)。

234.沟槽接触构造120包括接触沟槽131、接触绝缘层132以及接触电极133。接触沟槽131通过朝向第二主面4侧挖掘半导体层2的第一主面3而形成。

235.接触沟槽131划分沟槽接触构造120的第一侧壁121、第二侧壁122以及底壁123。以下,将沟槽接触构造120的第一侧壁121、第二侧壁122以及底壁123也称为接触沟槽131的第一侧壁121、第二侧壁122以及底壁123。

236.接触沟槽131的第一侧壁121与第一栅极沟槽81的第一侧壁61以及第二侧壁62连通。接触沟槽131的第一侧壁121与第二栅极沟槽101的第一侧壁71以及第二侧壁72连通。接触沟槽131在第一栅极沟槽81以及第二栅极沟槽101之间形成一个沟槽。

237.接触绝缘层132沿接触沟槽131的内壁形成为膜状。接触绝缘层132在接触沟槽131内划分凹状的空间。在接触绝缘层132中包覆接触沟槽131的底壁123的部分沿着接触沟槽131的底壁123形成。

238.接触绝缘层132以与第一底侧绝缘层84(第二底侧绝缘层104)相同的形态在接触沟槽131内划分以u字状凹陷的u字空间。也就是,接触绝缘层132划分接触沟槽131的底壁123侧的区域扩张且尖细被抑制的u字空间。这种u字空间例如通过对接触绝缘层132的内壁的蚀刻法(例如湿蚀刻法)来形成。

239.接触绝缘层132具有第七厚度t7。第七厚度t7也可以为以上且以下。第七厚度t7也可以为以上且以下、以上且以下、以上且以下、以上且以下、或者以上且以下。第七厚度t7优选为以上且以下。

240.第七厚度t7也可以根据沟槽接触构造120的宽度wtc而为以上且以下。第七厚度t7也可以为以上且以下、以上且以下、

以上且以下、以上且以下、以上且以下、以上且以下、以上且以下、或者以上且以下。该情况下,能够通过接触绝缘层132的厚化来提高半导体装置1的耐压。

241.第七厚度t7优选与第一底侧绝缘层84的第一厚度t1相等(t7=t1)。第七厚度t7优选与第二底侧绝缘层104的第四厚度t4相等(t7=t4)。

242.接触绝缘层132包含氧化硅(sio2)、氮化硅(sin)、氧化铝(al2o3)、氧化锆(zro2)以及氧化钽(ta2o3)中的至少一种。

243.接触绝缘层132也可以具有包括从半导体层2侧依次层叠的sin层以及sio2层的层叠构造。接触绝缘层132也可以具有包括从半导体层2侧依次层叠的sio2层以及sin层的层叠构造。接触绝缘层132也可以具有由sio2层或者sin层构成的单层构造。在该方式中,接触绝缘层132具有由sio2层构成的单层构造。接触绝缘层132优选由与第一绝缘层82(第二绝缘层102)相同的绝缘材料构成。

244.接触绝缘层132在第一栅极沟槽81以及接触沟槽131之间的连通部中与第一绝缘层82形成为一体。接触绝缘层132在第二栅极沟槽101以及接触沟槽131之间的连通部中与第二绝缘层102形成为一体。

245.在该方式中,接触绝缘层132具有向第一栅极沟槽81的一端部以及第二栅极沟槽101的一端部引出的引出绝缘层132a。引出绝缘层132a横穿连通部并包覆第一栅极沟槽81的一端部的内壁。引出绝缘层132a横穿连通部并包覆第二栅极沟槽101的一端部的内壁。

246.引出绝缘层132a在第一栅极沟槽81内与第一底侧绝缘层84以及第一开口侧绝缘层85形成为一体。引出绝缘层132a在第一栅极沟槽81的一端部的内壁中与第一底侧绝缘层84一起划分u字空间。

247.引出绝缘层132a在第二栅极沟槽101内与第二底侧绝缘层104以及第二开口侧绝缘层105形成为一体。引出绝缘层132a在第二栅极沟槽101的一端部的内壁中与第二底侧绝缘层104一起划分u字空间。

248.接触电极133隔着接触绝缘层132埋入于接触沟槽131。接触电极133与第一电极83以及第二电极103不同,作为一体物埋入于接触沟槽131。接触电极133具有从接触沟槽131露出的上端部、与接触绝缘层132相接的下端部。

249.接触电极133的下端部以与第一底侧电极86(第二底侧电极106)相同的形态,形成为朝向接触沟槽131的底壁123的凸弯曲状。更具体而言,接触电极133的下端部沿着由接触绝缘层132划分出的u字空间的底壁形成,并形成为朝向底壁123的平滑的凸弯曲状。

250.根据这种构造,能够抑制相对于接触电极133的局部的电场集中,因此能够抑制击穿电压的下降。尤其是,通过在接触绝缘层132扩张后的u字空间埋设接触电极133,能够适当地抑制接触电极133从上端部朝向下端部成为尖细形状。由此,能够适当地抑制相对于接触绝缘层132的下端部的局部的电场集中。

251.接触电极133在第一栅极沟槽81以及接触沟槽131之间的连接部中与第一底侧电极86电连接。接触电极133在第二栅极沟槽101以及接触沟槽131之间的连接部中与第二底侧电极106电连接。由此,第二底侧电极106与第一底侧电极86电连接。

252.更具体而言,接触电极133具有向第一栅极沟槽81的一端部以及第二栅极沟槽101

的一端部引出的引出电极133a。引出电极133a横穿第一栅极沟槽81以及接触沟槽131之间的连通部并位于第一栅极沟槽81内。引出电极133a还横穿第二栅极沟槽101以及接触沟槽131之间的连通部并位于第二栅极沟槽101内。

253.引出电极133a在第一栅极沟槽81内埋入于由接触绝缘层132划分出的u字空间。引出电极133a在第一栅极沟槽81内与第一底侧电极86形成为一体。由此,接触电极133与第一底侧电极86电连接。

254.在第一栅极沟槽81内,第一中间绝缘层88介于接触电极133以及第一开口侧电极87之间。由此,接触电极133在第一栅极沟槽81内与第一开口侧电极87电绝缘。

255.引出电极133a在第二栅极沟槽101内埋入于由接触绝缘层132划分出的u字空间。引出电极133a在第二栅极沟槽101内与第二底侧电极106形成为一体。由此,接触电极133与第二底侧电极106电连接。

256.在第二栅极沟槽101内,第二中间绝缘层108介于接触电极133与第二开口侧电极107之间。由此,接触电极133在第二栅极沟槽101内与第二开口侧电极107电绝缘。

257.接触电极133也可以包含导电性多晶硅、钨、铝、铜、铝合金以及铜合金中的至少一种。在该方式中,接触电极133包含导电性多晶硅。导电性多晶硅也可以包含n型杂质或者p型杂质。导电性多晶硅优选包含n型杂质。接触电极133优选包含与第一底侧电极86以及第二底侧电极106相同的导电材料。

258.在该方式中,在接触电极133从接触沟槽131露出的露出部相对于第一主面3位于接触沟槽131的底壁123侧。接触电极133的露出部形成为朝向接触沟槽131的底壁123的弯曲状。

259.接触电极133的露出部由形成为膜状的第三盖绝缘层139包覆。第三盖绝缘层139在接触沟槽131内与接触绝缘层132相连。第三盖绝缘层139也可以包含氧化硅(sio2)。

260.此外,从控制器ic10向第一栅极控制配线17a(未图示)输入的栅极控制信号传递至第一开口侧电极87。另外,从控制器ic10向第二栅极控制配线17b(未图示)输入的栅极控制信号传递至第二开口侧电极107。另外,从控制器ic10向第三栅极控制配线17c(未图示)输入的栅极控制信号经由接触电极133传递至第一底侧电极86以及第二底侧电极106。

261.在第一misfet56(第一沟槽栅极构造60)以及第二misfet57(第二沟槽栅极构造70)均被控制为断开状态的情况下,第一通道区域91以及第二通道区域111均被控制为断开状态。

262.在第一misfet56以及第二misfet57均被控制为接通状态的情况下,第一通道区域91以及第二通道区域111均被控制为接通状态(全接通控制)。

263.在第一misfet56被控制为接通状态而第二misfet57被控制为断开状态的情况下,第一通道区域91被控制为接通状态,第二通道区域111被控制为断开状态(第一半接通控制)。

264.在第一misfet56被控制为断开状态而第二misfet57被控制为接通状态的情况下,第一通道区域91被控制为断开状态,第二通道区域111被控制为接通状态(第二半接通控制)。

265.这样,功率misfet9利用形成于一个输出区域6的第一misfet56以及第二misfet57,实现包括全接通控制、第一半接通控制以及第二半接通控制的多种控制。

266.在使第一misfet56驱动时(也就是,栅极的接通控制时),也可以对第一底侧电极86施加接通信号von、对第一开口侧电极87施加接通信号von。该情况下,第一底侧电极86以及第一开口侧电极87作为栅极电极发挥功能。

267.由此,能够抑制第一底侧电极86以及第一开口侧电极87之间的电压下降,因此能够抑制第一底侧电极86以及第一开口侧电极87之间的电场集中。另外,能够使半导体层2的接通电阻下降,因此能够实现消耗电力的降低。

268.在使第一misfet56驱动时(也就是,栅极的接通控制时),也可以对第一底侧电极86施加断开信号voff(例如基准电压)、对第一开口侧电极87施加接通信号von。该情况下,第一底侧电极86作为场电极发挥功能、而第一开口侧电极87作为栅极电极发挥功能。由此,能够使寄生容量下降,从而能够实现开关速度的提高。

269.在使第二misfet57驱动时(也就是,栅极的接通控制时),也可以对第二底侧电极106施加接通信号von、对第二开口侧电极107施加接通信号von。该情况下,第二底侧电极106以及第二开口侧电极107作为栅极电极发挥功能。

270.由此,能够抑制第二底侧电极106以及第二开口侧电极107之间的电压下降,因此能够抑制第二底侧电极106以及第二开口侧电极107之间的电场集中。另外,能够使半导体层2的接通电阻下降,因此能够实现消耗电力的降低。

271.在使第二misfet57驱动时(也就是,栅极的接通控制时),也可以对第二底侧电极106施加断开信号voff(基准电压)、对第二开口侧电极107施加接通信号von。该情况下,第二底侧电极106作为场电极发挥功能、而第二开口侧电极107作为栅极电极发挥功能。由此,能够使寄生容量下降,从而能够实现开关速度的提高。

272.参照图5,第一通道区域91在各单元区域75中以第一通道面积s1形成。第一通道面积s1由形成于各单元区域75的多个第一源极区域92的总计平面面积来定义。

273.第一通道区域91在各单元区域75中以第一通道比例r1(第一比例)形成。第一通道比例r1是,当将各单元区域75的平面面积设为100%时,第一通道面积s1在各单元区域75所占的比例。

274.第一通道比例r1在0%以上且50%以下的范围内调整。第一通道比例r1也可以为0%以上且5%以下、5%以上且10%以下、10%以上且15%以下、15%以上且20%以下、20%以上且25%以下、25%以上且30%以下、30%以上且35%以下、35%以上且40%以下、40%以上且45%以下、或者45%以上且50%以下。第一通道比例r1优选为10%以上且35%以下。

275.在第一通道比例r1为50%的情况下,在第一沟槽栅极构造60的第一侧壁61以及第二侧壁62的大致整个区域形成第一源极区域92。该情况下,不在第一沟槽栅极构造60的第一侧壁61以及第二侧壁62形成第一接触区域93。第一通道比例r1优选为小于50%。

276.在第一通道比例r1为0%的情况下,不在第一沟槽栅极构造60的第一侧壁61以及第二侧壁62形成第一源极区域92。该情况下,在第一沟槽栅极构造60的第一侧壁61以及第二侧壁62仅形成主体区域55以及/或者第一接触区域93。第一通道比例r1优选为超过0%。在该方式中,示出了第一通道比例r1为25%的例子。

277.第二通道区域111在各单元区域75以第二通道面积s2形成。第二通道面积s2由形成于各单元区域75的多个第二源极区域112的总计平面面积来定义。

278.第二通道区域111在各单元区域75中以第二通道比例r2(第二比例)形成。第二通

道比例r2是,当将各单元区域75的平面面积设为100%时,第二通道面积s2在各单元区域75所占的比例。

279.第二通道比例r2在0%以上且50%以下的范围内调整。第二通道比例r2也可以为0%以上且5%以下、5%以上且10%以下、10%以上且15%以下、15%以上且20%以下、20%以上且25%以下、25%以上且30%以下、30%以上且35%以下、35%以上且40%以下、40%以上且45%以下、或者45%以上且50%以下。第二通道比例r2优选为10%以上且35%以下。

280.在第二通道比例r2为50%的情况下,在第二沟槽栅极构造70的第一侧壁71以及第二侧壁72的大致整个区域形成第二源极区域112。该情况下,不在第二沟槽栅极构造70的第一侧壁71以及第二侧壁72形成第二接触区域113。第二通道比例r2优选为小于50%。

281.在第二通道比例r2为0%的情况下,不在第二沟槽栅极构造70的第一侧壁71以及第二侧壁72形成第二源极区域112。该情况下,在第二沟槽栅极构造70的第一侧壁71以及第二侧壁72仅形成主体区域55以及/或者第二接触区域113。第二通道比例r2优选为超过0%。在该方式中,示出了第二通道比例r2为25%的例子。

282.这样,第一通道区域91以及第二通道区域111在各单元区域75中以0%以上且100%以下(优选为超过0%且小于100%)的总通道比例rt(rt=r1+r2)形成。

283.在该方式中,各单元区域75中的总通道比例rt为50%。在该方式中,所有总通道比例rt设定为相等的值。因此,输出区域6内(单位面积)中的平均通道比例rav成为50%。平均通道比例rav是以总通道比例rt的总数除以所有总通道比例rt的和之后的数。总通道比例rt也可以按每个单元区域75调整。也就是,也可以将分别具有不同的值的多个总通道比例rt应用于每个单元区域75。总通道比例rt关系到半导体层2的温度上升。例如,若使总通道比例rt增加,则半导体层2的温度容易上升。另一方面,若使总通道比例rt减少,则半导体层2的温度难以上升。

284.也可以利用上述关系,根据半导体层2的温度分布来调整总通道比例rt。例如,使在半导体层2中温度容易变高的区域的总通道比例rt比较小,也可以使在半导体层2中温度难以变高的区域的总通道比例rt比较大。

285.作为在半导体层2中温度容易变高的区域,能够例示输出区域6的中央部。作为在半导体层2中温度难以变高的区域,能够例示输出区域6的周缘部。当然,也可以根据半导体层2的温度分布来调整总通道比例rt,并且调整平均通道比例rav。

286.也可以使多个具有20%以上且40%以下(例如25%)的总通道比例rt的单元区域75汇聚于温度容易变高的区域(例如中央部)。也可以使多个具有60%以上且80%以下(例如75%)的总通道比例rt的单元区域75汇聚于温度难以变高的区域(例如周缘部)。也可以使多个具有超过40%且小于60%(例如50%)的总通道比例rt的单元区域75汇聚于温度容易变高的区域以及温度难以变高的区域之间的区域。

287.并且,20%以上且40%以下的总通道比例rt、40%以上且60%以下的总通道比例rt以及60%以上且80%以下的总通道比例rt也可以按规则的排列应用于多个单元区域75。

288.作为一例,也可以将以25%(low)

→

50%(middle)

→

75%(high)的顺序重复的三种总通道比例rt应用于多个单元区域75。该情况下,平均通道比例rav也可以调整为50%。这种构造的情况下,能够以比较简单的设计来抑制在半导体层2的温度分布上形成偏颇。

289.图6是表示通过实际测量来调查有源钳位耐量eac以及面积电阻率ron

·

a的关系

的图表。图6的图表表示将第一misfet56以及第二misfet57同时控制为接通状态以及断开状态的情况的特性。

290.在图6中,纵轴表示有源钳位耐量eac[mj/mm2],横轴表示面积电阻率ron

·

a[mω

·

mm2]。如图3中所述,有源钳位耐量eac是相对于反电动势的耐量。面积电阻率ron

·

a表示通常动作时的半导体层2内的接通电阻。

[0291]

图6中示出第一标绘点p1、第二标绘点p2、第三标绘点p3以及第四标绘点p4。第一标绘点p1、第二标绘点p2、第三标绘点p3以及第四标绘点p4分别表示平均通道比例rav(也就是,各单元区域75所占的总通道比例rt)调整为66%、50%、33%以及25%的情况的特性。

[0292]

在使平均通道比例rav增加的情况下,在通常动作时,面积电阻率ron

·

a下降,在有源钳位动作时,有源钳位耐量eac下降。与此相反,在使平均通道比例rav下降的情况下,在通常动作时,面积电阻率ron

·

a增加,在有源钳位动作时,有源钳位耐量eac提高。

[0293]

若以面积电阻率ron

·

a为鉴,则平均通道比例rav优选为33%以上(更具体而言为33%以上且小于100%)。若以有源钳位耐量eac为鉴,则平均通道比例rav优选为小于33%(更具体而言超过0%且小于33%)。

[0294]

因平均通道比例rav的增加而面积电阻率ron

·

a下降是因为增加了电流路径。另外,因平均通道比例rav的增加而有源钳位耐量eac下降是因为引起了反电动势引起的急剧的温度上升。

[0295]

尤其是,在平均通道比例rav(总通道比例rt)比较大的情况下,在彼此相邻的第一沟槽栅极构造60以及第二沟槽栅极构造70之间的区域中,产生局部的而且急剧的温度上升的可能性变高。认为有源钳位耐量eac因这种温度上升而下降。

[0296]

另一方面,因平均通道比例rav的下降而面积电阻率ron

·

a增加的理由是因为电流路径缩小。因平均通道比例rav的下降而有源钳位耐量eac提高,认为平均通道比例rav(总通道比例rt)比较小,局部的而且急剧的温度上升被抑制。

[0297]

根据图6的图表的结果可知,基于平均通道比例rav(总通道比例rt)的调整法存在权衡关系,因此难以脱离该权衡的关系来兼顾优异的面积电阻率ron

·

a以及优异的有源钳位耐量eac。

[0298]

另一方面,根据图6的图表的结果可知,在功率misfet9中,在通常动作时,进行接近第一标绘点p1(rav=66%)的动作,在有源钳位动作时,进行接近第四标绘点p4(rav=25%)的动作,由此能够兼顾优异的面积电阻率ron

·

a以及优异的有源钳位耐量eac。因此,在半导体装置1中,实施以下的控制。

[0299]

图7是用于说明图1所示的半导体装置1的通常动作的剖面立体图。图8是用于说明图1所示的半导体装置1的有源钳位动作的剖面立体图。在图7以及图8中,为了便于说明,省略第一主面3之上的构造,简化了栅极控制配线17。

[0300]

参照图7,在功率misfet9的通常动作时,向第一栅极控制配线17a输入第一接通信号von1,向第二栅极控制配线17b输入第二接通信号von2,向第三栅极控制配线17c输入第三接通信号von3。

[0301]

第一接通信号von1、第二接通信号von2以及第三接通信号von3分别从控制器ic10输入。第一接通信号von1、第二接通信号von2以及第三接通信号von3分别具有栅极阈值电压vth以上的电压。第一接通信号von1、第二接通信号von2以及第三接通信号von3也可以分

别具有相等的电压。

[0302]

该情况下,第一开口侧电极87、第二开口侧电极107、第一底侧电极86以及第二底侧电极106分别成为接通状态。也就是,第一开口侧电极87、第二开口侧电极107、第一底侧电极86以及第二底侧电极106分别作为栅极电极发挥功能。

[0303]

由此,第一通道区域91以及第二通道区域111均被控制为接通状态。在图7中,由点状的影线示出接通状态的第一通道区域91以及第二通道区域111。

[0304]

其结果,第一misfet56以及第二misfet57这双方被驱动(全接通控制)。通常动作时的通道利用率ru为100%。通常动作时的特性通道比例rc为50%。通道利用率ru为第一通道区域91以及第二通道区域111中被控制为接通状态的第一通道区域91以及第二通道区域111的比例。

[0305]

此外,特性通道比例rc是平均通道比例rav乘以通道利用率ru得到的值(rc=rav

×

ru)。功率misfet9的特性(面积电阻率ron

·

a以及有源钳位耐量eac)基于特性通道比例rc来确定。由此,面积电阻率ron

·

a在图6的图表中接近由第二标绘点p2示出的面积电阻率ron

·

a。

[0306]

另一方面,参照图8,在功率misfet9的有源钳位动作时,向第一栅极控制配线17a输入断开信号voff,向第二栅极控制配线17b输入第一钳位接通信号vcon1,向第三栅极控制配线17c输入第二钳位接通信号vcon2。

[0307]

断开信号voff、第一钳位接通信号vcon1以及第二钳位接通信号vcon2分别从控制器ic10输入。断开信号voff具有小于栅极阈值电压vth的电压(例如基准电压)。第一钳位接通信号vcon1以及第二钳位接通信号vcon2分别具有栅极阈值电压vth以上的电压。第一钳位接通信号vcon1以及第二钳位接通信号vcon2也可以分别具有相等的电压。第一钳位接通信号vcon1以及第二钳位接通信号vcon2也可以具有通常动作时的电压以下或者小于通常动作时的电压的电压。

[0308]

该情况下,第一开口侧电极87成为断开状态,第一底侧电极86、第二底侧电极106以及第二开口侧电极107分别成为接通状态。由此,第一通道区域91被控制为断开状态并且第二通道区域111被控制为接通状态。在图8中,断开状态的第一通道区域91由涂抹影线示出,接通状态的第二通道区域111由点状的影线示出。

[0309]

其结果,第一misfet56被控制为断开状态、而第二misfet57被控制为接通状态(第二半接通控制)。由此,有源钳位动作时的通道利用率ru成为超过零且小于通常动作时的通道利用率ru。

[0310]

有源钳位动作时的通道利用率ru为50%。另外,有源钳位动作时的特性通道比例rc为25%。由此,有源钳位耐量eac在图6的图表中接近由第四标绘点p4示出的有源钳位耐量eac。

[0311]

该情况下,控制器ic10以在通常动作时以及有源钳位动作时之间应用不同的特性通道比例rc(通道的面积)的方式,对第一misfet56以及第二misfet57进行控制。更具体而言,控制器ic10以有源钳位动作时的通道利用率ru超过零且小于通常动作时的通道利用率ru的方式,对第一misfet56以及第二misfet57进行控制。

[0312]

更具体而言,控制器ic10在通常动作时将第一misfet56以及第二misfet57控制为接通状态,在有源钳位动作时将第一misfet56控制为断开状态并且将第二misfet57控制为

接通状态。

[0313]

因此,在通常动作时,特性通道比例rc相对地增加。即,在通常动作时,能够利用第一misfet56以及第二misfet57使电流流动。由此,电流路径相对地增加,从而能够实现面积电阻率ron

·

a(接通电阻)的降低。

[0314]

另一方面,在有源钳位动作时,特性通道比例rc相对地减少。即,在使第一misfet56停止的状态下能够利用第二misfet57使电流流动,因此能够由第二misfet57消耗(吸收)反电动势。由此,能够抑制反电动势引起的急剧的温度上升,因此能够实现有源钳位耐量eac的提高。

[0315]

因而,能够提供一种半导体装置1,其能够脱离图6所示的权衡的关系,实现优异的面积电阻率ron

·

a以及优异的有源钳位耐量eac的兼顾。

[0316]

此外,在上述的控制例中,对有源钳位动作时应用了第二半接通控制的例子进行了说明。但是,也可以在有源钳位动作时应用第一半接通控制。

[0317]

<过电流保护电路>

[0318]

图9是表示组装于半导体装置的过电流保护电路的第一构成例的图。本图的半导体装置200与上述的半导体装置1相同,作为高边开关ic发挥功能,该高边开关ic中,形成于半导体基板的第一主面侧(表面侧)的输出电极out(上述的源极电极12)与未图示的负载连接,形成于该半导体基板的第二主面侧(背面侧)的电源电极vbb(上述的漏极电极11)与未图示的电源端连接。

[0319]

半导体装置200具有功率misfet210、栅极控制电路220、以及过电流保护电路230。

[0320]

功率misfet210与上述的功率misfet9相同,是栅极分割型的功率晶体管,其构成为,根据经由第一栅极控制配线211输入的第一栅极控制信号g11和经由第二栅极控制配线212输入的第二栅极控制信号g12,对第一通道区域以及第二通道区域进行个别控制。

[0321]

例如,就功率misfet210的接通电阻值ron而言,当双方的通道区域接通时成为接通电阻值ron1,当仅单方的通道区域接通时成为比接通电阻值ron1高的接通电阻值ron2(例如ron2=20

×

ron1)。具体而言,例如也可以设为ron1=0.05ω、ron2=1ω。

[0322]

栅极控制电路220是相当于上述的栅极控制电路25的电路部,构成为,生成第一栅极控制信号g11以及第二栅极控制信号g12,并经由第一栅极控制配线211以及第二栅极控制配线212将各信号供给至功率misfet210。

[0323]

过电流保护电路230是相当于上述的过电流保护电路34的电路部,构成为,当流向功率misfet210的输出电流iout超过预定的阈值电流ith时,将第二通道区域断开。

[0324]

若按本图叙述,则过电流保护电路230包括比较器231、n通道型的misfet232及233、以及电流源234。

[0325]

比较器231构成为,对输入到非反转输入端(+)的预定的阈值电压vth1和输入到反转输入端(-)的输出电压vout(=输出电极out的端子电压、vbb-iout

×

ron)进行比较来生成过电流保护信号ocp1。就过电流保护信号ocp1而言,例如当vout>vth1时成为低电平(=过电流未检测时的逻辑电平),当vout<vth1时成为高电平(=过电流检测时的逻辑电平)。

[0326]

misfet232相当于第一晶体管,其构成为,根据过电流保护信号ocp1将第二栅极控制配线212与输出电极out之间导通/切断。就misfet232而言,当过电流保护信号ocp1为低

电平时断开,当过电流保护信号ocp1为高电平时接通。即,当过电流保护信号ocp1为高电平(=过电流检测时的逻辑电平)时,第二栅极控制配线212与输出电极out(甚至功率misfet210的源极)之间短路,因此第二通道区域被断开。

[0327]

misfet233相当于第二晶体管,其构成为,连接于电源电极vbb与阈值电压vth1的施加端之间,生成流向自身的恒定电流iref1和与自身的接通电阻值ron3相应的阈值电压vth1(=vbb-iref1

×

ron3)。此外,misfet233的接通电阻值ron3希望设定为比功率misfet210的接通电阻值ron(即接通电阻值ron1或ron2)充分高的值。具体而言,例如也可以设为ron3=5kω。

[0328]

另外,misfet233的栅极与栅极控制配线211及212中未连接misfet232的一方(即栅极控制配线211)连接。因此,misfet233与功率misfet210同步地接通/断开。如果是这种结构,在功率misfet210的断开期间不流动恒定电流iref1,因此可以不浪费电力。

[0329]

并且,作为misfet233,希望使用以与功率misfet210具有成对性的方式形成的栅极分割型的晶体管。如果是这种结构,能够精度良好地设定阈值电压vth1(甚至阈值电流ith),因此能够提高过电流检测精度。

[0330]

电流源234生成流向misfet233的恒定电流iref1。具体而言,例如也可以设为iref1=100μa。

[0331]

图10是表示功率misfet210接通期间的过电流保护动作的一例的图。此外,横轴表示流向功率misfet210的输出电流iout,纵轴表示输出电极out表现出的输出电压vout。

[0332]

当iout<ith(=iref1

×

ron3/ron1)时,功率misfet210的电压下降比较小,成为vout(=vbb-iout

×

ron1)>vth1(=vbb-iref1

×

ron3)。此时,过电流保护信号ocp1成为低电平,misfet232断开,因此第二栅极控制配线212与输出电极out之间打开。因此,功率misfet210的第一通道区域与第二通道区域均接通,因此功率misfet210的接通电阻值ron设定为接通电阻值ron1(例如0.05ω)。

[0333]

另一方面,若输出电流iout增大而成为iout>ith,则成为vout<vth1。此时,过电流保护信号ocp1成为高电平,misfet232接通,因此第二栅极控制配线212与输出电极out之间短路。因此,功率misfet210的第二通道区域被断开,仅第一通道区域成为接通状态,因此功率misfet210的接通电阻值ron从接通电阻值ron1升高为接通电阻值ron2(例如1ω)。其结果,可抑制流向功率misfet210的输出电流iout。

[0334]

例如,在ron1=0.05ω、ron2=1ω、ron3=5kω、iref1=100μa、vbb=14v的情况下,当输出电流iout超过10a时,功率misfet210的接通电阻值ron从ron1升高为ron2,输出电流iout被抑制为预定的上限值(=vbb/ron2=14a)。

[0335]

尤其是,本构成例的过电流保护电路230与进行功率晶体管的栅极反馈控制的现有结构不同,是不需要大型的元件(相位补偿电容器以及电流检测电阻等)的简单的电路结构。因此,例如可以说最适合于重视面积效率的廉价产品。此外,由于不进行功率misfet210的栅极反馈控制,因此虽然依赖于接通电阻值ron的偏差、温度特性,但由于以防止半导体装置200的破坏为目的,因此没有特别问题。

[0336]

图11是表示组装于半导体装置的过电流保护电路的第二构成例的图。本图的半导体装置300与上述的半导体装置1及200不同,作为低边开关ic发挥功能,该低边开关ic中,接地电极gnd与未图示的接地端连接,输出电极out与未图示的负载连接。

[0337]

半导体装置300具有功率misfet310、栅极控制电路320、以及过电流保护电路330。

[0338]

功率misfet310与上述的功率misfet9及210相同,是栅极分割型的功率晶体管,其构成为,根据经由第一栅极控制配线311输入的第一栅极控制信号g21和经由第二栅极控制配线312输入的第二栅极控制信号g22,对第一通道区域以及第二通道区域进行个别控制。

[0339]

例如,就功率misfet310的接通电阻值ron而言,当双方的通道区域接通时,成为接通电阻值ron1,当仅单方的通道区域接通时,成为比接通电阻值ron1高的接通电阻值ron2(例如ron2=20

×

ron1)。具体而言,例如,也可以设为ron1=0.05ω、ron2=1ω。

[0340]

栅极控制电路320是相当于上述的栅极控制电路25及220的电路部,构成为,生成第一栅极控制信号g21以及第二栅极控制信号g22,经由第一栅极控制配线311以及第二栅极控制配线312将各信号供给至功率misfet310。

[0341]

过电流保护电路330相当于上述的过电流保护电路34及230的电路部,构成为,当流向功率misfet310的输出电流iout超过预定的阈值电流ith时,将第二通道区域断开。

[0342]

若按本图叙述,则过电流保护电路330包括比较器331、n通道型的misfet332及333、以及电流源334。

[0343]

比较器331对输入到非反转输入端(+)的输出电压vout(=输出电极out的端子电压、iout

×

ron)和输入到反转输入端(-)的预定的阈值电压vth2进行比较来生成过电流保护信号ocp2。就过电流保护信号ocp2而言,例如当vout<vth2时,成为低电平(=过电流未检测时的逻辑电平),当vout>vth2时成为高电平(=过电流检测时的逻辑电平)。

[0344]

misfet332相当于第一晶体管,其构成为,根据过电流保护信号ocp2将第二栅极控制配线312与输出电极out之间导通/切断。就misfet332而言,当过电流保护信号ocp2为低电平时断开,当过电流保护信号ocp2为高电平时接通。即,当过电流保护信号ocp2为高电平(=过电流检测时的逻辑电平)时,第二栅极控制配线312与输出电极out(甚至功率misfet310的源极)之间短路,因此第二通道区域被断开。

[0345]

misfet333相当于第二晶体管,其构成为,连接于接地电极gnd与阈值电压vth2的施加端之间,生成流向自身的恒定电流iref2和与自身的接通电阻值ron3相应的阈值电压vth2(=iref2

×

ron3)。此外,misfet333的接通电阻值ron3希望设定为比功率misfet310的接通电阻值ron(即接通电阻值ron1或ron2)充分高的值。具体而言,例如也可以设为ron3=5kω。

[0346]

另外,misfet333的栅极与栅极控制配线311及312中未连接misfet332的一方(即栅极控制配线311)连接。因此,misfet333与功率misfet310同步地接通/断开。如果是这种结构,则在功率misfet310断开期间不流动恒定电流iref2,也可以不浪费电力。

[0347]

并且,作为misfet333,希望使用以与功率misfet310具有成对性的方式形成的栅极分割型的晶体管。如果是这种结构,能够精度良好地设定阈值电压vth2(甚至阈值电流ith),因此能够提高过电流检测精度。

[0348]

电流源334生成流向misfet333的恒定电流iref2。具体而言,例如,也可以设为iref2=100μa。

[0349]

图12是表示功率misfet310接通期间的过电流保护动作的一例的图。此外,横轴表示流向功率misfet310的输出电流iout,纵轴表示输出电极out表现出的输出电压vout。

[0350]

当iout<ith(=iref2

×

ron3/ron1)时,功率misfet310的电压下降比较小,因此

成为vout(=iout

×

ron1)<vth2(=iref2

×

ron3)。此时,过电流保护信号ocp2成为低电平,misfet332断开,因此第二栅极控制配线312与输出电极out之间打开。因此,功率misfet310的第一通道区域与第二通道区域均接通,因此功率misfet310的接通电阻值ron设定为接通电阻值ron1(例如0.05ω)。

[0351]

另一方面,若输出电流iout增大而成为iout>ith,则成为vout>vth2。此时,过电流保护信号ocp2成为高电平,misfet332接通,因此第二栅极控制配线312与输出电极out之间短路。因此,功率misfet310的第二通道区域被断开,仅第一通道区域成为接通状态,因此功率misfet310的接通电阻值ron从接通电阻值ron1升高为接通电阻值ron2(例如1ω)。其结果,可抑制流向功率misfet310的输出电流iout。

[0352]

例如,在ron1=0.05ω、ron2=1ω、ron3=5kω、iref1=100μa、vbb=14v的情况下,当输出电流iout超过10a时,功率misfet210的接通电阻值ron从ron1升高为ron2,输出电流iout被抑制为预定的上限值(=vbb/ron2=14a)。

[0353]

尤其是,本构成例的过电流保护电路330与进行功率晶体管的栅极反馈控制的现有结构不同,是不需要大型的元件(相位补偿电容器以及电流检测电阻等)的简单的电路结构。因此,例如可以说最适合于重视面积效率的廉价产品。此外,由于不进行功率misfet310的栅极反馈控制,因此虽然依赖于接通电阻值ron的偏差、温度特性,但由于以防止半导体装置300的破坏为目的,因此没有特别问题。

[0354]

<栅极分割型与并列连接型的对比>

[0355]

另外,通过并列连接接通电阻值不同的多个功率晶体管,并对它们进行个别控制,也能够进行与上述相同的过电流保护动作,来代替至此为止说明的栅极分割型的功率misfet210及310。

[0356]

但是,在使用了并列连接型的功率晶体管的结构中,在过电流检测时,输出电流仅集中流向接通电阻值高的小面积的功率晶体管,因此功率晶体管的发热容易成为问题。

[0357]

另一方面,如果是使用了栅极分割型的功率misfet210及310的结构,则即使在过电流检测时使功率misfet210及310的接通电阻值ron升高,输出电流iout也分散流向功率misfet210及310各自的形成区域整面,因此具有难以产生发热引起的元件破坏之类的优点。

[0358]

<对车辆的应用>

[0359]

图13是表示车辆的一构成例的外观图。本构成例的车辆x搭载电池(本图中未图示)、以及接受从电池供给电源电压而进行动作的各种电子设备x11~x18。此外,关于本图中的电子设备x11~x18的搭载位置,为了便于图示,存在与实际不同的情况。

[0360]

电子设备x11是进行与发动机关联的控制(注射控制、电子节流器控制、怠速控制、氧传感加热器控制、以及自动巡航控制等)的发动机控制器单元。

[0361]

电子设备x12是进行hid[high intensity discharged lamp]、drl[daytime running lamp]等的点亮熄灭控制的灯控制器单元。

[0362]

电子设备x13是进行与变速器关联的控制的变速器控制器单元。

[0363]

电子设备x14是进行与车辆x的运动关联的控制(abs[anti-lock brake system]控制、eps[electric power steering]控制、电子悬架控制等)的车体控制器单元。

[0364]

电子设备x15是进行门锁、防犯警报等的驱动控制的安全性控制器单元。

[0365]

电子设备x16是刮水器、电动门镜、电动车窗、缓冲器(减震器)、电动天窗、以及电动座椅等作为标准装备品、摄像机选项品,在工厂出货阶段组装于车辆x的电子设备。

[0366]

电子设备x17是车载a/v[audio/visual]设备、车辆导航系统、以及etc[electronic toll collection system,电子收费系统]等作为用户选项品而任意地装配于车辆x的电子设备。

[0367]

电子设备x18是车载鼓风机、油泵、水泵、电池冷却风扇等具备高耐压系统马达的电子设备。

[0368]

此外,以上说明的半导体装置1、以及半导体装置200及300均能够组装于电子设备x11~x18的任一个。

[0369]

<总括>

[0370]

以下,对至此为止说明的各种实施方式进行总括叙述。

[0371]

例如,本说明书中公开的半导体装置采用以下结构(第一结构),即,具有:栅极分割型的功率晶体管,其构成为,根据多个栅极控制信号对多个通道区域进行个别控制;栅极控制电路,其构成为,生成上述多个栅极控制信号;以及过电流保护电路,其构成为,当流向上述功率晶体管的输出电流超过阈值时,将上述多个通道区域的至少一个断开。

[0372]

此外,在由上述第一结构构成的半导体装置中,也可以采用以下结构(第二结构),即,上述功率晶体管包括:第一电极,其形成于半导体基板的第一主面侧;以及第二电极,其形成于上述半导体基板的第二主面侧。

[0373]

另外,在由上述第二结构构成的半导体装置中,也可以采用以下结构(第三结构),即,上述过电流保护电路包括:比较器,其构成为,对预定的阈值电压和上述第一电极的端子电压进行比较,并生成过电流保护信号;以及第一晶体管,其构成为,根据上述过电流保护信号将多个栅极控制配线的至少一个与上述第一电极之间导通/切断。

[0374]

另外,在由上述第三结构构成的半导体装置中,也可以采用以下结构(第四结构),即,上述过电流保护电路还包括第二晶体管,该第二晶体管构成为,连接于上述第二电极或者上述第一电极与上述阈值电压的施加端之间,根据流向自身的恒定电流生成上述阈值电压。

[0375]

另外,在由上述第四结构构成的半导体装置中,也可以采用以下结构(第五结构),即,上述第二晶体管与上述功率晶体管同步地接通/断开。

[0376]

另外,在由上述第四或第五结构构成的半导体装置中,也可以采用以下结构(第六结构),即,上述第二晶体管是以与上述功率晶体管具有成对性的方式形成的栅极分割型的晶体管。

[0377]

另外,在由上述第一~第六任一结构构成的半导体装置中,也可以采用以下结构(第七结构),即,上述功率晶体管作为高边开关发挥功能,就该高边开关而言,上述第一电极与负载连接,上述第二电极与电源端连接。

[0378]

另外,在由上述第一~第六任一结构构成的半导体装置中,也可以采用以下结构(第八结构),即,上述功率晶体管作为低边开关发挥功能,就该低边开关而言,上述第一电极与接地端连接,上述第二电极与负载连接。

[0379]

另外,例如,本说明书中公开的电子设备采用以下结构(第九结构),即,具有:由上述第一~第八任一结构构成的半导体装置;以及与上述半导体装置连接的负载。

[0380]

另外,例如,本说明书中公开的车辆采用以下结构(第十结构),即,具有由上述第九结构构成的电子设备。

[0381]

<其它变形例>

[0382]

此外,在上述的实施方式中,以车载用高边开关ic为例进行了说明,但本说明书中公开的发明的应用对象并不限定于此,以用于其它用途的车载用ipd[intelligent power device,智能功率器件](车载用低边开关ic、车载用电源ic等)为首,能够广泛应用于所有具有功率晶体管的半导体装置。

[0383]

即,本说明书中公开的发明除了上述实施方式以外,在不脱离其技术的创造主旨的范围内能够加以各种变更。即,上述实施方式应该被认为在所有方面都是例示性的,而不是限制性的,本发明的技术范围不是由上述实施方式的说明示出而是由技术方案的范围示出,应该理解为,包括与技术方案的范围相同的意思以及属于范围内的所有变更。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1