一种基于GaAs衬底的低功耗50~4000MHz低噪放芯片的制作方法

一种基于gaas衬底的低功耗50~4000mhz低噪放芯片

技术领域

1.本实用新型涉及射频器件领域,尤其涉及一种基于gaas衬底的低功耗50~4000mhz低噪放芯片。

背景技术:

2.随着设备小型化的发展,射频应用对芯片小型化、多功能性、高可靠性、低功耗性、提出了更高的要求。对于射频放大器而言,稳定性和性能的要求也越来越高。低噪放(low-noiseamplifier)是一类特殊的电子放大器,主要用于通讯系统中将接收自天线的信号放大,以便于后级的电子设备处理。由于来自天线的信号一般都非常微弱,低噪音放大器一般情况下均位于非常靠近天线的部位,以减小信号通过传输线的损耗。

3.然而在现有技术中,目前半导体放大器芯片多采用有源偏置电路的结构,内部走线结构相对复杂,芯片面积较大,并且他们的工作频率带宽相对较窄,功耗大。

4.因此,针对上述问题,提供一种基于gaas衬底的低功耗50~4000mhz低噪放芯片,是本领域亟待解决的技术问题。

技术实现要素:

5.本实用新型的目的在于克服现有技术的不足,提供一种基于gaas衬底的低功耗 50~4000mhz低噪放芯片。

6.本实用新型的目的是通过以下技术方案来实现的:

7.本实用新型的第一方面,提供一种基于gaas衬底的低功耗50~4000mhz低噪放芯片,包括陶瓷基板和芯片本体,所述芯片本体通过导电胶粘接于所述陶瓷基板上;

8.所述陶瓷基板上设置有第一隔直电容、滤波电容、扼流电感、射频输入焊盘和射频输出焊盘,射频输入信号依次通过第一隔直电容和射频输入焊盘后输入至芯片本体的射频输入端,芯片本体输出的射频输出信号通过射频输出焊盘输出,电源输入信号依次通过滤波电容、扼流电感、射频输出焊盘后输入至芯片本体的电源输入端。

9.进一步地,所述芯片本体为二级放大结构。

10.进一步地,所述芯片本体包括射频输入端和射频输出端;

11.所述射频输入端通过第一微带线mline1与第一微带t形结mtee1的第一端连接,第一微带t形结mtee1的第二端依次通过第二微带线mline2、第一晶体管transistor1与第二微带t形结mtee2的第一端连接,第一微带t形结mtee1的第三端依次通过电阻r1、第三微带线mline3与第二微带t形结mtee2的第二端连接;

12.第二微带t形结mtee2的第三端通过第五微带线mline5与第三微带t形结mtee3的第一端连接,第三微带t形结mtee3的第二端依次通过第六微带线mline6、第二晶体管 transistor2、第九微带线mline9与第四微带t形结mtee4的第一端连接,第三微带t形结 mtee3的第三端依次通过电阻r2、第七微带线mline7与第四微带t形结mtee4的第二端连接;

13.第四微带t形结mtee4的第三端通过第十微带线mline10与射频输出端连接。

14.进一步地,所述第一晶体管transistor1的接地端通过第四微带线mline4接地,所述第二晶体管transistor2的接地端通过第八微带线mline8接地。

15.进一步地,所述芯片本体还包括第一静电屏蔽装置esd1和第二静电屏蔽装置esd2,所述第一静电屏蔽装置esd1并联于所述射频输入端,所述第二静电屏蔽装置esd2并联于所述射频输出端。

16.进一步地,所述滤波电容为三个并联在电源输入信号输入端的接地电容。

17.进一步地,所述陶瓷基板上设置有第二隔直电容,芯片本体的射频输出端依次通过射频输出焊盘和第二隔直电容输出射频输出信号。

18.进一步地,所述陶瓷基板和芯片本体通过qfn2*2封装在一起。

19.进一步地,所述电源输入端输入+3.3v的偏置电压。

20.进一步地,所述芯片本体的大小为1.2mm

×

0.6mm。

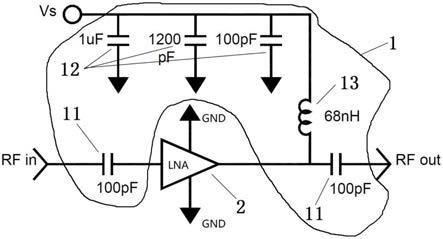

21.本实用新型的有益效果是:

22.(1)在本实用新型的一示例性实施例中,将直流的电源输入焊盘和射频输出焊盘共用(即仅通过射频输出焊盘实现射频输出和电源输入),可以节省芯片本体内部元件布局的空间;同时,第一隔直电容、滤波电容和扼流电感均布置在芯片本体外部的陶瓷基板上,这样做可以节省裸芯片本体的面积,还可以灵活方便的调节和选用外部元件。并且相较于分离式设计,粘贴式设计更加安全可靠。

23.(2)在本实用新型的又一示例性实施例中,相较于现有技术中的单极晶体管放大的形式,本示例性实施例中的芯片本体采用两极晶体管放大的形式,从而实现高增益的特点。

24.(3)在本实用新型的又一示例性实施例中,不仅给出了采用两极晶体管放大的具体实现形式,而且还采用负反馈结构,从而拓展了芯片本体的工作宽带,并且与传输线进行输入匹配可实现良好的输入驻波系数。

25.(4)在本实用新型的又一示例性实施例中,利用并联在输入和输出端口的esd装置,实现良好的静电屏蔽功能,有效的保护芯片,提高芯片的可靠性和安全性。

附图说明

26.图1为本实用新型一示例性实施例提供的低噪放芯片连接示意图;

27.图2为本实用新型一示例性实施例提供的陶瓷基板电路连接示意图;

28.图3为本实用新型一示例性实施例提供的芯片本体电路连接示意图;

29.图中,1-陶瓷基板,11-第一隔直电容,12-滤波电容,13-扼流电感,14-射频输入焊盘, 15-射频输出焊盘,16-第二隔直电容,2-芯片本体,201-负反馈结构。

具体实施方式

30.下面结合附图对本实用新型的技术方案进行清楚、完整地描述,显然,所描述的实施例是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

31.在本实用新型的描述中,需要说明的是,属于“中心”、“上”、“下”、“左”、“右”、“竖

transistor2、第九微带线mline9与第四微带t形结mtee4的第一端连接,第三微带t形结 mtee3的第三端依次通过电阻r2、第七微带线mline7与第四微带t形结mtee4的第二端连接;

43.第四微带t形结mtee4的第三端通过第十微带线mline10与射频输出端连接。

44.具体地,该示例性实施例中不仅给出了采用两极晶体管放大的具体实现形式,而且还采用负反馈结构201,从而拓展了芯片本体2的工作宽带,并且与传输线进行输入匹配可实现良好的输入驻波系数。

45.其中,第一晶体管transistor1和第二晶体管transistor2均为phemt。

46.更优地,在一示例性实施例中,如图3所示,所述第一晶体管transistor1的接地端通过第四微带线mline4接地,所述第二晶体管transistor2的接地端通过第八微带线mline8接地。

47.更优地,在一示例性实施例中,如图3所示,所述芯片本体2还包括第一静电屏蔽装置 esd1和第二静电屏蔽装置esd2,所述第一静电屏蔽装置esd1并联于所述射频输入端,所述第二静电屏蔽装置esd2并联于所述射频输出端。

48.具体地,在该示例性实施例中,利用并联在输入和输出端口的esd装置,实现良好的静电屏蔽功能,有效的保护芯片,提高芯片的可靠性和安全性。

49.更优地,在一示例性实施例中,如图2所示,所述滤波电容12为三个并联在电源输入信号输入端的接地电容。

50.其中,在一示例性实施例中,三个滤波电容12的大小分别为1uf、1200pf、100pf。

51.更优地,在一示例性实施例中,如图2所示,所述陶瓷基板1上设置有第二隔直电容16,芯片本体2的射频输出端依次通过射频输出焊盘15和第二隔直电容16输出射频输出信号。

52.其中第一隔直电容11和第二隔直电容16的大小均为100pf。

53.更优地,在一示例性实施例中,所述陶瓷基板和芯片本体通过qfn2*2封装在一起。

54.更优地,在一示例性实施例中,所述电源输入端输入+3.3v的偏置电压。

55.更优地,在一示例性实施例中,所述芯片本体的大小为1.2mm

×

0.6mm。

56.显然,上述实施例仅仅是为清楚地说明所作的举例,而并非对实施方式的限定,对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其他不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。而由此所引申出的显而易见的变化或变动仍处于本实用新型创造的保护范围之中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1