像素电路及其驱动方法与流程

本发明实施例涉及显示,尤其涉及一种像素电路及其驱动方法。

背景技术:

1、随着显示技术的不断发展,显示面板的应用越来越广泛,人们对于显示面板的性能要求也越来越高。显示面板中的像素电路用于驱动发光器件进行发光显示,目前,现有像素电路难以适用于高分辨率和高刷新频率的显示,并且像素电路的驱动信号的产生方式较为复杂。

技术实现思路

1、本发明实施例提供一种像素电路及其驱动方法,以提升显示效果,并降低驱动难度。

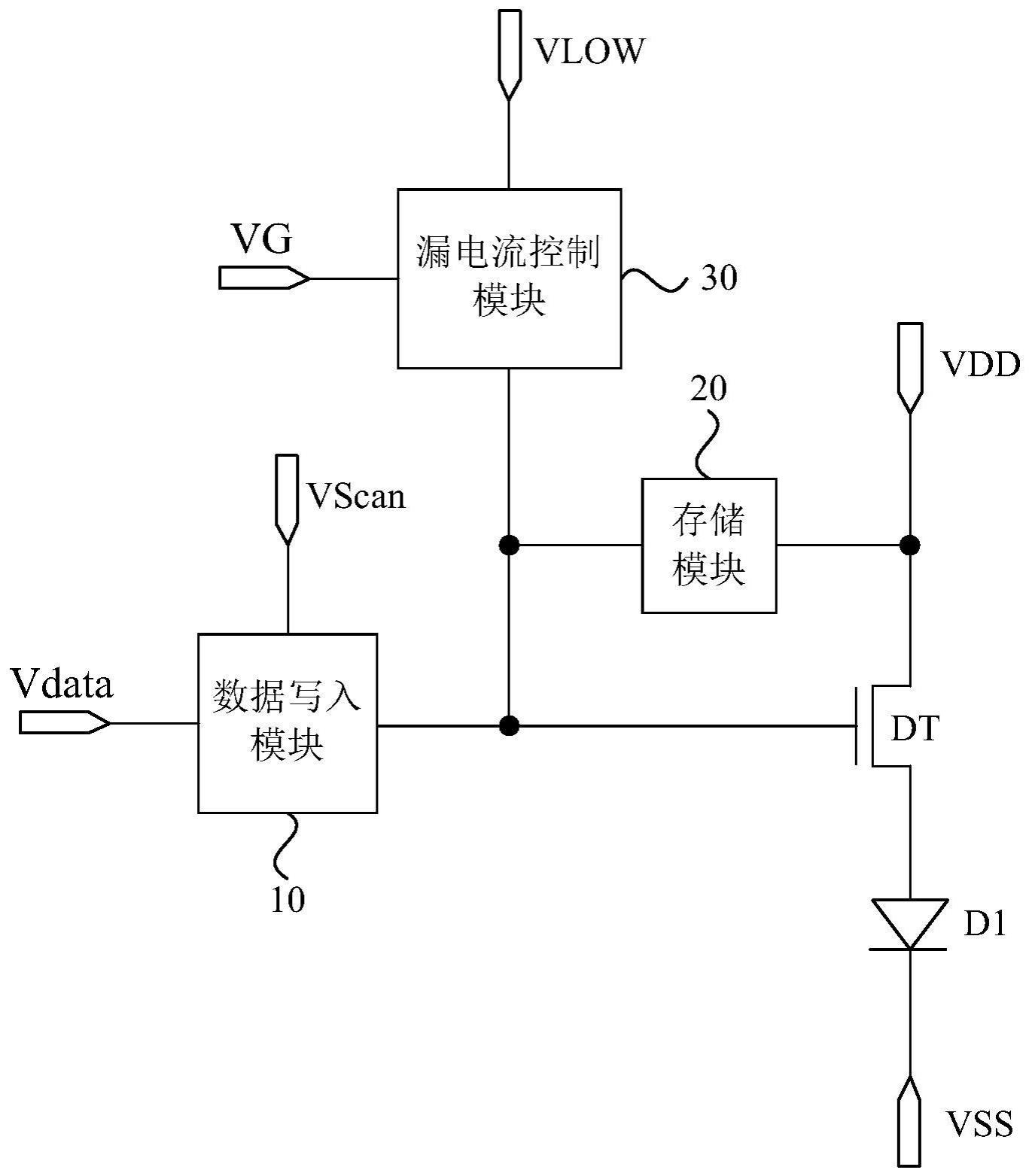

2、第一方面,本发明实施例提供了一种像素电路,包括:数据写入模块、存储模块、漏电流控制模块和驱动晶体管;

3、所述数据写入模块用于在数据写入阶段向所述驱动晶体管的栅极写入数据电压;

4、所述存储模块的第一端连接所述驱动晶体管的栅极,第二端接入固定电压,所述存储模块用于存储所述驱动晶体管的栅极电压;

5、所述漏电流控制模块连接于复位电压端和所述存储模块的第一端之间,所述漏电流控制模块的控制端接入控制信号,所述漏电流控制模块用于在发光阶段响应所述控制信号控制所述存储模块的第一端和所述复位电压端之间的漏电流的大小,以控制所述存储模块存储的所述驱动晶体管的栅极电压的大小;

6、所述驱动晶体管用于响应自身的栅极电压产生驱动电流,以驱动发光器件发光。

7、可选地,所述漏电流控制模块包括至少两个晶体管,所述至少两个晶体管串接于所述复位电压端和所述存储模块的第一端之间,且至少两个所述晶体管的沟道宽长比均不同;

8、所述至少两个晶体管中的每个晶体管的栅极均作为所述漏电流控制模块的控制端并接入对应的控制信号,每个所述晶体管均用于响应对应的所述控制信号而导通或关断,并在关断时进行漏电。

9、可选地,所述至少两个晶体管包括第一晶体管、第二晶体管、第三晶体管、第四晶体管、第五晶体管、第六晶体管、第七晶体管和第八晶体管;所述第一晶体管、所述第二晶体管、所述第三晶体管、所述第四晶体管、所述第五晶体管、所述第六晶体管、所述第七晶体管和所述第八晶体管中的至少两个晶体管的沟道宽长比不同;

10、所述第一晶体管、所述第二晶体管、所述第三晶体管、所述第四晶体管、所述第五晶体管、所述第六晶体管、所述第七晶体管和所述第八晶体管串接于所述复位电压端和所述存储模块的第一端之间,所述第一晶体管、所述第二晶体管、所述第三晶体管、所述第四晶体管、所述第五晶体管、所述第六晶体管、所述第七晶体管和所述第八晶体管的栅极分别接入不同的控制信号。

11、可选地,由所述第一晶体管至所述第八晶体管,各晶体管的沟道宽长比依次增大;

12、优选地,由所述第一晶体管至所述第八晶体管,各晶体管的沟道宽长比的比例为1:2:4:8:16:32:64:128。

13、可选地,所述至少两个晶体管中的每个晶体管的栅极各连接有一开关单元和一存储单元,以通过所述开关单元接入所述控制信号,并通过所述存储单元存储栅极电压。

14、可选地,所述漏电流控制模块包括漏电控制晶体管,所述漏电控制晶体管的栅极接入所述控制信号,所述漏电控制晶体管的第一极连接所述复位电压端,所述漏电控制晶体管的第二极连接所述存储模块的第一端,所述漏电控制晶体管的沟道宽长比可调。

15、可选地,所述漏电流控制模块还用于在初始化阶段响应所述控制信号而导通,将所述复位电压端的复位电压写入所述驱动晶体管的栅极。

16、可选地,还包括第一发光控制模块、第二发光控制模块和补偿模块;

17、所述第一发光控制模块连接于电源电压端和所述驱动晶体管的第一极之间,所述第二发光控制模块连接于所述驱动晶体管的第二极和所述发光器件之间,所述第一发光控制模块和所述第二发光控制模块均用于对发光阶段进行控制;

18、所述补偿模块连接于所述驱动晶体管的第二极和栅极之间,所述补偿模块用于对所述驱动晶体管的阈值电压进行补偿。

19、第二方面,本发明实施例还提供了一种像素电路的驱动方法,所述像素电路包括:数据写入模块、存储模块、漏电流控制模块和驱动晶体管;所述存储模块的第一端连接所述驱动晶体管的栅极,第二端接入固定电压,所述存储模块用于存储所述驱动晶体管的栅极电压;所述漏电流控制模块连接于复位电压端和所述存储模块的第一端之间,所述漏电流控制模块的控制端接入控制信号;

20、所述像素电路的驱动方法包括:

21、在数据写入阶段,通过所述数据写入模块向所述驱动晶体管的栅极写入数据电压;

22、在发光阶段,通过所述漏电流控制模块响应所述控制信号控制所述存储模块的第一端和所述复位电压端之间的漏电流的大小,以控制所述存储模块存储的所述驱动晶体管的栅极电压的大小,并通过所述驱动晶体管响应自身的栅极电压产生驱动电流,以驱动发光器件发光。

23、可选地,所述漏电流控制模块包括至少两个晶体管,所述至少两个晶体管串接于所述复位电压端和所述存储模块的第一端之间,且至少两个所述晶体管的沟道宽长比不同;所述至少两个晶体管中的每个晶体管的栅极均作为所述漏电流控制模块的控制端;

24、所述像素电路的驱动方法包括:

25、在初始化阶段,向所述至少两个晶体管的栅极施加对应的控制信号,以控制所述至少两个晶体管响应对应的所述控制信号而导通,将所述复位电压端的复位电压写入所述驱动晶体管的栅极;

26、在发光阶段,向所述至少两个晶体管的栅极施加对应的控制信号,以控制所述至少两个晶体管响应对应的所述控制信号而导通或关断,以控制所述存储模块的第一端和所述复位电压端之间的漏电流的大小;

27、优选地,所述像素电路的驱动方法还包括:

28、通过调整所述复位电压的大小来控制所述存储模块的第一端和所述复位电压端之间的漏电流的大小。

29、本发明实施例提供的像素电路及其驱动方法,在数据写入阶段,通过数据写入模块向驱动晶体管的栅极写入数据电压,同时通过存储模块存储驱动晶体管的栅极电压。在发光阶段,通过漏电流控制模块控制存储模块的第一端和复位电压端之间的漏电流的大小,以控制存储模块存储的电压及驱动晶体管的栅极电压由数据电压变化为复位电压的放电时间,从而控制驱动晶体管响应其栅极电压产生驱动电流的时间,并控制发光器件的发光时间,实现了发光器件的发光亮度及显示面板的显示灰阶控制。与现有技术相比,本方案在一帧内仅对像素电路进行一次数据电压写入,无需将一帧的数据分为多个子帧进行写入,有助于节约数据写入时间,可适用于高分辨率和高刷新频率的显示装置。本方案在不同帧可以向像素电路写入不同的数据电压,以实现模拟式驱动,通过控制存储模块的第一端和复位电压端之间的漏电流来控制发光器件的发光时间,从而控制发光亮度,以实现数字式驱动,无需产生复杂的脉冲宽度调制信号来控制发光时间。综上所述,本方案中的像素电路实现了数字驱动和模拟驱动相结合的驱动方式,有助于在提升显示效果的同时降低驱动难度。

技术特征:

1.一种像素电路,其特征在于,包括:数据写入模块、存储模块、漏电流控制模块和驱动晶体管;

2.根据权利要求1所述的像素电路,其特征在于,所述漏电流控制模块包括至少两个晶体管,所述至少两个晶体管串接于所述复位电压端和所述存储模块的第一端之间,且至少两个所述晶体管的沟道宽长比不同;

3.根据权利要求2所述的像素电路,其特征在于,所述至少两个晶体管包括第一晶体管、第二晶体管、第三晶体管、第四晶体管、第五晶体管、第六晶体管、第七晶体管和第八晶体管;所述第一晶体管、所述第二晶体管、所述第三晶体管、所述第四晶体管、所述第五晶体管、所述第六晶体管、所述第七晶体管和所述第八晶体管中的至少两个晶体管的沟道宽长比不同;

4.根据权利要求3所述的像素电路,其特征在于,由所述第一晶体管至所述第八晶体管,各晶体管的沟道宽长比依次增大;

5.根据权利要求2所述的像素电路,其特征在于,所述至少两个晶体管中的每个晶体管的栅极各连接有一开关单元和一存储单元,以通过所述开关单元接入所述控制信号,并通过所述存储单元存储栅极电压。

6.根据权利要求1所述的像素电路,其特征在于,所述漏电流控制模块包括漏电控制晶体管,所述漏电控制晶体管的栅极接入所述控制信号,所述漏电控制晶体管的第一极连接所述复位电压端,所述漏电控制晶体管的第二极连接所述存储模块的第一端,所述漏电控制晶体管的沟道宽长比可调。

7.根据权利要求1所述的像素电路,其特征在于,所述漏电流控制模块还用于在初始化阶段响应所述控制信号而导通,将所述复位电压端的复位电压写入所述驱动晶体管的栅极。

8.根据权利要求1所述的像素电路,其特征在于,还包括第一发光控制模块、第二发光控制模块和补偿模块;

9.一种像素电路的驱动方法,其特征在于,所述像素电路包括:数据写入模块、存储模块、漏电流控制模块和驱动晶体管;所述存储模块的第一端连接所述驱动晶体管的栅极,第二端接入固定电压,所述存储模块用于存储所述驱动晶体管的栅极电压;所述漏电流控制模块连接于复位电压端和所述存储模块的第一端之间,所述漏电流控制模块的控制端接入控制信号;

10.根据权利要求9所述的像素电路的驱动方法,其特征在于,所述漏电流控制模块包括至少两个晶体管,所述至少两个晶体管串接于所述复位电压端和所述存储模块的第一端之间,且至少两个所述晶体管的沟道宽长比不同;所述至少两个晶体管中的每个晶体管的栅极均作为所述漏电流控制模块的控制端;

技术总结

本发明实施例公开了一种像素电路及其驱动方法。像素电路包括:数据写入模块、存储模块、漏电流控制模块和驱动晶体管;数据写入模块用于在数据写入阶段向驱动晶体管的栅极写入数据电压;存储模块用于存储驱动晶体管的栅极电压;漏电流控制模块连接于复位电压端和存储模块的第一端之间,漏电流控制模块的控制端接入控制信号,漏电流控制模块用于在发光阶段响应控制信号控制存储模块的第一端和复位电压端之间的漏电流的大小,以控制存储模块存储的驱动晶体管的栅极电压的大小;驱动晶体管用于响应自身的栅极电压产生驱动电流,以驱动发光器件发光。本方案实现了数字驱动和模拟驱动相结合的驱动方式,有助于在提升显示效果的同时降低驱动难度。

技术研发人员:黄亚东,张金刚,张东豪,廖一遂,钱先锐,叶本银,袁盼,黄飞

受保护的技术使用者:成都辰显光电有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!