显示装置及电子设备的制作方法

本公开涉及显示装置和包括该显示装置的电子设备。

背景技术:

1、近年来,作为有机电致发光(el)显示装置(以下简称为“显示装置”),已经提出了具有所有子像素共用的有机层的装置。然而,在具有这种配置的显示装置中,驱动电流的泄漏可能发生在相邻子像素之间。因此,已经提出了一种用于防止驱动电流在相邻子像素之间泄漏的技术(例如,参见专利文献1)。

2、引用列表

3、专利文件

4、专利文献1:wo 2020/111202单行本

技术实现思路

1、发明要解决的问题

2、如上所述,近年来,在具有对所有子像素共用的有机el层的显示装置中,期望用于防止在相邻子像素之间产生的驱动电流的泄漏的技术。

3、本公开的目的是提供一种能够防止在相邻子像素之间产生驱动电流的泄漏的显示装置以及包括该显示装置的电子设备。

4、解决问题的方法

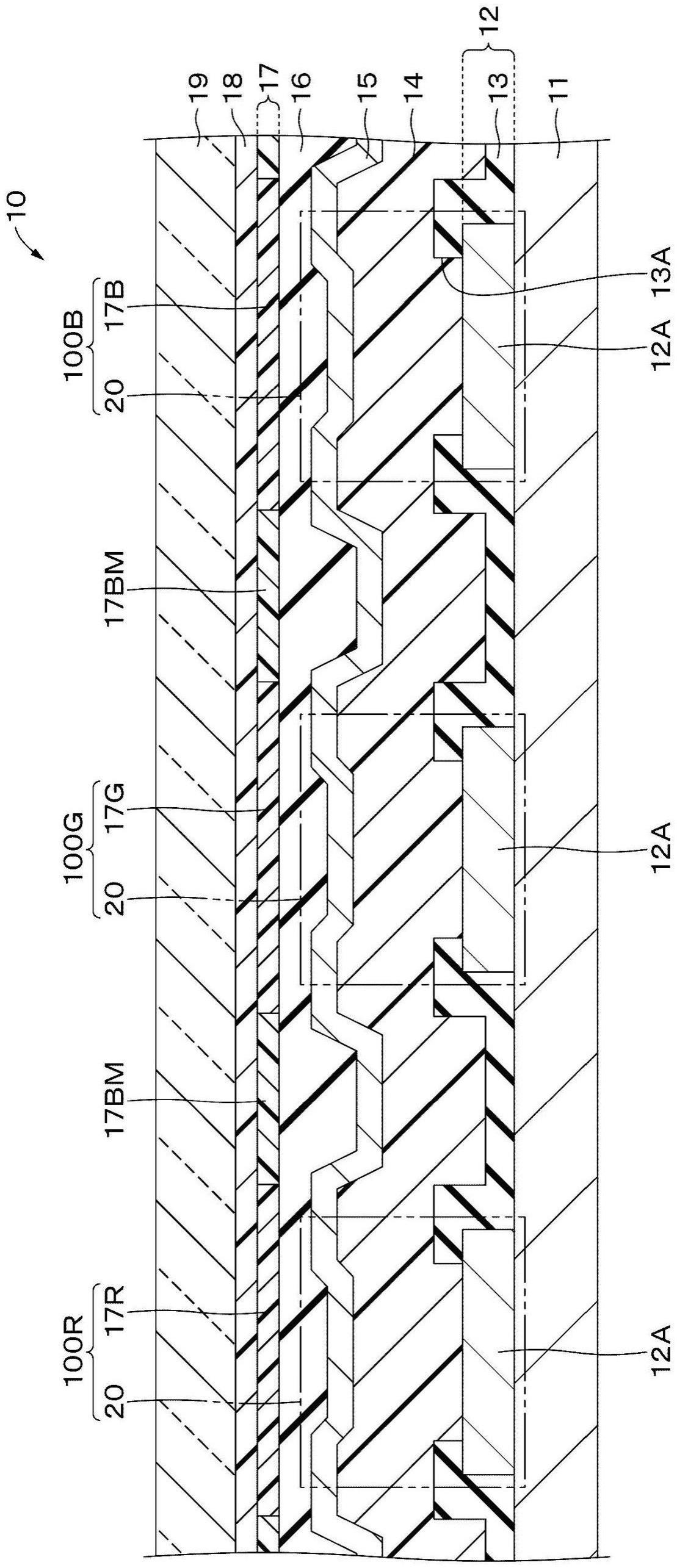

5、为了实现上述目的,第一种公开是一种显示装置,包括:

6、第一电极层,具有二维布置的多个电极;

7、第二电极层,被设置为面向所述第一电极层;

8、设置于第一电极层和第二电极层之间的电致发光层;以及

9、绝缘层,被设置在彼此相邻的电极之间,其中

10、所述电致发光层包括空穴传输层,所述空穴传输层与所述绝缘层相邻,以及

11、在所述绝缘层和所述空穴传输层之间的界面处的能级einterface(1)和所述空穴传输层的体相中的能级ebulk(1)满足以下公式(1)。

12、0≤ebulk(1)-einterface(1)≤0.3 ev (1)

13、第二公开是一种显示装置,包括:

14、第一电极层,具有二维布置的多个电极;

15、第二电极层,被设置为面向所述第一电极层;

16、设置于第一电极层和第二电极层之间的电致发光层;以及

17、绝缘层,被设置在彼此相邻的电极之间,其中

18、所述电致发光层包括空穴传输层,

19、所述空穴传输层至少包括第一空穴传输层和第二空穴传输层,所述第一空穴传输层与所述绝缘层相邻,并且

20、所述第一空穴传输层的体相的能级ebulk(2a)和所述第二空穴传输层的体相的能级ebulk(2b)满足下式(2)。

21、0≤ebulk(2b)-ebulk(2a)≤0.3 ev (2)

22、第三公开是一种显示装置,包括:

23、第一电极层,具有二维布置的多个电极;

24、第二电极层,被设置为面向所述第一电极层;

25、设置于第一电极层和第二电极层之间的电致发光层;以及

26、绝缘层,被设置在彼此相邻的电极之间,其中

27、所述电致发光层包括空穴传输层和空穴注入层,所述空穴注入层与所述绝缘层相邻,以及

28、所述空穴注入层与空穴传输层之间的界面处的能级eintface(3)和所述空穴传输层的体相中的能级ebulk(3)满足下式(3)。

29、0≤ebulk(3)-einterface(3)≤0.3 ev (3)

30、第四公开是一种显示装置,包括:

31、第一电极层,具有二维布置的多个电极;

32、第二电极层,被设置为面向所述第一电极层;

33、设置于第一电极层和第二电极层之间的电致发光层;以及

34、绝缘层,被设置在彼此相邻的电极之间,其中

35、所述电致发光层包括空穴传输层和空穴注入层,所述空穴注入层与所述绝缘层相邻,

36、所述空穴传输层至少包括第一空穴传输层和第二空穴传输层,所述第一空穴传输层邻近所述空穴注入层,以及

37、所述第一空穴传输层的体相的能级ebulk(4a)和所述第二空穴传输层的体相的能级ebulk(4b)满足下式(4)。

38、0≤ebulk(4b)—ebulk(4a)≤0.3 ev (4)

技术特征:

1.一种显示装置,包括:

2.一种显示装置,包括:

3.一种显示装置,包括:

4.一种显示装置,包括:

5.根据权利要求3所述的显示装置,其中

6.根据权利要求5所述的显示装置,其中,

7.根据权利要求1所述的显示装置,其中,

8.一种电子设备,包括根据权利要求1所述的显示装置。

技术总结

提供了一种显示装置,利用该显示装置可以抑制发生在相邻子像素之间的驱动电流泄漏。该显示装置设置有:第一电极层,包括二维布置的多个电极;第二电极层,被设置成面向第一电极层;设置于第一电极层和第二电极层之间的电致发光层;以及设置在相邻电极之间的绝缘层。电致发光层设置有空穴传输层,空穴传输层与绝缘层相邻。绝缘层与空穴传输层之间的界面处的能级E<subgt;interface(1)</subgt;和空穴传输层的体相中的能级E<subgt;bulk(1)</subgt;满足公式(1)。(1):0≤E<subgt;bulk(1)</subgt;-E<subgt;interface(1)</subgt;≤0.3eV。

技术研发人员:须佐纮子,塚本竹雄,君岛美树,渡部彰

受保护的技术使用者:索尼集团公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!