信号生成电路,信号生成方法和显示装置与流程

本发明涉及显示,尤其涉及一种信号生成电路,信号生成方法和显示装置。

背景技术:

1、在相关技术中,eoa(生成发光控制信号的驱动模组)的信号输入和提供驱动信号的goa(栅极驱动模组)的信号输入主要是时钟信号clk和stv信号(起始信号)。由于goa中的clk所带负载与goa所带负载不同,其造成的rc delay(延迟)也会不同,由于负载不同会带来信号的下降时间改变,从而导致eoa提供的发光控制信号的边沿和goa提供的驱动信号的边沿不对齐的现象。

技术实现思路

1、本发明的主要目的在于提供一种信号生成电路、信号生成方法和显示装置,解决现有技术中输出端输出的信号(该信号可以为发光控制信号)的上升沿与所述驱动信号输出端提供的驱动信号的下降沿之间存在时序错位现象的问题。

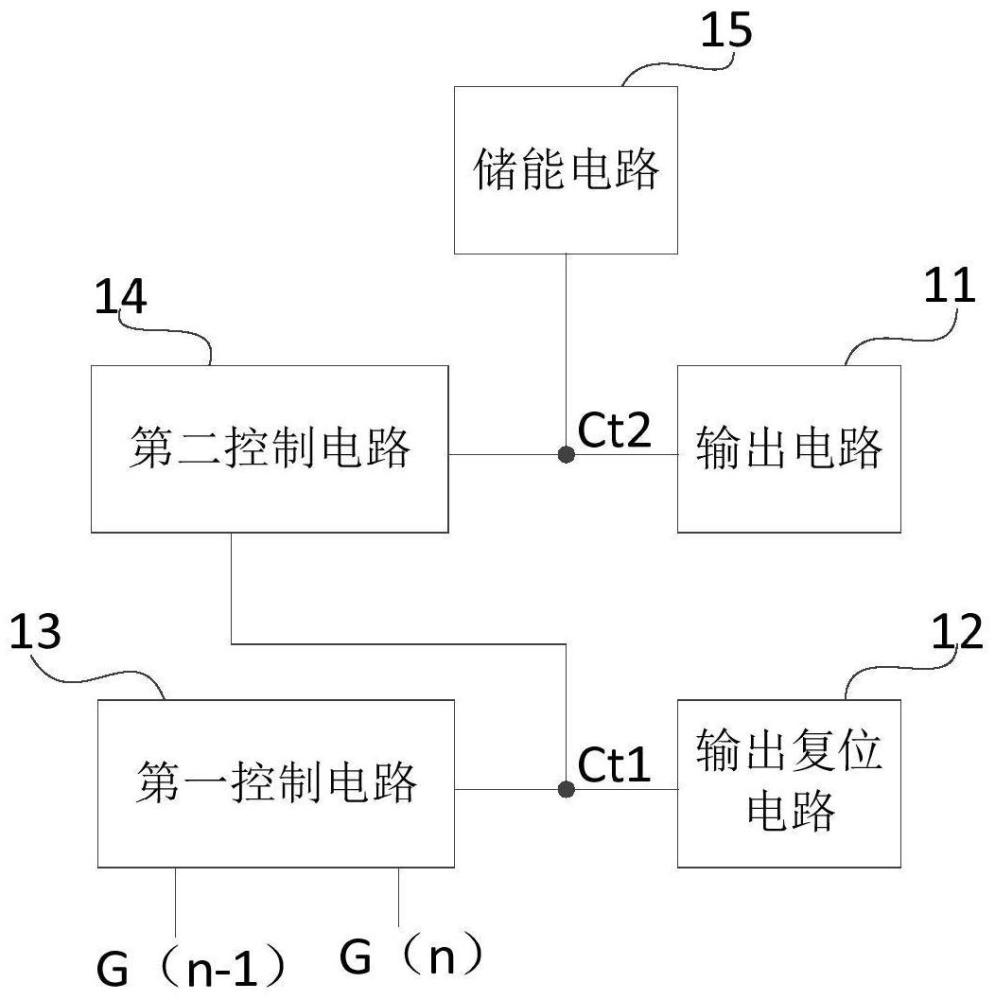

2、本发明实施提供一种信号生成电路,包括输出电路、输出复位电路、第一控制电路、第二控制电路和储能电路,其中,

3、所述输出复位电路分别与第一控制端、第一电压端和输出端电连接,用于在所述第一控制端的电位的控制下,控制所述输出端与所述第一电压端之间连通;

4、所述输出电路分别与第二控制端、第二电压端和输出端电连接,用于在所述第二控制端的电位的控制下,控制所述输出端与所述第二电压端之间连通;

5、所述储能电路与所述第二控制端电连接,用于储存电能;

6、所述第一控制电路分别与复位端、驱动信号输出端和所述第一控制端电连接,用于在所述复位端提供的复位信号和所述驱动信号输出端提供的驱动信号的控制下,控制所述第一控制端的电位;所述复位端为相邻上一级驱动信号输出端;

7、所述第二控制电路分别与第一控制端与所述第二控制端电连接,用于根据第一控制端的电位,控制所述第二控制端的电位。

8、可选的,所述第一控制电路用于在所述复位信号的控制下,控制所述复位端与所述第一控制端之间连通,并用于在所述驱动信号的控制下,控制所述驱动信号输出端与所述第一控制端之间连通。

9、可选的,所述第一控制电路包括第一晶体管和第二晶体管;

10、所述第一晶体管的控制极与所述第一晶体管的第一极与所述驱动信号输出端电连接,所述第一晶体管的第二极与所述第一控制端电连接;

11、所述第二晶体管的控制极与所述第二晶体管的第二极与所述复位端电连接,所述第二晶体管的第一极与所述第一控制端电连接。

12、可选的,所述第二控制电路还分别与第三电压端和第四电压端电连接;

13、所述第二控制电路包括第三晶体管和第四晶体管;

14、所述第三晶体管的控制极与所述第三晶体管的第一极与所述第四电压端电连接,所述第三晶体管的第二极与所述第二控制端电连接;

15、所述第四晶体管的控制极与所述第一控制端电连接,所述第四晶体管的第一极与所述第二控制端电连接,所述第四晶体管的第二极与所述第三电压端电连接。

16、可选的,所述第二控制电路还分别与第三电压端、时钟信号端和第四电压端电连接,用于在所述时钟信号端提供的时钟信号的控制下,控制所述第二控制端与所述第四电压端之间连通,并在所述第一控制端的电位的控制下,控制所述第二控制端与所述第三电压端之间连通。

17、可选的,所述第二控制电路包括第五晶体管和第六晶体管;

18、所述第五晶体管的控制极与所述时钟信号端电连接,所述第五晶体管的第一极与所述第四电压端电连接,所述第五晶体管的第二极与所述第二控制端电连接;

19、所述第六晶体管的控制极与所述第一控制端电连接,所述第六晶体管的第一极与所述第三电压端电连接,所述第六晶体管的第二极与所述第二控制端电连接。

20、可选的,所述输出复位电路包括第七晶体管,所述输出电路包括第八晶体管,所述储能电路包括存储电容;

21、所述第七晶体管的控制极与所述第一控制端电连接,所述第七晶体管的第一极与所述第一电压端电连接,所述第七晶体管的第二极与所述输出端电连接;

22、所述第八晶体管的控制极与所述第二控制端电连接,所述第八晶体管的第一极与所述第二电压端电连接,所述第八晶体管的第二极与所述输出端电连接;

23、所述存储电容的第一端与所述第二控制端电连接,所述存储电容的第二端与所述输出端电连接。

24、本发明实施例还提供了一种信号生成方法,应用于上述的信号生成电路,所述信号生成方法包括:

25、第一控制电路在复位端提供的复位信号和驱动信号输出端提供的驱动信号的控制下,控制第一控制端的电位;所述复位端为相邻上一级驱动信号输出端;

26、第二控制电路根据第一控制端的电位,控制第二控制端的电位;

27、输出复位电路在所述第一控制端的电位的控制下,控制输出端与第一电压端之间连通;

28、输出电路在所述第二控制端的电位的控制下,控制所述输出端与第二电压端之间连通。

29、可选的,所述第一控制电路在复位端提供的复位信号和驱动信号输出端提供的驱动信号的控制下,控制第一控制端的电位步骤包括:

30、所述第一控制电路在所述复位信号的控制下,控制所述复位端与所述第一控制端之间连通,所述第一控制电路在所述驱动信号的控制下,控制所述驱动信号输出端与所述第一控制端之间连通。

31、可选的,所述第二控制电路分别与第三电压端、时钟信号端、第四电压端、第一控制端和第二控制端电连接;所述第二控制电路控制第二控制端的电位步骤包括:

32、所述第二控制电路在所述时钟信号端提供的时钟信号的控制下,控制所述第二控制端与所述第四电压端之间连通,所述第二控制电路在所述第一控制端的电位的控制下,控制所述第二控制端与所述第三电压端之间连通。

33、本发明实施例还提供了一种显示装置,包括上述的信号生成电路。

34、本发明能够改善所述输出端输出的信号的上升沿与所述驱动信号输出端提供的驱动信号的下降沿之间的时序错位现象。

技术特征:

1.一种信号生成电路,其特征在于,包括输出电路、输出复位电路、第一控制电路、第二控制电路和储能电路,其中,

2.如权利要求1所述的信号生成电路,其特征在于,所述第一控制电路用于在所述复位信号的控制下,控制所述复位端与所述第一控制端之间连通,并用于在所述驱动信号的控制下,控制所述驱动信号输出端与所述第一控制端之间连通。

3.如权利要求2所述的信号生成电路,其特征在于,所述第一控制电路包括第一晶体管和第二晶体管;

4.如权利要求1至3中任一权利要求所述的信号生成电路,其特征在于,所述第二控制电路还分别与第三电压端和第四电压端电连接;

5.如权利要求1至3中任一权利要求所述的信号生成电路,其特征在于,所述第二控制电路还分别与第三电压端、时钟信号端和第四电压端电连接,用于在所述时钟信号端提供的时钟信号的控制下,控制所述第二控制端与所述第四电压端之间连通,并在所述第一控制端的电位的控制下,控制所述第二控制端与所述第三电压端之间连通。

6.如权利要求5所述的信号生成电路,其特征在于,所述第二控制电路包括第五晶体管和第六晶体管;

7.如权利要求1至3中任一权利要求所述的信号生成电路,其特征在于,所述输出复位电路包括第七晶体管,所述输出电路包括第八晶体管,所述储能电路包括存储电容;

8.一种信号生成方法,应用于如权利要求1至7中任一权利要求所述的信号生成电路,其特征在于,所述信号生成方法包括:

9.如权利要求8所述的信号生成方法,其特征在于,所述第一控制电路在复位端提供的复位信号和驱动信号输出端提供的驱动信号的控制下,控制第一控制端的电位步骤包括:

10.如权利要求8或9所述的信号生成方法,其特征在于,所述第二控制电路分别与第三电压端、时钟信号端、第四电压端、第一控制端和第二控制端电连接;所述第二控制电路控制第二控制端的电位步骤包括:

11.一种显示装置,其特征在于,包括如权利要求1至7中任一权利要求所述的信号生成电路。

技术总结

本发明提供一种信号生成电路、信号生成方法和显示装置。信号生成电路,包括输出电路、输出复位电路、第一控制电路、第二控制电路和储能电路;输出复位电路在第一控制端的电位的控制下,控制输出端与第一电压端之间连通;输出电路在第二控制端的电位的控制下,控制输出端与第二电压端之间连通;第一控制电路在复位信号和驱动信号的控制下,控制第一控制端的电位;第二控制电路根据第一控制端的电位,控制第二控制端的电位。本发明解决现有技术中输出端输出的信号(该信号可以为发光控制信号)的上升沿与所述驱动信号输出端提供的驱动信号的下降沿之间存在时序错位现象。

技术研发人员:刘伟星,谷朝芸,彭锦涛,王新星,张春芳,徐智强

受保护的技术使用者:京东方科技集团股份有限公司

技术研发日:

技术公布日:2024/4/7

- 还没有人留言评论。精彩留言会获得点赞!