电平转换电路、方法、显示驱动电路和电子设备与流程

本发明涉及显示驱动,尤其涉及一种电平转换电路、方法、显示驱动电路和电子设备。

背景技术:

1、目前,智能终端、平板电脑等电子设备的使用越来越广泛,为了满足用户的各种需求,对电子设备的显示屏的分辨率要求越来越高,显示驱动电路的耗电量也随之提高。显示驱动电路需要一个与输出数量成比例的扫描驱动电路,该电路使用电平转换器电路将低压信号转换为高压信号。因此,随着分辨率的提高,扫描次数也会增加,电平转换器电路的数量也会增加。由于每个电平转换器电路的高压缓冲端子上的晶体管同时切换所造成的短路电流,导致多电平转换器的显示驱动电路功耗增加。

技术实现思路

1、本发明提供一种电平转换电路、方法、显示驱动电路和电子设备,用以解决现有技术中每个电平转换器电路的高压缓冲端子上的晶体管同时切换所造成的短路电流,导致多电平转换器的显示驱动电路功耗增加的缺陷。

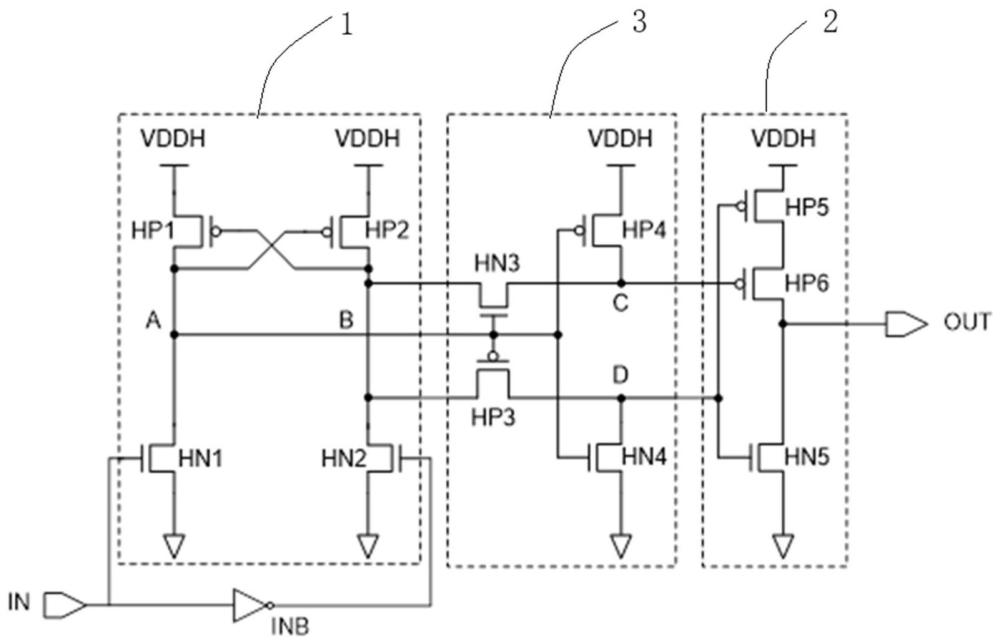

2、本发明提供一种电平转换电路,包括电平转换模块、时序调整模块和电压缓冲模块,所述电压缓冲模块包括依次连接的p型晶体管和n型晶体管;

3、所述电平转换模块,配置为对接收到的输入信号进行电平转换,得到第一转换信号和第二转换信号;

4、所述时序调整模块,配置为根据所述第一转换信号的电压值和所述第二转换信号的电压值之间的关系,得到第一调整信号和第二调整信号,并分别将所述第一调整信号和所述第二调整信号传输至所述电压缓冲模块,以调整所述电压缓冲模块中p型晶体管的切换时间和n型晶体管的切换时间。

5、根据本发明提供的一种电平转换电路,所述时序调整模块包括第三p型晶体管hp3、第四p型晶体管hp4、第三n型晶体管hn3和第四n型晶体管hn4,所述第三p型晶体管hp3的栅极、第四p型晶体管hp4的栅极、第三n型晶体管hn3的栅极和第四n型晶体管hn4的栅极均与所述第一转换信号连接,所述第三p型晶体管hp3的漏极和所述第三n型晶体管hn3的漏极均与所述第二转换信号连接,所述第三n型晶体管hn3的源极和第四p型晶体管hp4的源极配置为输出所述第一调整信号,所述第三p型晶体管hp3的源极和所述第四n型晶体管hn4的源极配置为输出所述第二调整信号。

6、根据本发明提供的一种电平转换电路,所述根据所述第一转换信号的电压值和所述第二转换信号的电压值之间的关系,得到第一调整信号和第二调整信号,包括:

7、根据所述第一转换信号的电压值和所述第二转换信号的电压值之间的关系,调整所述第三p型晶体管hp3、所述第四p型晶体管hp4、所述第三n型晶体管hn3和所述第四n型晶体管hn4的通断状态,得到所述第一调整信号和所述第二调整信号。

8、根据本发明提供的一种电平转换电路,所述电平转换模块包括第一p型晶体管hp1、第二p型晶体管hp2、第一n型晶体管hn1和第二n型晶体管hn2,所述第一p型晶体管hp1的漏极和所述第二p型晶体管hp2的漏极分别连接预设电压端子,所述第一p型晶体管hp1的源极与所述第一n型晶体管hn1的漏极连接,所述第一p型晶体管hp1的栅极分别连接所述第二p型晶体管hp2的源极和所述第二n型晶体管hn2的漏极,连接处配置为输出所述第二转换信号;所述第二p型晶体管hp2的源极与所述第二n型晶体管hn2的漏极连接,所述第二p型晶体管hp2的栅极分别连接所述第一p型晶体管hp1的源极和所述第一n型晶体管hn1的漏极,连接处配置为输出所述第一转换信号;所述第二p型晶体管hp2的栅极和所述第二n型晶体管hn2的栅极配置为接收所述输入信号。

9、根据本发明提供的一种电平转换电路,所述第二p型晶体管hp2的栅极直接与所述输入信号连接,所述第二n型晶体管hn2的栅极经反相器与所述输入信号连接。

10、根据本发明提供的一种电平转换电路,所述电压缓冲模块包括依次连接的第五p型晶体管hp5、第六p型晶体管hp6和第五n型晶体管hn5,所述第五p型晶体管hp5的栅极和所述第五n型晶体管hn5的栅极与所述第二调整信号连接,所述第六p型晶体管hp6的栅极与所述第一调整信号连接,所述第六p型晶体管hp6和第五n型晶体管hn5的公共端配置为连接输出引脚。

11、根据本发明提供的一种电平转换电路,所述电压缓冲模块还配置为根据所述第一调整信号的电压值和所述第二调整信号的电压值之间的关系,调整所述第五p型晶体管hp5、第六p型晶体管hp6和第五n型晶体管hn5的通断状态。

12、本发明还提供一种电平转换方法,包括:

13、对接收到的输入信号进行电平转换,得到第一转换信号和第二转换信号;

14、根据所述第一转换信号的电压值和所述第二转换信号的电压值之间的关系,得到第一调整信号和第二调整信号以调整电压缓冲模块中p型晶体管的切换时间和n型晶体管的切换时间。

15、本发明还提供一种显示驱动电路,包括所述的电平转换电路。

16、本发明还提供一种电子设备,包括显示屏和所述的显示驱动电路,所述显示驱动电路与所述显示屏连接。

17、本发明提供的电平转换电路、方法、显示驱动电路和电子设备,包括电平转换模块、时序调整模块和电压缓冲模块,所述电压缓冲模块包括依次连接的p型晶体管和n型晶体管;所述电平转换模块,配置为对接收到的输入信号进行电平转换,得到第一转换信号和第二转换信号;所述时序调整模块,配置为根据所述第一转换信号的电压值和所述第二转换信号的电压值之间的关系,得到第一调整信号和第二调整信号,并分别将所述第一调整信号和所述第二调整信号传输至所述电压缓冲模块,以调整所述电压缓冲模块中p型晶体管的切换时间和n型晶体管的切换时间。本发明通过时序调整模块对电压缓冲模块中p型晶体管的切换时间和n型晶体管的切换时间进行调整,消除电压转换过程中p型晶体管和n型晶体管同时导通的时间,从而降低了短路电流。

技术特征:

1.一种电平转换电路,其特征在于,包括电平转换模块、时序调整模块和电压缓冲模块,所述电压缓冲模块包括依次连接的p型晶体管和n型晶体管;

2.根据权利要求1所述的电平转换电路,其特征在于,所述时序调整模块包括第三p型晶体管hp3、第四p型晶体管hp4、第三n型晶体管hn3和第四n型晶体管hn4,所述第三p型晶体管hp3的栅极、第四p型晶体管hp4的栅极、第三n型晶体管hn3的栅极和第四n型晶体管hn4的栅极均与所述第一转换信号连接,所述第三p型晶体管hp3的漏极和所述第三n型晶体管hn3的漏极均与所述第二转换信号连接,所述第三n型晶体管hn3的源极和第四p型晶体管hp4的源极配置为输出所述第一调整信号,所述第三p型晶体管hp3的源极和所述第四n型晶体管hn4的源极配置为输出所述第二调整信号。

3.根据权利要求2所述的电平转换电路,其特征在于,所述根据所述第一转换信号的电压值和所述第二转换信号的电压值之间的关系,得到第一调整信号和第二调整信号,包括:

4.根据权利要求1所述的电平转换电路,其特征在于,所述电平转换模块包括第一p型晶体管hp1、第二p型晶体管hp2、第一n型晶体管hn1和第二n型晶体管hn2,所述第一p型晶体管hp1的漏极和所述第二p型晶体管hp2的漏极分别连接预设电压端子,所述第一p型晶体管hp1的源极与所述第一n型晶体管hn1的漏极连接,所述第一p型晶体管hp1的栅极分别连接所述第二p型晶体管hp2的源极和所述第二n型晶体管hn2的漏极,连接处配置为输出所述第二转换信号;所述第二p型晶体管hp2的源极与所述第二n型晶体管hn2的漏极连接,所述第二p型晶体管hp2的栅极分别连接所述第一p型晶体管hp1的源极和所述第一n型晶体管hn1的漏极,连接处配置为输出所述第一转换信号;所述第二p型晶体管hp2的栅极和所述第二n型晶体管hn2的栅极配置为接收所述输入信号。

5.根据权利要求4所述的电平转换电路,其特征在于,所述第二p型晶体管hp2的栅极直接与所述输入信号连接,所述第二n型晶体管hn2的栅极经反相器与所述输入信号连接。

6.根据权利要求1所述的电平转换电路,其特征在于,所述电压缓冲模块包括依次连接的第五p型晶体管hp5、第六p型晶体管hp6和第五n型晶体管hn5,所述第五p型晶体管hp5的栅极和所述第五n型晶体管hn5的栅极与所述第二调整信号连接,所述第六p型晶体管hp6的栅极与所述第一调整信号连接,所述第六p型晶体管hp6和第五n型晶体管hn5的公共端配置为连接输出引脚。

7.根据权利要求6所述的电平转换电路,其特征在于,所述电压缓冲模块还配置为根据所述第一调整信号的电压值和所述第二调整信号的电压值之间的关系,调整所述第五p型晶体管hp5、第六p型晶体管hp6和第五n型晶体管hn5的通断状态。

8.一种电平转换方法,其特征在于,包括:

9.一种显示驱动电路,其特征在于,包括权利要求1-7任一项所述的电平转换电路。

10.一种电子设备,其特征在于,包括显示屏和权利要求9所述的显示驱动电路,所述显示驱动电路与所述显示屏连接。

技术总结

本发明提供一种电平转换电路、方法、显示驱动电路和电子设备,包括电平转换模块、时序调整模块和电压缓冲模块,电压缓冲模块包括依次连接的P型晶体管和N型晶体管;电平转换模块,配置为对接收到的输入信号进行电平转换,得到第一转换信号和第二转换信号;时序调整模块,配置为根据第一转换信号的电压值和第二转换信号的电压值之间的关系,得到第一调整信号和第二调整信号,以调整电压缓冲模块中P型晶体管的切换时间和N型晶体管的切换时间。本发明通过时序调整模块对电压缓冲模块中P型晶体管的切换时间和N型晶体管的切换时间进行调整,消除电压转换过程中P型晶体管和N型晶体管同时导通的时间,从而降低了短路电流。

技术研发人员:金海星

受保护的技术使用者:北京奕斯伟计算技术股份有限公司

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!