像素阵列驱动电路及显示装置的制作方法

本申请涉及显示面板,尤其涉及一种像素阵列驱动电路及显示装置。

背景技术:

1、在显示面板技术领域,由于向液晶面板的像素输出数据的源极驱动电路(sourcedriver)成本较高,因此,为了节约成本,目前常采用在扫描驱动电路(即gate驱动电路)中加倍扫描线的数量,并减少数据线的数量的设计方式,该方式即drd(double ratedriving,双倍率驱动)技术。

2、drd技术可以由同一根数据线驱动两个子像素单元,从而可以减少数据线的数量。该方式可以实现较少的源极驱动集成电路(source ic)来驱动显示面板显示,从而降低成本。

3、现有的drd技术,同一数据线往往与不同颜色的子像素单元连接,即同一列子像素可能连接到不同的数据线上,因此,数据线上的驱动电压必须在一帧图像显示期间逐行变化。当需要实现hsr(hardware super resolution,硬件超分辨率)等需要对某些行与其相邻行的数据混合显示的功能时,造成不同行无法共享数据线上的电压,该类功能无法实现。

技术实现思路

1、鉴于此,为解决上述部分或全部技术问题,本申请实施例提供一种像素阵列驱动电路及显示装置。

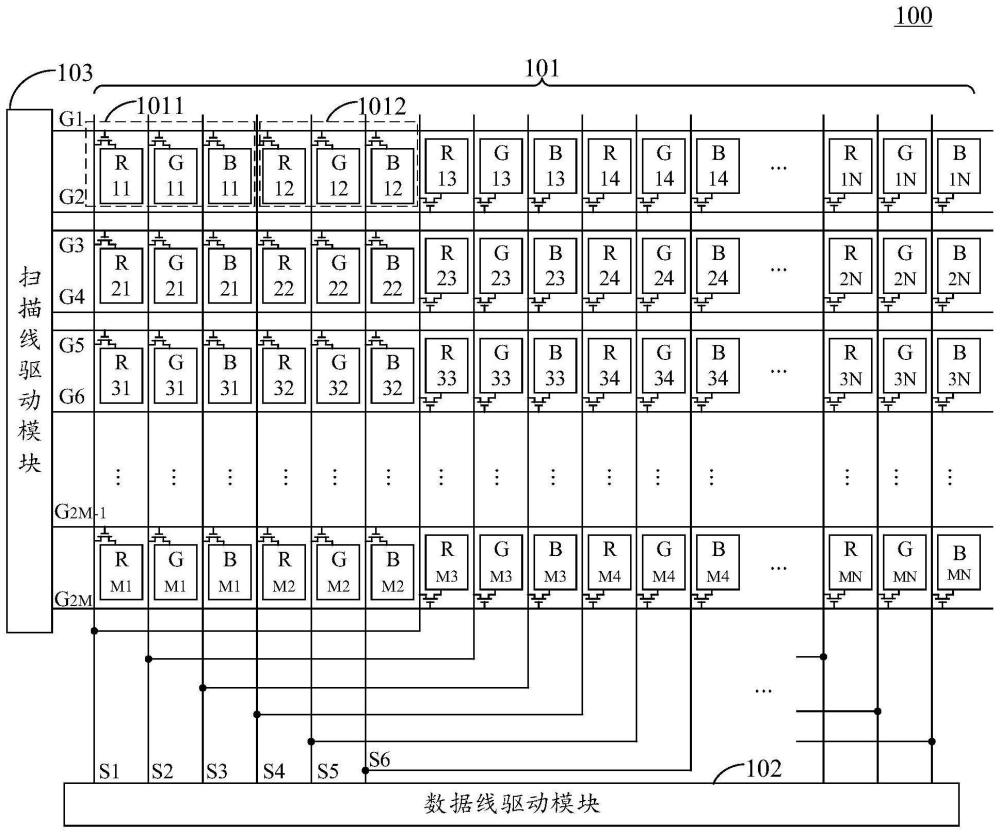

2、第一方面,本申请实施例提供一种像素阵列驱动电路,该电路包括:像素阵列、第一预设数量条数据线、第二预设数量条扫描线、数据线驱动模块和扫描线驱动模块,数据线驱动模块与第一预设数量条数据线连接,扫描线驱动模块与第二预设数量条扫描线连接,像素阵列中的每行对应两条扫描线,像素阵列中的每个像素包括多个子像素;第一预设数量条数据线中的每条数据线分别对应一列子像素,用于向对应的一列子像素输出显示信号;对于像素阵列中的每行,该行包括第三预设数量个像素集合,每个像素集合包括两个像素子集合,且每个像素子集合包括至少一个像素;两个像素子集合中的第一像素子集合和第二像素子集合分别通过该行对应的两条扫描线中的第一扫描线和第二扫描线驱动;第一像素子集合和第二像素子集合各自包括的像素一一对应,且相对应的像素各自包括的同色子像素分别对应的数据线相互连接。

3、在一个可能的实施方式中,该电路还包括时序控制器,时序控制器与扫描线驱动模块连接;像素阵列包括依次交错分布的第一类像素行和第二类像素行;时序控制器用于:响应于触发启动第一扫描模式的操作,控制扫描驱动模块按照对应的时序向第一类像素行对应的扫描线依次输出扫描驱动信号;以及对于像素阵列包括的每个第二类像素行,在该第二类像素行相邻的上一第一类像素行被驱动显示期间,控制扫描驱动模块向该第二类像素行输出扫描驱动信号;在该第二类像素行相邻的下一第一类像素行被驱动显示期间,控制扫描驱动模块向该第二类像素行输出扫描驱动信号。

4、在一个可能的实施方式中,对于像素阵列包括的每个第二类像素行,在该第二类像素行相邻的上一第一类像素行被驱动显示期间,该第二类像素行对应的第一扫描线与上一第一类像素行对应的第一扫描线同时接收扫描驱动信号,该第二类像素行对应的第二扫描线与上一第一类像素行对应的第二扫描线同时接收扫描驱动信号;以及在该第二类像素行相邻的下一第一类像素行被驱动显示期间,该第二类像素行对应的第一扫描线与下一第一类像素行对应的第一扫描线同时接收扫描驱动信号,该第二类像素行对应的第二扫描线与下一第一类像素行对应的第二扫描线同时接收扫描驱动信号。

5、在一个可能的实施方式中,对于像素阵列包括的每个第二类像素行,该第二类像素行对应的第一扫描线接收的扫描驱动信号的驱动时长小于等于上一第一类像素行对应的第一扫描线接收的扫描驱动信号的驱动时长,该第二类像素行对应的第二扫描线接收的扫描驱动信号的驱动时长小于等于上一第一类像素行对应的第二扫描线接收的扫描驱动信号的驱动时长;以及该第二类像素行对应的第一扫描线接收的扫描驱动信号的驱动时长小于等于下一第一类像素行对应的第一扫描线接收的扫描驱动信号的驱动时长,该第二类像素行对应的第二扫描线接收的扫描驱动信号的驱动时长小于等于下一第一类像素行对应的第二扫描线接收的扫描驱动信号的驱动时长。

6、在一个可能的实施方式中,时序控制器进一步用于:接收输入的原始图像数据;从原始图像数据中提取每个第一类像素行对应的待显示数据,并对提取的待显示数据重新排布;基于第一扫描模式命令对应的时序,依次向数据线驱动模块发送每个第一类像素行对应的待显示数据;数据线驱动模块用于:将接收的待显示数据转换为第一预设数量条数据线中的每条数据线分别对应的显示信号,并通过第一预设数量条数据线中的每条数据线输出对应的显示信号。

7、在一个可能的实施方式中,时序控制器用于:响应于触发启动第二扫描模式的操作,控制扫描驱动模块按照对应的时序向第二预设数量条扫描线逐条依次输出扫描驱动信号。

8、在一个可能的实施方式中,时序控制器进一步用于:接收输入的原始图像数据;对原始图像数据进行重新排布,得到第二预设数量条扫描线中的每条扫描线对应的待显示数据;基于第二扫描模式命令对应的时序,依次向数据线驱动模块发送每条扫描线对应的待显示数据;数据线驱动模块用于:将接收的待显示数据转换为第一预设数量条数据线中的每条数据线分别对应的显示信号,并通过第一预设数量条数据线中的每条数据线输出对应的显示信号。

9、在一个可能的实施方式中,在同一图像帧的显示期间,像素阵列中的各列子像素分别对应的参考电压极性相同。

10、在一个可能的实施方式中,第一像素子集合和第二像素子集合分别包括两个像素。

11、第二方面,本申请实施例提供一种显示装置,包括:如上述第一方面描述的像素阵列驱动电路、显示面板、面板框体、电源模块和数据接收模块;像素阵列驱动电路设置在显示面板上,显示面板安装在面板框体上,显示面板的供电端与电源模块连接,显示面板的信号接收端与数据接收模块连接。

12、本申请实施例提供的像素阵列驱动电路及显示装置,通过将像素阵列中的每行像素划分为多个像素集合,每个像素集合又划分为两个像素子集合,其中的第一像素子集合和第二像素子集合分别通过该行对应的两条扫描线中的第一扫描线和第二扫描线驱动,第一像素子集合和第二像素子集合中相对应的像素各自包括的同色子像素分别对应的数据线相互连接,从而实现了同列子像素由一条数据线驱动,且同一条数据线连接的两列子像素的颜色相同,该电路结构可以使某一行像素与相邻像素共享数据,从而有助于实现hsr等功能。此外,由于同一数据线连接的子像素的颜色相同,可以使数据显示的时序控制和数据排布过程更加简便,从而有助于提高显示的效率。

技术特征:

1.一种像素阵列驱动电路,其特征在于,所述电路包括:像素阵列、第一预设数量条数据线、第二预设数量条扫描线、数据线驱动模块和扫描线驱动模块,所述数据线驱动模块与所述第一预设数量条数据线连接,所述扫描线驱动模块与所述第二预设数量条扫描线连接,所述像素阵列中的每行对应两条扫描线,所述像素阵列中的每个像素包括多个子像素;

2.根据权利要求1所述的电路,其特征在于,所述电路还包括时序控制器,所述时序控制器与所述扫描线驱动模块连接;

3.根据权利要求2所述的电路,其特征在于,对于所述像素阵列包括的每个第二类像素行,在该第二类像素行相邻的上一第一类像素行被驱动显示期间,该第二类像素行对应的第一扫描线与所述上一第一类像素行对应的第一扫描线同时接收扫描驱动信号,该第二类像素行对应的第二扫描线与所述上一第一类像素行对应的第二扫描线同时接收扫描驱动信号;以及

4.根据权利要求3所述的电路,其特征在于,对于所述像素阵列包括的每个第二类像素行,该第二类像素行对应的第一扫描线接收的扫描驱动信号的驱动时长小于等于所述上一第一类像素行对应的第一扫描线接收的扫描驱动信号的驱动时长,该第二类像素行对应的第二扫描线接收的扫描驱动信号的驱动时长小于等于所述上一第一类像素行对应的第二扫描线接收的扫描驱动信号的驱动时长;以及

5.根据权利要求2所述的电路,其特征在于,所述时序控制器进一步用于:

6.根据权利要求2所述的电路,其特征在于,所述时序控制器用于:

7.根据权利要求6所述的电路,其特征在于,所述时序控制器进一步用于:

8.根据权利要求1-7任一项所述的电路,其特征在于,在同一图像帧的显示期间,所述像素阵列中的各列子像素分别对应的参考电压极性相同。

9.根据权利要求1-7任一项所述的电路,其特征在于,所述第一像素子集合和所述第二像素子集合分别包括两个像素。

10.一种显示装置,其特征在于,包括:如权利要求1-9任一项所述的像素阵列驱动电路、显示面板、面板框体、电源模块和数据接收模块;

技术总结

本申请实施例涉及一种像素阵列驱动电路及显示装置,该电路包括:像素阵列、第一预设数量条数据线、第二预设数量条扫描线、数据线驱动模块和扫描线驱动模块,像素阵列中的每行对应两条扫描线,像素阵列中的每个像素包括多个子像素;第一预设数量条数据线中的每条数据线分别对应一列子像素,每行包括第三预设数量个像素集合,每个像素集合包括两个像素子集合,第一像素子集合和第二像素子集合各自包括的像素一一对应,且相对应的像素各自包括的同色子像素分别对应的数据线相互连接。本申请实施例有助于在时序DRD显示的基础上,实现HSR等功能,还可以使数据显示的时序控制和数据排布过程更加简便,从而有助于提高显示的效率。

技术研发人员:杨文武,李建雷,纪飞林,陈伟,叶利丹

受保护的技术使用者:惠科股份有限公司

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!