半导体组件及其切割方法、滤波器及电子设备与流程

1.本发明的实施例涉及半导体领域,尤其涉及一种半导体组件、一种半导体组件的切割方法,一种具有该半导体组件的滤波器,以及一种具有该滤波器的电子设备。

背景技术:

2.电子器件作为电子设备的基本元素,已经被广泛应用,其应用范围包括移动电话、汽车、家电设备等。此外,未来即将改变世界的人工智能、物联网、5g通讯等技术仍然需要依靠电子器件作为基础。

3.电子器件根据不同工作原理可以发挥不同的特性与优势,在所有电子器件中,利用压电效应(或逆压电效应)工作的器件是其中很重要一类,压电器件有着非常广泛的应用情景。薄膜体声波谐振器(film bulk acoustic resonator,简称fbar,又称为体声波谐振器,也称baw)作为压电器件的重要成员正在通信领域发挥着重要作用,特别是fbar滤波器在射频滤波器领域市场占有份额越来越大,fbar具有尺寸小、谐振频率高、品质因数高、功率容量大、滚降效应好等优良特性,其滤波器正在逐步取代传统的声表面波(saw)滤波器和陶瓷滤波器,在无线通信射频领域发挥巨大作用,其高灵敏度的优势也能应用到生物、物理、医学等传感领域。

4.对于薄膜体声波谐振器等mems器件,其通常设置在两个基底之间,两个基底通过密封键合层键合,一个基底可以为设置mems器件的功能基底,另一个基底可以为封装基底,不过也可以设置mems器件。对于分离的mems器件及其封装结构,可以将其称为一颗die。

5.在mems器件的制作过程中,两片晶圆彼此对置,晶圆之间利用密封键合层键合连接,两片晶圆之间基于密封键合层的分隔,从而在两片晶圆之间形成很多颗die。

6.图1为现有技术中在两颗die之间划片从而将两颗die切割分离的结构示意图。图1中,201和202为晶圆或基底,101为划片用对准标记,b为对准标记101之间的水平距离,102为下密封结构或下密封键合层,104为导电通孔,105为焊盘,109为上密封结构或上密封键合层,键合层109与键合层102彼此键合而形成密封结构。如图1所示,键合层102之间在水平方向上的距离为a。

7.由于两片晶圆键合时存在偏移,对准标记101无法做到与密封结构完全对齐。为了确保划片时不伤及密封结构,下密封圈或下密封键合层102之间的距离a要大于划片标记101之间的距离b,通常a与b的差距在20um左右。

8.因为划片属于物理切割,划片刀的轨迹也无法保障没有偏差,所以划片标记间的距离b要大于划片刀的厚度(或者激光的宽度),通常要大20um左右。

9.因此,在采用图1所示的切割方案时,需要设置冗余宽度,这会浪费晶圆的面积。

10.图2为现有技术中采用刻蚀方法来执行两颗die之间的切割的结构示意图。如图2所示,如果通过刻蚀的方法刻出分隔通道106,则可以在保证精度的情况下将下密封结构102之间的距离a大幅度缩小,但是如果在焊盘形成工艺之前就将die分隔,这导致后续电镀无法进行,或者在磨片减薄工艺进行时因单颗die可承受外力不足而导致键合失效。

11.因此,现有技术中存在改进die之间的切割方法的需要。

技术实现要素:

12.为了克服现有技术中的问题的至少一个方面,提出本发明。

13.根据本发明的实施例的一个方面,提出了一种半导体组件,包括:

14.第一基底和第二基底;

15.密封层,设置在第一基底的下侧与第二基底的上侧之间;

16.至少一个mems器件,

17.其中:

18.第一基底、第二基底以及密封层限定或围合至少一个容纳空间,所述mems器件设置在对应的容纳空间内;

19.所述第一基底的上侧并未设置划片用对准标记。

20.本发明的实施例还涉及一种半导体组件的切割方法,包括:

21.步骤1:提供第一基底、第二基底、密封层和mems器件,密封层设置在第一基底的下侧与第二基底的上侧之间,第一基底、第二基底以及密封层限定或围合容纳空间,mems器件设置在对应的容纳空间内,其中:密封层包括设置在第一基底的第一密封层与设置在第二基底的第二密封层,第一密封层适于与第二密封层密封连接;

22.步骤2:移除第一基底的周边区域的预定部分以露出与所述预定部分对应的第二密封层;

23.步骤3:以在所述预定部分对应的所述第二密封层为对准标记执行切割。

24.本发明的实施例还涉及一种滤波器,包括上述的半导体组件。

25.本发明的实施例也涉及一种电子设备,包括上述的滤波器或者上述的半导体组件。

附图说明

26.以下描述与附图可以更好地帮助理解本发明所公布的各种实施例中的这些和其他特点、优点,图中相同的附图标记始终表示相同的部件,其中:

27.图1为现有技术中在两颗die之间划片从而将两颗die切割分离的结构示意图;

28.图2为现有技术中采用刻蚀方法来执行两颗die之间的切割的结构示意图;

29.图3a和图3b为示出根据本发明的一个示例性实施例的两颗die之间的切割方法的结构示意图,其中图3a中,上基底还未执行切割,图3b中,上基底周围预定部分已经执行切割;

30.图3c为图3b中的晶圆结构的示意性俯视图,其中中间的圆圈部分代表上侧的晶圆;

31.图3d为图3c中的晶圆结构的边缘部分的局部放大示意图;

32.图3e为根据本发明的另一个示例性实施例的晶圆结构的边缘部分的局部放大示意图;

33.图4为根据本发明的一个示例性实施例的未完成切割前的两片晶圆的结构示意图,其中的省略号表示较多的die没有示出;

34.图5a-图5f为根据本发明的一个示例性实施例的显示制造图3b所示结构的步骤的示意性结构图;

35.图6为刻蚀表面的实体图;

36.图7为图6中的刻蚀表面的放大图。

具体实施方式

37.下面通过实施例,并结合附图,对本发明的技术方案作进一步具体的说明。在说明书中,相同或相似的附图标号指示相同或相似的部件。下述参照附图对本发明实施方式的说明旨在对本发明的总体发明构思进行解释,而不应当理解为对本发明的一种限制。

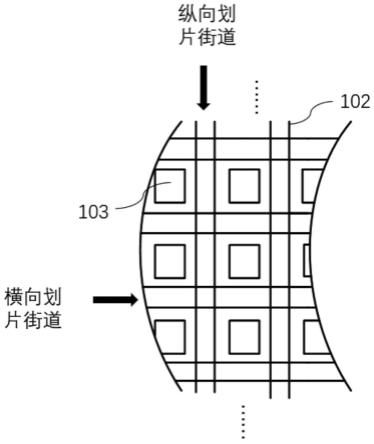

38.图3a和图3b为示出根据本发明的一个示例性实施例的两颗die之间的切割方法的结构示意图,其中图3a中,上基底还未执行切割,图3b中,上基底的周边预定部分已经执行切割。图3c为图3b中的晶圆结构的示意性俯视图,其中中间的圆圈部分代表上侧的晶圆。

39.图3a和图3b中,201和202为晶圆或基底,102为下密封结构或下密封键合层,104为导电通孔,105为焊盘,109为上密封结构或上密封键合层,键合层109与键合层102彼此键合而形成密封结构。

40.在版图设计时,如图3a所示,对基底202的周边宽度b(一般为1mm-10mm,进一步的,为1mm-3.5mm)的范围内取消基底202上的密封键合层109,从而使得在图3a中b对应区域的两个基底为非键合状态。

41.接着,如图3b所示,利用切割方法移除基底202的b对应区域,从而露出在基底201上侧的密封键合层102。如此,如图3c所示,可以露出基底201的外边缘周边区域的密封键合层102。

42.图3d为图3c中的晶圆结构的边缘部分的局部放大示意图。从图3d中可以看到,密封键合层102(细实线)纵横交错,限定了围合mems器件103的矩形区域。细实线或密封键合层102之间构成切割通道,在图3d中为横向划片街道和纵向划片街道。

43.在图3c所示结构的基础上,以切割刀具沿图3d中所示的划片街道,可以完成切割,从而形成独立的各个die。

44.这种划片方法的优点是规避了后设定的划片标记101与密封键合层102之间的对准问题,从而可以无需为了这个对准而额外增加密封圈距离(通常为20um),从而提升单片晶圆的die产出数量。

45.图3e为根据本发明的另一个示例性实施例的晶圆结构的边缘部分的局部放大示意图。图3e与图3d的不同在于,在图3e中,第一基底202的边缘部分(在图3e中对应于部分107)未被移除,而是在距离第一基底202的边缘一个预定距离(例如不大于3mm,该距离只要保证可以在执行切割时露出的密封键合层102可以起到对准作用即可)处移除了一部分的第一基底202从而露出密封键合层102。

46.图4为根据本发明的一个示例性实施例的未完成切割前的两片晶圆的结构示意图,其中的省略号表示较多的die没有示出。图4中所示结构与图3b所示结构相似。

47.除了参照图3a和图3b所述的切割方法,还可以采用其他的露出密封键合层102的方法。以下参照图5a-图5f进行示例性说明。图5a-图5f为根据本发明的示例性实施例的显示制造图3b所示结构的步骤的示意性结构图。

48.如图5a所示,提供基底202。

49.如图5b所示,在基底202的一侧刻蚀出通孔104,形成密封键合层109,以及在基底202的边缘区域形成缺口110。为节约成本,通孔104可以不贯穿基底202,通孔104与缺口110同时形成。

50.如图5c所示,提供基底201,在其一侧设置mems器件103以及密封键合层102。

51.如图5d所示,将图5c中的基底201与图5b中的基底202彼此键合,此时,密封键合层102和密封键合层109彼此键合连接。

52.如图5e所示,可以通过研磨工艺等从图5e中基底202的上侧移除预定厚度的基底材料,以将图5d中的与缺口110对应的部分移除,从而露出基底201上的密封键合层102。

53.如图5f所示,制作金属焊盘105。

54.之后的切割操作与图3b中所示结构相同。

55.基于以上,采用本发明的方法,可以消除对图1中的划片对准标记101,所以,本发明提出了如下一种半导体组件,其在现有技术中设置划片对准标记101的基底一侧并未设置划片用对准标记。

56.鉴于在现有技术中,划片对准标记101往往与金属焊盘105同层且间隔开布置,所以,在本发明提出的半导体组件中,在导电焊盘的外边缘与其所在的基底的端面之间并未设置与导电焊盘同层布置且间隔开的划片对准标记。

57.在本发明中,可以采用例如图3a和图3b所示的切割方案,而不采用现有技术中的图2所示的刻蚀方案,所以,基于例如图3a和图3b所示的切割方案所获得的半导体组件的基底的端面是切割形成而非刻蚀形成,即在本发明中,基底202的端面并不具有基于刻蚀而形成的纹路。图6为刻蚀表面的实体图,图7为图6中的刻蚀表面的放大图。如图7所示,刻蚀表面具有孔隙纹路。基底202的端面并不具有基于刻蚀而形成的纹路可以表示该端面不具有孔隙纹路。

58.在本发明中的上述示例中,以密封键合层102和109均为金属键合层为例进行说明,但是,用于形成密封的键合层也可以不是金属键合层。此外,在mems器件封装结构中,在用于金属键合的金属键合层的外侧,还设置有专门的密封层以起到密封作用,此时,本发明的切割方法是以在另外的基本上露出的该专门的密封层作为切割引导基准。

59.在本发明的权利要求中,对于第一基底和第二基底,并未明确两者的位置关系,可以第一基底在第二基底上方,也可以第二基底在第一基底上方。对于在现有技术中会设置划片对准标记的基底,基底上侧就是会设置划片对准标记的一个基底的一侧。相应的,在本发明权利要求中,在现有技术中需要设置划片对准标记但是采用本发明的切割方案而不设置划片对准标记的第一基底的一侧就是第一基底的上侧,而第二基底的上侧就是与该第一基底的下侧相对的一侧。

60.如本领域技术人员能够理解的,根据本发明的半导体组件可以用于形成滤波器或电子设备。这里的电子设备,包括但不限于射频前端、滤波放大模块等中间产品,以及手机、wifi、无人机等终端产品。

61.需要指出的是,在本发明中,各个数值范围,除了明确指出不包含端点值之外,除了可以为端点值,还可以为各个数值范围的中值,这些均在本发明的保护范围之内。

62.基于以上,本发明提出了如下技术方案:

63.1、一种半导体组件,包括:

64.第一基底和第二基底;

65.密封层,设置在第一基底的下侧与第二基底的上侧之间;

66.至少一个mems器件,

67.其中:

68.第一基底、第二基底以及密封层限定或围合至少一个容纳空间,所述mems器件设置在对应的容纳空间内;

69.所述第一基底的上侧并未设置划片用对准标记。

70.2、根据1所述的组件,其中:

71.所述组件包括穿过所述第一基底的导电通孔;

72.所述第一基底的上侧设置有导电焊盘,所述导电焊盘与所述导电通孔相连通;

73.在所述第一基底的上侧,在所述导电焊盘的外边缘与所述第一基底的端面之间并未设置所述对准标记。

74.3、根据2所述的组件,其中:

75.所述密封层为金属键合层,所述导电通孔与所述键合层在第一基底的厚度方向上对齐且电连接。

76.4、根据2所述的组件,其中:

77.在所述第一基底的上侧,在所述导电焊盘的外边缘与所述第一基底的端面之间并未设置与所述导电焊盘同层布置且间隔开的划片对准标记。

78.5、根据1-4中任一项所述的组件,其中:

79.所述第一基底的端面不具有基于刻蚀形成的纹路。

80.6、一种半导体组件的切割方法,包括:

81.步骤1:提供第一基底、第二基底、密封层和mems器件,密封层设置在第一基底的下侧与第二基底的上侧之间,第一基底、第二基底以及密封层限定或围合容纳空间,mems器件设置在对应的容纳空间内,其中:密封层包括设置在第一基底的第一密封层与设置在第二基底的第二密封层,第一密封层适于与第二密封层密封连接;

82.步骤2:移除第一基底的周边区域的预定部分以露出与所述预定部分对应的第二密封层;

83.步骤3:以在所述预定部分对应的所述第二密封层为对准标记执行切割。

84.7、根据6所述的方法,其中:

85.移除第一基底的周边区域的预定部分包括移除所述第一基底的外边缘所在部分。

86.8、根据7所述的方法,其中:

87.以在与第一基底的厚度方向平行的方向上切割或刻蚀所述第一基底而移除所述预定部分。

88.9、根据8所述的方法,其中:

89.在步骤1中,在与所述预定部分对应的区域,在所述第一基底的下侧不设置第一密封层。

90.10、根据7所述的方法,其中:

91.在步骤1中,第一基底的下侧在所述预定部分为凹陷部分,所述第一基底在所述凹

陷部分对应的部分具有第一厚度;

92.在步骤2中,从第一基底的上侧移除预定厚度的基底材料而露出与所述预定部分对应的第二密封层,所述预定厚度不小于第一厚度。

93.11、根据6所述的方法,其中:

94.第一基底的周边区域的预定部分与所述第一基底的外边缘在水平方向上间隔开一个距离。

95.12、根据11所述的方法,其中:

96.所述一个距离不大于3mm。

97.13、根据6所述的方法,其中:

98.所述预定部分的宽度在1mm-10mm的范围内。

99.14、根据13所述的方法,其中:

100.所述预定部分的宽度在1mm-3.5mm的范围内。

101.15、一种滤波器,包括根据1-5中任一项所述的半导体组件,其中所述mems器件包括谐振器。

102.16、一种电子设备,包括根据15所述的滤波器或者根据1-5中任一项所述的半导体组件。

103.尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行变化,本发明的范围由所附权利要求及其等同物限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1