静电耐压试验装置和静电耐压试验方法与流程

1.本公开涉及静电耐压试验装置和静电耐压试验方法。

背景技术:

2.伴随着集成电路和分立器件等半导体器件的微细化,由于静电放电而发生故障的风险变高。在采用半导体器件时,要求静电管理,该静电管理用于掌握针对静电放电具有何种程度的耐压,并与该耐压配合地预防故障。因此,针对全部的半导体器件进行静电耐压试验(例如参照日本特开2000-206177号公报(专利文献1))。

3.现有技术文献

4.专利文献

5.专利文献1:日本特开2000-206177号公报

技术实现要素:

6.发明要解决的问题

7.在以往的静电耐压试验中,针对半导体器件的1个端子产生静电放电。但是,即便针对1个端子产生静电放电,半导体器件有时也不会因在制造现场中产生的电压而发生故障。

8.在向设置于安装有半导体器件的基板的多个引脚插入连接器的结构中,多个引脚的端子分别同时与半导体器件的多个端子电接触。在这样的结构中,经由多个引脚在半导体器件中产生静电放电,因此,与经由1个引脚在半导体器件中产生静电放电的结构相比,能够在短时间内向半导体器件流入大电流。其结果是,使半导体器件产生故障的可能性变高。因此,在使1个端子产生静电放电的以往的静电耐压试验中,产生无法准确地在制造现场测定半导体器件的耐压的情况。

9.本公开是为了解决这样的问题点而完成的,本公开的目的在于,提供一种能够准确地测定安装基板上的半导体器件的静电耐压的静电耐压试验装置和静电耐压试验方法。

10.用于解决问题的手段

11.在本公开的某个方案中,静电耐压试验装置测定安装基板上的半导体器件的静电耐压。半导体器件具有多个引脚。在安装基板上设置有与多个引脚分别电连接的多个端子和导体图案。静电耐压试验装置具备搭载安装基板的金属板、用于向金属板施加电压的电源、配置在金属板与安装基板之间的绝缘体、连接在多个端子与接地布线之间的开关电路、以及控制开关电路的控制部。开关电路包括多个第1开关,该多个第1开关构成为与多个端子分别对应地设置,并将对应的端子与接地布线连接。控制部在将蓄积于导体图案的电荷经由半导体器件向接地布线放电时,将从多个第1开关中选择出的至少1个第1开关接通。

12.在本公开的另一方案中,静电耐压试验方法是用于测定安装基板上的半导体器件的静电耐压的静电耐压试验方法。半导体器件具有多个引脚。在安装基板上,设置有与多个引脚分别电连接的多个端子和导体图案。静电耐压试验方法具备使半导体器件产生静电放

电的步骤。使半导体器件产生静电放电的步骤包括以下步骤:通过向隔着绝缘体而与导体图案对置配置的金属板施加电压,使导体图案带电;以及将蓄积于导体图案的电荷经由半导体器件向接地布线放电。放电的步骤包括以下步骤:将从多个第1开关中选择出的至少1个第1开关接通,该多个第1开关构成为与多个端子分别对应设置,并将对应的端子与接地布线连接。

13.发明的效果

14.根据本公开,可提供能够准确地测定制造现场中的半导体器件的静电耐压的静电耐压试验装置和静电耐压试验方法。

附图说明

15.图1是将半导体装置的一部分放大后的俯视图。

16.图2是半导体装置的剖视图。

17.图3是概要地示出实施方式1的静电耐压试验装置的结构例的图。

18.图4是示出图3所示的半导体装置、开关电路以及电力线的布线结构的图。

19.图5是用于说明使导体图案带电的工序的图。

20.图6是用于说明使导体图案的电荷放电的工序的图。

21.图7是用于说明对金属板进行除电的工序的图。

22.图8是示出用于测定半导体器件的电特性的测定装置的结构例的图。

23.图9是用于说明实施方式1的静电耐压试验方法的处理流程的流程图。

24.图10是概要地示出实施方式2的静电耐压试验装置的结构例的图。

25.图11是用于说明实施方式2的静电耐压试验方法的处理流程的流程图。

26.图12是用于说明测定半导体器件的电特性的工序的图。

27.图13是用于说明产生静电放电的工序的图。

具体实施方式

28.以下,参照附图对本公开的实施方式详细进行说明。另外,以下,针对图中的相同或相当的部分标注相同的标号,原则上不再重复其说明。

29.实施方式1

30.(半导体装置的结构例)

31.首先,使用图1和图2,对成为实施方式1的静电耐压试验方法的试验对象的半导体装置的结构例进行说明。图1是将半导体装置20的一部分放大后的俯视图。图2是半导体装置20的剖视图。另外,在图2中,示出半导体装置20安装于电子设备的情形。

32.如图1和图2所示,半导体装置20具有安装基板8和半导体器件10。安装基板8包含导体图案8a和层叠在导体图案8a上的绝缘层8b。导体图案8a在俯视下占据安装基板8的大多数面积,构成gnd图案。

33.半导体器件10安装于安装基板8的表面。半导体器件10具有至少1个半导体元件10e、密封树脂10f、以及多个引脚。半导体元件10e例如由igbt(insulated gate bipolar transistor)、mos-fet(metal-oxide-semiconductor field effect transistor)、二极管等构成。

34.多个引脚通过未图示的导电线而与至少1个半导体元件10e电连接。密封树脂10f将至少1个半导体元件10e和多个引脚的一部分密封。由此,多个引脚的一部分从密封树脂10f露出。多个引脚包括供电用或信号输入用的引脚10a~10c、以及接地电压(gnd)供给用的gnd引脚10d。

35.在安装基板8的表面上,形成有供电用或信号输入用的布线12a~12c、gnd布线12d、以及多个端子9。多个端子9包含供电用或信号输入用的端子9a~9c、以及gnd端子9d。

36.布线12a~12c与导体图案8a电绝缘。gnd布线12d经由配置在绝缘层8b内的gnd端子9d而与导体图案8a电连接。布线12a~12c的第1端部与半导体器件10的引脚10a~10c分别连接。布线12a~12c的第2端部与端子9a~9c分别连接。gnd布线12d的第1端部与半导体器件10的gnd引脚10d连接。gnd布线12d的第2端部与gnd端子9d连接。

37.在电子设备的制造工序中,半导体装置20收容在由树脂等形成的壳体13的内部。通过向半导体装置20的端子9a~9c插入连接器14,端子9a~9c经由连接器14而与其他的设备15电连接。

38.(静电放电)

39.接着,详细说明在电子设备的制造现场中能够产生的静电放电。

40.在电子设备的制造现场中,通过收容半导体装置20的壳体13相对于gnd带电,设置在安装基板8内的导体图案8a(gnd图案)有时带电。另外,如图2所示,导体图案8a经由gnd端子9d和gnd布线12d而与半导体器件10的gnd引脚10d电连接。

41.在制造工序中,假定在导体图案8a带电的状态下将半导体器件10的引脚10a经由连接器14而与其他的设备15电连接的情况。

42.在该情况下,半导体器件10的引脚10a与安装基板8上的端子9a电连接,因此,在向端子9a插入了连接器14时,蓄积于导体图案8a的电荷从gnd引脚10d依次经由半导体元件10e和引脚10a、端子9a、连接器14以及设备15内部的布线而流入gnd。即,在半导体装置20中产生与蓄积于导体图案8a的电荷量相应的静电放电,因此,半导体器件10可能发生故障。

43.这里,在假定了安装基板的静电放电的模型中,具有基板带电事件(charge board event:cbe)。cbe是指,通过连接器向带电的安装基板的插入或安装基板与金属工具的接触等而使蓄积于安装基板的电荷放电的模型。通常,安装基板与半导体器件相比,大多具有几百倍以上的面积,蓄积于安装基板的电荷量与该面积成比例地变大。

44.在安装基板中,为了应对噪声,广泛采用了占据安装基板的大多数面积的导电性的gnd图案。表示分别蓄积于半导体器件和安装基板的电荷的电容的静电电容c是基于c=ε(s/d)的关系式而决定的。其中,ε是相对介电常数,s是对置电极的面积,d是对置电极间的距离。如上所述,gnd图案的面积s比半导体器件大,因此,安装基板的静电电容c比半导体器件的静电电容c大。

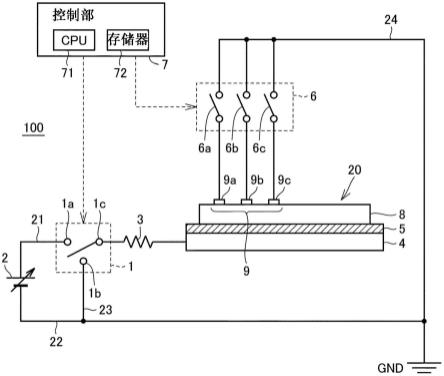

45.分别蓄积于半导体器件和安装基板的电荷量q是基于q=cv的关系式而决定的。其中,v是在对置电极之间施加的电压。如上所述,安装基板的静电电容c比半导体器件大,因此,在所施加的电压v彼此相等的情况下,安装基板与半导体器件相比,蓄积更多的电荷量。

46.静电放电的能量w是基于w=q

×

v/2的关系式而决定的。在半导体器件和安装基板的施加电压v彼此相等的情况下,安装基板与半导体器件相比,蓄积的电荷量q变大,因此,静电放电的能量w也变大。因此,在图1和图2所示的半导体装置20中,虽然在半导体器件10

单体中不产生由静电放电引起的故障,但是通过将半导体器件10安装于安装基板8,可能在半导体器件10中产生由静电放电引起的故障。因此,需要在将半导体器件10安装于安装基板8的状态下进行依照cbe的静电耐压试验,对电子设备的制造工序中的半导体器件10的静电耐压进行测定。

47.(静电耐压试验)

48.接着,对实施方式1的静电耐压试验进行说明。首先,使用图3对实施方式1的静电耐压试验装置的结构例进行说明。

49.(1)静电耐压试验装置的结构例

50.图3是概要地示出实施方式1的静电耐压试验装置的结构例的图。

51.如图3所示,实施方式1的静电耐压试验装置100是用于测定图1和图2所示的半导体装置20的静电耐压的装置。静电耐压试验装置100具有开关1、直流电源2、电阻3、金属板4、绝缘体5、开关电路6、控制部7以及电力线21~24。

52.直流电源2连接在高电压侧的电力线21与低电压侧的电力线22之间。电力线22由接地布线构成。直流电源2构成为能够切换向电力线21输出的电压的大小。

53.电阻3连接在电力线21与金属板4之间。开关1连接在电力线21、23与电阻3之间。对于开关1,能够应用半导体开关或机械式开关。关于半导体开关,代表性的是igbt或mosfet等半导体开关元件。机械式开关例如是继电器等开闭器。开关1对应于“第2开关”的一实施例。

54.开关1构成为能够按照来自控制部7的控制信号,将电阻3与电力线21及电力线23中的任意一方电连接。作为一例,开关1具有3个触点1a~1c。触点1a、1b是固定触点,触点1c是选择性地与触点1a、1b连接的可动触点。触点1a与电力线21的第1端子连接,触点1b与电力线23的第1端子连接,触点1c与电阻3的第1端子连接。电力线21的第2端子与直流电源2的正极连接,电力线23的第2端子与电力线22连接,电阻3的第2端子与金属板4连接。

55.通过将开关1的触点1c与触点1a连接而将电力线21与电阻3电连接,因此,能够将从直流电源2向电力线21供给的电压经由电阻3施加到金属板4。另一方面,通过将开关1的触点1c与触点1b连接而将电力线23与电阻3电连接,因此,能够将蓄积于金属板4的电荷经由电力线23朝向电力线22释放。

56.在以下的说明中,把将触点1c与触点1a连接称为“将触点1a接通(导通)”,把将触点1c与触点1b连接称为“将触点1b接通”。另外,在开关1中,在触点1a为接通时,触点1b被断开(非导通),在触点1b为接通时,触点1a被断开。

57.绝缘体5具有平板形状,且配置在金属板4上。半导体装置20配置在绝缘体5上。绝缘体5确保金属板4与导体图案8a的电绝缘。通过在金属板4与导体图案8a之间设置绝缘体5,能够模拟将金属板4与导体图案8a设为电极的电容器。因此,在向金属板4施加了电压时,能够在金属板4中蓄积电荷。另外,绝缘体5的规格需要根据试验电压来决定。这是因为,在使用了绝缘耐压比试验电压低的绝缘体5的情况下,绝缘体5在电压施加中可能发生绝缘破坏。

58.开关电路6连接在半导体装置20的端子9与电力线24之间。电力线24由接地布线构成。开关电路6具有多个开关6a~6c。多个开关6a~6c对应于“多个第1开关”的一实施例。

59.对于开关6a~6c,例如能够应用水银继电器。水银继电器的触点部分被水银覆盖。

在其他的机械式继电器中,在开关的打开时瞬时地发生反复进行通断的跳动。由于水银具有高粘性,因此,在水银继电器中不发生跳动。因此,能够进行再现性高的静电耐压试验。

60.开关6a~6c用于再现在将图2所示的半导体器件10的引脚10a~10c与其他的设备15经由连接器14而电连接时产生的静电放电。具体而言,开关6a连接在端子9a与电力线24之间。开关6b连接在端子9b与电力线24之间。开关6c连接在端子9c与电力线24之间。开关6a~6c分别构成为通过按照来自控制部7的控制信号而接通(导通)/断开(非导通),从而将对应的端子9与电力线24电连接/电切断。

61.通过将开关6a~6c接通,再现了图2所示的半导体器件10的引脚10a~10c与连接器14的电连接,因此,能够模拟上述的基于cbe(基板带电事件)的静电放电。另外,在图3的例子中,将开关电路6所包含的开关的数量设为3,但开关的数量为多个即可。

62.控制部7对开关1和开关电路6的接通断开进行控制。控制部7例如能够由微型计算机等构成。具体而言,控制部7具备cpu(central processing unit:中央处理单元)71、以及存储程序和数据的存储器72,通过基于cpu71执行该程序而实现的软件处理,能够执行后述的控制动作。或者,关于该控制动作的一部分或全部,也能够代替软件处理,通过使用了内置的专用电子电路等的硬件处理来实现。

63.存储器72包括rom(read only memory:只读存储器)和ram(random access memory:随机存取存储器)。rom能够存储由cpu71执行的程序。ram能够暂时存储在cpu71执行程序过程中利用的数据,能够作为被用作作业区域的暂时的数据存储器发挥功能。

64.控制部7能够相互独立地控制开关电路6所包含的多个开关6a~6c的接通断开。因此,控制部7能够将多个开关6a~6c中的任意1个开关接通。或者,控制部7能够将2个以上的开关同时接通。即,控制部7能够将多个开关6a~6c中的至少1个接通。

65.图4是示出图3所示的半导体装置20、开关电路6以及电力线24的布线结构的图。如图4所示,静电耐压试验装置100还具有多个探针11a~11c。以下,有时将探针11a~11c统一简称为“探针11”。

66.对于探针11,例如能够应用弹簧探针。弹簧探针具有内置弹簧的可动部,当对前端施加压力时,可动部通过弹簧而滑动。利用该滑动,能够确保探针11与端子9的接触。

67.多个探针11a~11c的第1端子与多个开关6a~6c的第1端子分别连接。多个开关6a~6c的第2端子与电力线24连接。多个探针11a~11c的第2端子与半导体装置20的多个端子9a~9c分别连接。另外,在图4的例子中,将探针11的数量设为3,但探针11的数量与开关电路6的开关的数量相同即可。

68.(2)静电耐压试验方法

69.接着,对实施方式1的静电耐压试验方法进行说明。

70.实施方式1的静电耐压试验方法构成为,通过在图3所示的静电耐压试验装置100中对开关1和开关电路6的接通断开进行控制,从而执行安装基板8的导体图案8a的带电、以及蓄积于导体图案8a的电荷的放电。由此,实现模拟了基于cbe(基板带电事件)的静电放电的静电耐压试验。

71.(2-1)使导体图案8a带电的工序

72.在实施方式1的静电耐压试验方法中,为了产生基于cbe的静电放电,首先进行使安装基板8的导体图案8a带电的工序。图5是用于说明使导体图案8a带电的工序的图。

73.在本工序中,首先,将图3所示的静电耐压试验装置100设定为初始状态。在初始状态下,将开关1的触点1b设为接通(即,将触点1a断开),将开关电路6的开关6a~6c设为断开。接着,针对初始状态的静电耐压试验装置100,设置成为试验对象的半导体装置20。即,在绝缘体5上设置安装基板8。

74.接着,通过使用未图示的驱动部使探针11a~11c进行动作,如图5所示,使探针11a~11c分别接触半导体装置20的端子9a~9c。通过探针11a~11c接触,端子9a~9c与开关6a~6c的第1端子分别电连接。但是,开关6a~6c均为断开状态,因此,端子9a~9c与电力线24(即,gnd)被电切断。

75.接着,如图5所示,将开关1的触点1a设为接通(即,将触点1b断开)。当触点1a被接通时,如图中的箭头所示,从直流电源2向电力线21供给的电压经由开关1和电阻3被施加到金属板4。由此,在金属板4中蓄积正电荷。另外,虽然在图5的例子中,金属板4蓄积正电荷,但能够通过采用蓄积负电荷的结构,进行再现了安装基板8带负电的状态的试验。

76.另外,电阻3是为了限制向金属板4施加电压时的浪涌电流而设置的。电阻3具有几mω的电阻值。通过设置电阻3,能够减小直流电源2的电流电容,结果上能够实现直流电源2的小型化。

77.隔着绝缘体5而与金属板4对置的导体图案8a在静电耐压试验装置100的初始状态下呈电中性,因此,正电荷与负电荷等量存在。当触点1a被接通而向金属板4施加电压时,在导体图案8a中,不存在电荷流出的路径,因此,如图5所示,产生极化。另外,虽然产生极化,但存在于导体图案8a的正电荷与负电荷保持等量不变。通过极化,导体图案8a的电荷12相对于gnd产生电力线,因此,导体图案8a相对于gnd具有电位。

78.(2-2)将导体图案8a的电荷放电的工序

79.接着,进行将蓄积于导体图案8a的电荷放电的工序。在本工序中,通过使蓄积于导体图案8a的电荷12经由半导体器件10向gnd放电,从而再现基于cbe的静电放电。图6是用于说明使导体图案8a的电荷12放电的工序的图。

80.在本工序中,一边将开关1的触点1a保持为接通状态,一边将开关电路6的开关6a~6c的至少1个接通。在图6的例子中,将开关6a~6c同时接通。通过将开关6a接通,经由端子9a、探针11a、开关6a以及电力线24而将半导体器件10的引脚10a与gnd电连接。半导体器件10的引脚10b、10c也同样,通过将开关6b、6c接通而与gnd电连接。

81.通过半导体器件10的多个引脚10a~10c同时与gnd电连接,如图6中的箭头所示,在导体图案8a与gnd之间形成经由半导体器件10的电路径。该电路径在从引脚10a~10c到gnd的区间内分支为多个电路径。蓄积于导体图案8a的电荷12在流入半导体器件10后,通过这多个电路径而流入gnd。

82.在像这样将构成开关电路6的多个开关6a~6c中的2个以上的开关同时接通的情况下,在半导体器件10的引脚与gnd之间形成多个电路径,因此,与仅接通了单一的开关的情况相比,能够使导体图案8a的电荷12的放电路径整体的阻抗下降。然后,通过该阻抗的下降,在放电路径中流动的电流增大。但是,半导体器件10的gnd引脚10d在单一的端子中流动全部的电流,因此,电流超过容许值而增大,由此可能发生静电破坏。

83.另外,能够通过调整在开关电路6中接通的开关的数量而变更放电路径整体的阻抗。放电路径整体的阻抗随着增加接通的开关的数量而变小。其结果是,在放电路径中流动

的电流变大。如图2所示,在制造现场中,在每次向多个端子9插入连接器14时,各端子9的接触方式变化。因此,需要测定与端子9的接触方式发生了变化时的静电耐压。

84.根据实施方式1的静电耐压试验装置100,通过开关电路6对静电放电的路径进行控制,因此,能够在多个端子9a~9c中的选择出的端子9中产生静电放电。即,由于开关6a~6c与半导体器件10的引脚10a~10c以1对1的方式对应地连接,因此,能够仅利用选择出的端子9产生静电放电。这样,能够假定向多个端子9a~9c插入了连接器14时的各端子9的接触方式的变化而测定静电耐压。

85.另外,在不使用开关电路6而例如使用连接器14实施了静电耐压试验的情况下,有时受到周围的环境(湿度等)、使连接器14插入的速度和插入的角度、连接器14的污染等各种影响。因此,即便在相同的测定条件下实施静电耐压试验,也可能得不到具有再现性的试验结果。另一方面,实施方式1的静电耐压试验装置100由于在放电路径的形成中使用开关电路6,因此,抑制了上述的周围环境等的影响,结果上能够进行再现性高的静电耐压试验。

86.(2-3)对金属板4进行除电的工序

87.在静电放电结束时,进行对金属板4进行除电的工序。图7是用于说明对金属板4进行除电的工序的图。

88.在本工序中,如图7所示,通过将开关电路6的开关6a~6c全部断开而将半导体器件10的引脚10a~10c与gnd电切断。接着,将开关1的触点1b设为接通(即,将触点1a断开)。

89.通过触点1b接通,金属板4经由电阻3、电力线23及电力线22而与gnd电连接。蓄积于金属板4的电荷经由电阻3、电力线23及电力线22而流入gnd。在对金属板4进行除电之后,使探针11a~11c进行动作,使得解除与端子9a~9c的接触。由此,静电耐压试验装置100返回到初始状态。

90.(半导体器件的故障判定方法)

91.接着,对实施方式1的静电耐压试验中的判定半导体器件10的故障的方法进行说明。

92.半导体器件10的故障判定是基于在静电放电的前后实施的半导体器件10的电测定的结果而进行的。图8是示出用于测定半导体器件10的电特性的测定装置的结构例的图。

93.如图8所示,用于测定半导体器件10的电特性的测定装置110具有测定器16、运算器17、以及多个探针11a~11d。对于探针11,例如能够应用弹簧探针。

94.多个探针11a~11d的第1端子与测定器16连接。多个探针11a~11c的第2端子与半导体装置20的多个端子9a~9c分别连接。多个探针11d的第2端子与半导体装置20的gnd端子9d连接。另外,在图8的例子中,将探针11的数量设为4,但探针11的数量为多个即可。

95.测定器16是用于测定半导体器件10的电特性的部位,例如具有包括电压源或电流源的曲线描绘仪等。测定器16构成为能够测定半导体器件10的端子间的电压和流向半导体器件10的电流。

96.通过使用未图示的驱动部使探针11a~11d进行动作,如图8所示,使探针11a~11d分别与半导体装置20的端子9a~9d接触。通过使探针11a~11d接触,测定器16经由探针11a~11d和端子9a~9d而与半导体器件10的引脚10a~10d电连接。

97.运算器17与测定器16连接,受理由测定器16测定的半导体器件10的端子间电压和电流的测定值。运算器17基于测定值,判定半导体器件10是否发生了故障。

98.具体而言,在静电放电的实施前和实施后,使用测定器16对半导体器件10的电特性进行测定,在运算器17中比较实施前后的电特性的测定值。在半导体器件10由于静电放电而发生了故障的情况下,半导体器件10的电阻值会发生变化。例如在半导体器件10发生了开路故障的情况下,半导体器件10的电阻值增加,即便施加电压,也不流过电流。另一方面,在半导体器件10发生了短路故障的情况下,半导体器件10的电阻值下降,当施加电压时,一下子流动电流。因此,如果在静电耐压试验的实施前与实施后确认到半导体器件10的电特性的测定值的变化,则能够判断为半导体器件10发生了故障。

99.(静电耐压试验处理流程)

100.图9是用于说明实施方式1的静电耐压试验方法的处理流程的流程图。

101.如图9所示,实施方式1的静电耐压试验方法具备:测定产生静电放电前的半导体器件10的电特性的工序;产生静电放电的工序;以及测定产生静电放电后的半导体器件10的电特性的工序。

102.在测定产生静电放电前的半导体器件10的电特性的工序中,使用图8所示的测定装置110,对半导体器件10的电特性(第1电特性)进行测定。

103.具体而言,首先,通过步骤s01,将测定器16与半导体装置20的端子9a~9d连接。在步骤s01中,使探针11a~11d与端子9a~9d分别接触。

104.接着,通过步骤s02,对半导体器件10的电特性进行测定。在步骤s02中,将开关电路6的开关6a~6c中的至少1个和开关6d接通,并且,从测定器16向半导体器件10施加电压及/或电流。由测定器16测定的半导体器件10的电特性的测定值被送出到运算器17。运算器17将半导体器件10的电特性的测定值作为初始特性保存于存储部。

105.当半导体器件10的电特性的测定结束后,通过步骤s03,使探针11a~11d进行动作,使得解除与端子9a~9d的接触,由此,从端子9a~9d卸下测定器16。

106.接着,在产生静电放电的工序中,使用图3所示的静电耐压试验装置100,使半导体器件10产生基于cbe(基板带电事件)的静电放电。

107.具体而言,首先,通过步骤s04,对设定为初始状态的静电耐压试验装置100设置成为试验对象的半导体装置20。在步骤s04中,在绝缘体5上设置安装基板8。另外,由于静电耐压试验装置100为初始状态,因此,开关1的触点1b被接通。

108.接着,通过步骤s05,使探针11a~11c进行动作,由此,如图5所示,使探针11a~11c与半导体装置20的端子9a~9c分别接触。由此,端子9a~9c与开关电路6的开关6a~6c分别电连接。但是,由于开关6a~6c均为断开状态,因此,端子9a~9c与电力线24(即,gnd)被电切断。

109.接着,通过步骤s06,设定从直流电源2向电力线21供给的电压。该电压成为向金属板4施加的电压。

110.当设定了来自直流电源2的施加电压时,通过步骤s07,将开关1的触点1a设为接通(即,将触点1b断开)。当触点1a被接通时,从直流电源2向电力线21供给的电压经由开关1和电阻3被施加到金属板4。其结果是,如图5所示,在金属板4中蓄积正电荷,导体图案8a带电。

111.接着,进入步骤s08,一边将开关1的触点1a保持为接通状态,一边将开关电路6的开关6a~6c中的至少1个开关接通。此时,通过将2个以上的开关同时接通,半导体器件10的引脚10a~10c中的2个以上的引脚同时与gnd电连接,因此,在导体图案8a与gnd之间形成经

由半导体器件10的多个电路径。当蓄积于导体图案8a的电荷12流入半导体器件10时,通过这多个电路径而流入gnd。

112.接着,通过步骤s09,将开关电路6的开关6a~6c全部断开,由此将半导体器件10的引脚10a~10c与gnd电切断。此外,将开关1的触点1b设为接通(即,将触点1a断开)。通过触点1b接通,蓄积于金属板4的电荷经由电阻3、电力线23及电力线22而流入gnd。

113.在对金属板4进行除电之后,通过步骤s10,使探针11a~11c进行动作,使得解除与端子9a~9c的接触,由此,从端子9a~9c卸下开关电路6。

114.接着,在测定产生静电放电后的半导体器件10的电特性的工序中,再次使用图8所示的测定装置110来测定半导体器件10的电特性(第2电特性)。

115.具体而言,首先,在步骤s11中,将测定器16与半导体装置20的端子9a~9d连接。在步骤s11中,使探针11a~11d与端子9a~9d分别接触。

116.接着,通过步骤s12,对半导体器件10的电特性进行测定。步骤s12的处理与步骤s02的处理相同。即,将开关电路6的开关6a~6c中的至少1个和开关6d接通,并且,从测定器16向半导体器件10施加电压及/或电流。

117.运算器17在从测定器16取得半导体器件10的电特性的测定值后,进入步骤s13,对在步骤s12中取得的电特性(第2电特性)的测定值与在步骤s02中取得的初始特性(第1电特性)进行比较,由此,判定半导体器件10是否发生了故障。

118.在判定为半导体器件10发生了故障的情况下(s13的判定为是时),结束静电耐压试验。另一方面,在判定为半导体器件10未发生故障(即,正常)的情况下(s13的判定为否时),进入步骤s14,运算器17判定是否能够进一步增加来自直流电源2的施加电压。在步骤s14中,在当前的施加电压达到直流电源2能够输出的电压范围的上限值的情况下,判定为无法增加施加电压。在无法增加施加电压的情况下(s14的判定为否时),结束静电耐压试验。

119.另一方面,如果当前的施加电压未达到该上限值(s14的判定为是时),则运算器17判定为能够增加施加电压,返回步骤s04,再次执行产生静电放电的工序。在本工序中,通过步骤s06,将施加电压变更为比当前的电压值高的电压值。然后,通过执行步骤s07~s10的处理,使半导体器件10产生静电放电。接下来,通过执行步骤s11~s14的处理,测定半导体器件10的电特性,基于该测定值与初始特性的比较来判定半导体器件10有无故障。

120.如以上说明的那样,根据实施方式1的静电耐压试验装置和静电耐压试验方法,能够在设置于半导体装置20的安装基板8的多个端子9中同时产生静电放电,因此,能够测定由于如向多个端子9插入连接器时那样金属同时与多个端子9接触而产生静电放电的工序中的静电耐压。这样,能够准确地测定安装基板8上的半导体器件10的静电耐压。

121.此外,根据实施方式1的静电耐压试验装置和静电耐压试验方法,通过开关电路6来控制静电放电的发生路径,因此,能够在从多个端子9中选择出的端子9中产生静电放电。这样,能够假定向多个端子9插入连接器时的各端子9的接触方式的变化而测定静电耐压。

122.此外,通过开关电路6中的多个开关6a~6c的接通断开而产生静电放电,因此,能够抑制周围环境的影响,结果上能够实现再现性高的静电耐压试验。

123.实施方式2

124.在上述的实施方式1中,针对静电耐压试验装置100与测定装置110分体的结构例

进行了说明,但也能够采用使静电耐压试验装置和测定装置一体化的结构。在该结构中,能够使用开关来选择性地驱动静电耐压试验装置和测定装置。

125.(静电耐压试验装置的结构例)

126.图10是概要地示出实施方式2的静电耐压试验装置的结构例的图。

127.如图10所示,实施方式2的静电耐压试验装置100a是对图3所示的实施方式1的静电耐压试验装置100附加了测定器16、运算器17以及开关18、并且将开关电路6和控制部7分别置换为开关电路6a和控制部7a而得到的。在静电耐压试验装置100a中,测定器16和运算器17与图8所示的测定装置110中的测定器16和运算器17分别相同,因此省略说明。

128.开关18连接在电力线25、26与电力线24之间。对于开关18,能够应用半导体开关或机械式开关。开关18对应于“第3开关”的一实施例。

129.开关18构成为能够按照来自控制部7a的控制信号,将电力线25与电力线24和电力线26中的任意一方电连接。作为一例,开关18具有3个触点18a~18c。触点18a、18b是固定触点,触点18c是选择性地与触点18a、18b连接的可动触点。触点18a与电力线25的第1端子连接,触点18a与电力线24的第1端子连接,触点18b与电力线26的第1端子连接。电力线25的第2端子与开关电路6a的开关6a~6c的第1端子连接。电力线26的第2端子与测定器16连接。

130.开关电路6a连接在半导体装置20的端子9与电力线25及测定器16之间。开关电路6a是向图3所示的开关电路6追加了开关6d而得到的。开关6d连接在gnd端子9d与测定器16之间。对于开关6d,能够应用半导体开关或机械式开关。开关6d构成为按照来自控制部7a的控制信号而接通/断开,由此进行gnd端子9d与测定器16的电连接/切断。

131.通过将开关18的触点18c与触点18a连接,从而将电力线25与电力线24电连接,因此,能够形成图3所示的静电耐压试验装置100。另一方面,通过将开关18的触点18c与触点18b连接,从而将电力线25与电力线26电连接,因此,经由开关6a~6c将半导体装置20的端子9a~9c与测定器16连接。由此,能够形成图8所示的测定装置110。即,静电耐压试验装置100a构成为能够切换静电耐压试验装置100与测定装置110。

132.在以下的说明中,把将触点18c与触点18a连接称为“将触点18a接通”,把将触点18c与触点18b连接称为“将触点18b接通”。另外,在开关18中,在触点18a为接通时触点18b被断开,在触点18b为接通时触点18a被断开。

133.控制部7a对开关1、18和开关电路6a的接通断开进行控制。控制部7a例如能够由微型计算机等构成。具体而言,控制部7具备cpu71、以及存储程序和数据的存储器72,通过基于cpu71执行该程序而实现的软件处理,能够执行后述的控制动作。或者,关于该控制动作的一部分或全部,也能够代替软件处理,通过使用了内置的专用的电子电路等的硬件处理来实现。

134.控制部7a与控制部7同样,能够相互独立地控制开关电路6所包含的多个开关6a~6c的接通断开。因此,控制部7a能够将多个开关6a~6c中的至少1个开关接通。

135.(静电耐压试验方法)

136.接着,使用图11至图13,对实施方式2的静电耐压试验方法进行说明。图11是用于说明实施方式2的静电耐压试验方法的处理流程的流程图。图11的流程图与图9所示的流程图相比,开关18和开关电路6a的控制不同。

137.如图11所示,实施方式2的静电耐压试验方法具备:测定产生静电放电前的半导体

器件10的电特性的工序;产生静电放电的工序;以及测定产生静电放电后的半导体器件10的电特性的工序。

138.在测定产生静电放电前的半导体器件10的电特性的工序中,使用图10所示的测定器16和运算器17,来测定半导体器件10的电特性(第1电特性)。图12是用于说明测定半导体器件10的电特性的工序的图。

139.具体而言,首先,通过步骤s21,对设定为初始状态的静电耐压试验装置100a设置成为试验对象的半导体装置20。在初始状态下,将开关1的触点1b设为接通(即,将触点1a断开)。

140.接着,通过步骤s22,使未图示的探针与半导体装置20的端子9a~9d接触,由此,端子9a~9d与开关电路6a的开关6a~6d分别电连接。但是,由于开关6a~6d均为断开状态,因此,端子9a~9c与电力线25被电切断,并且,gnd端子9d与测定器16被电切断。

141.通过步骤s23,将开关18的触点18b设为接通(即,将触点18a断开)。接着,通过步骤s24,对半导体器件10的电特性进行测定。在步骤s24中,将开关电路6a的开关6a~6c中的至少1个和开关6d接通,并且从测定器16向半导体器件10施加电压及/或电流。由测定器16测定的半导体器件10的电特性的测定值被送出到运算器17。运算器17将半导体器件10的电特性的测定值作为初始特性保存于存储部。

142.当半导体器件10的电特性的测定结束,通过步骤s25,将开关电路6a的开关6a~6d全部设为断开。

143.接着,在产生静电放电的工序中,使半导体器件10产生基于cbe(基板带电事件)的静电放电。图13是用于说明产生静电放电的工序的图。

144.具体而言,首先通过步骤s26,将开关18的触点18a设为接通(即,将触点18b断开)。另外,开关1的触点1b保持接通不变。

145.接着,通过步骤s27,设定从直流电源2向电力线21供给的电压。该电压成为向金属板4施加的电压。当设定了来自直流电源2的施加电压时,通过步骤s28,将开关1的触点1a设为接通(即,将触点1b断开)。当接通了触点1a时,从直流电源2向电力线21供给的电压经由开关1和电阻3被施加到金属板4。

146.接着,进入步骤s29,一边将开关1的触点1a保持为接通状态,一边将开关电路6a的开关6a~6c中的至少1个接通。另外,开关6d保持断开不变。在图13的例子中,将开关6a~6c同时接通。在步骤s29中,通过将多个开关6a~6c中的2个以上的开关同时接通,从而半导体器件10的引脚10a~10c中的2个以上的引脚同时与gnd电连接,因此,在导体图案8a与gnd之间形成经由半导体器件10的多个电路径。当蓄积于导体图案8a的电荷12流入半导体器件10时,通过这多个电路径而流入gnd。

147.接着,通过步骤s30,将开关电路6a的开关6a~6c全部断开,由此,将半导体器件10的引脚10a~10c与gnd电切断。此外,将开关1的触点1b设为接通(即,将触点1a断开)。通过触点1b接通,蓄积于金属板4的电荷经由电阻3、电力线23及电力线22而流入gnd。

148.接着,在测定产生静电放电后的半导体器件10的电特性的工序中,再次使用图10所示的测定器16和运算器17来测定半导体器件10的电特性(第2电特性)。

149.具体而言,首先,通过步骤s31,将开关18的触点18b设为接通(即,将触点18a断开),将开关1的触点1b设为接通(即,将触点1a断开)。另外,开关电路6a的开关6a~6d全部

为断开。

150.接着,通过步骤s32,测定半导体器件10的电特性(第2电特性)。步骤s32的处理与步骤s24的处理相同。即,将开关电路6a的开关6a~6c中的至少1个和开关6d接通,并且从测定器16向半导体器件10施加电压及/或电流。

151.运算器17在从测定器16取得了半导体器件10的电特性的测定值时,进入步骤s33,对在步骤s32中取得的电特性(第2电特性)的测定值与在步骤s24中取得的初始特性(第1电特性)进行比较,由此,判定半导体器件10是否发生了故障。

152.在判定为半导体器件10发生了故障的情况下(s33的判定为是时),结束静电耐压试验。另一方面,在判定为半导体器件10未发生故障的情况下(s33的判定为否时),进入步骤s34,运算器17判定是否能够进一步增加来自直流电源2的施加电压。在无法增加施加电压的情况下(s34的判定为否时),结束静电耐压试验。

153.另一方面,在能够增加施加电压的情况下(s34的判定为是时),返回步骤s26,再次执行产生静电放电的工序。在本工序中,通过步骤s27,将施加电压变更为比当前的电压值高的电压值。然后,通过执行步骤s28~s30的处理,使半导体器件10产生静电放电。接下来,通过执行步骤s31~s34的处理,对半导体器件10的电特性进行测定,基于该测定值与初始特性的比较来判定半导体器件10有无故障。

154.如以上说明的那样,在实施方式2的静电耐压试验装置和静电耐压试验方法中,也能够通过对开关电路6a的开关6a~6c进行控制,从而在设置于半导体装置20的安装基板8的多个端子9中同时产生静电放电,因此,能够得到与实施方式1的静电耐压试验装置和静电耐压试验方法同样的效果。

155.另外,针对上述的实施方式和变更例,从申请开始就计划包括说明书中未提及的组合,在不产生不良情况或矛盾的范围内,适当组合在实施方式中说明的结构。

156.此次公开的实施方式在所有方面进行了例示,不应认为是限制性的内容。本公开的范围非由上述的说明示出而是由权利要求书示出,包含与权利要求书同等的含义和范围内的全部变更。

157.附图标记说明

158.1、6a~6d、18开关,1a~1c、18a~18c触点,2直流电源,3电阻,4金属板,5绝缘体,6、6a开关电路,7、7a控制部,8安装基板,8a导体图案,8b绝缘层,9、9a~9d端子,10半导体器件,10a~10d引脚,10e半导体元件,10f密封树脂,11、11a~11d探针,12电荷,12a~12c布线,13壳体,14连接器,15设备,16测定器,17运算器,20半导体装置,21~26电力线,71cpu,72存储器,100、100a静电耐压试验装置,110测定装置。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1