基于FPGA的三重交叠A/C模式应答信号解码算法的制作方法

本发明属于二次雷达信号处理,具体涉及一种基于fpga的三重交叠a/c模式应答信号解码算法。

背景技术:

1、空中交通管制雷达信标系统(air traffic control radar beacon system,atcrbs),是现代航空交通管制系统的重要组成部分,它通过询问机向空中目标发送询问,目标根据收到的询问做出应答的方式来识别空中目标,其工作模式主要是a/c模式,a模式提供飞机的识别码,c模式提供飞机的高度码。两种模式的应答码格式相同,由框架脉冲f1、f2以及其之间的代码脉冲组成,所以解码a/c模式应答信号需要不断检测框架脉冲f1、f2,同时将f1、f2之间的信息保存下来。如果检测到有效的框架脉冲f1、f2,则从f1、f2之间的信息中提取代码脉冲。

2、绝大部分军、民用飞机都配备了atcrbs应答器,随着空中交通密度的日益增加,航管中存在的串扰、混扰和虚假目标等问题日趋严重。识别多目标交叠,拒绝目标幻影和避免异步串扰是a/c模式应答信号处理的关键问题。常规的fpga+dsp处理方法是通过fpga实现信号二值化、旁瓣抑制、脉冲提取和存储,dsp根据存储的数据进行框架查找,代码脉冲提取,从而实现目标解码。这种方法在低密度的环境中能够准确完成解码。二次雷达的询问频率为50hz~450hz,当空中目标较多时,fpga存储大量数据给dsp,对于串行处理方式的dsp来说进行框架检测和代码信息提取将会耗费更多的时间。因此,在复杂环境下提高信号的处理能力和处理速度成为现代航空交通管制系统中a/c应答信号处理环节亟待解决的问题。

3、fpga集成度高,处理速度快,执行效率高,能完成复杂的时序逻辑设计,且编程灵活方便,是现代信号高速处理、信号编解码的主要手段。合理利用fpga编程中的组合逻辑和时序逻辑,并加以时序约束,可代替dsp实现复杂的信号处理算法。

技术实现思路

1、本发明的目的在于提出一种基于fpga的三重交叠a/c模式应答信号解码算法。

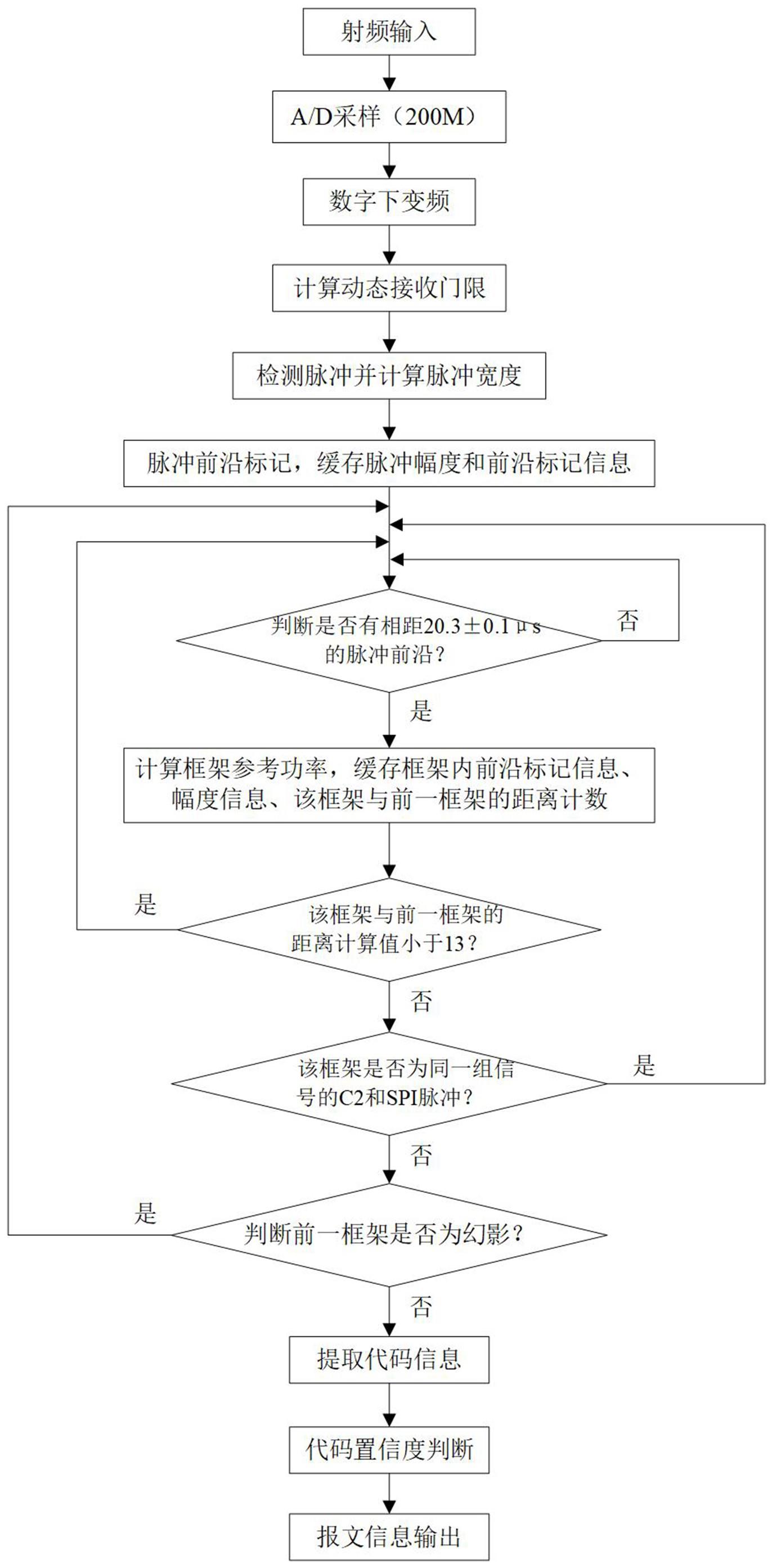

2、本发明的特征在于,充分利用fpga强大的信号处理能力,完成应答信号交叠脉冲分解、框架检测、代码脉冲提取、置信度判断以及去幻影等,最终实现最多三重交叠a/c模式应答信号解码,在复杂环境下提高了空中交通管制系统中a/c应答信号的处理能力和处理速度。该方法包含以下内容:

3、(1) 计算动态接收门限dmtl;

4、(2) 根据动态接收门限检测脉冲,并计算脉冲宽度;

5、(3) 根据脉冲幅度和脉冲宽度,标记脉冲前沿;

6、(4) 根据脉冲前沿检测a/c应答框架,计算该框架的参考功率,保存框架脉冲之间的数据信息、前沿标记信息以及该框架与前一框架间的距离,并起始下一次距离计数;

7、(5) 接收到当前框架,根据框架间距离判断前一框架是否为幻影,若是则不进行处理,若否,则提取代码脉冲;

8、(6) 根据代码脉冲与框架脉冲的时序关系以及前沿标记信息提取代码脉冲,并计算脉冲功率;

9、(7) 将代码脉冲功率与参考功率相比较,若差值在±1db范围内,该代码脉冲的置信度为1,反之为0。

技术特征:

1.一种基于fpga的三重交叠mode a/c应答信号解码算法,其特征在于,该算法包含以下步骤:

2.根据权利要求1所述的一种基于fpga的三重交叠a/c模式应答信号解码算法,其特征在于在解三重交叠脉冲时,一个时钟完成脉冲宽度的计数,根据脉冲宽度和脉冲幅度得到脉冲前沿信息,并同步缓存有效脉冲的前沿标记信息和幅度信息,用于后续框架检测和代码脉冲提取。

技术总结

本发明公开了一种基于FPGA的三重交叠A/C模式应答信号解码算法。其特点在于:对Mode A/C应答信号高速AD采样后做数字下变频处理,根据基带信号的幅度信息和时间信息将交叠的脉冲分离开,利用目标应答信号脉冲幅度的一致性和脉冲距离的相关性,结合FPGA的并行处理能力以及阻塞赋值和非阻塞赋值方式,快速准确地提取出三重交叠Mode A/C应答信号的框架信息和代码信息,同时剔除虚假目标。本发明提出的三重交叠应答信号解码算法完全基于FPGA设计,在高密度环境中突破了以往FPGA+DSP处理在实时性上的限制,提高了系统对应答信号的处理能力。

技术研发人员:张漫漫,李洪高,李友华,陶英健,钱书元,任修顺,于德焘,邵保国

受保护的技术使用者:烟台三航雷达服务技术研究所有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!