感测电阻器的制作方法

本发明的实施例涉及电子系统,更具体地,涉及用于将感测电阻器集成到电路板中的系统和方法。

背景技术:

1、电流感测电阻器(也称为感测电阻器)通常是焊接在客户电路板上的分立电阻器。然而,这样的电阻器可能不太适合于满足即将到来的感测电阻器设计的性能目标,例如低阻抗。因此,需要提高感测电阻器的性能。

技术实现思路

1、所描述的技术的方法和装置各自具有几个方面,其中没有一个单独对其期望的属性负责。

2、在一个方面,提供一种集成感测电阻器,包括:在至少第一横向方向上与多个第二金属凸块交替的多个第一金属凸块;和多个薄膜电阻器,每个薄膜电阻器设置在所述第一和第二金属凸块的一对相邻者之间并电连接,其中所述集成感测电阻器被配置为感测由流过所述集成感测电阻器的电流产生的电压,以确定所述电流的值。

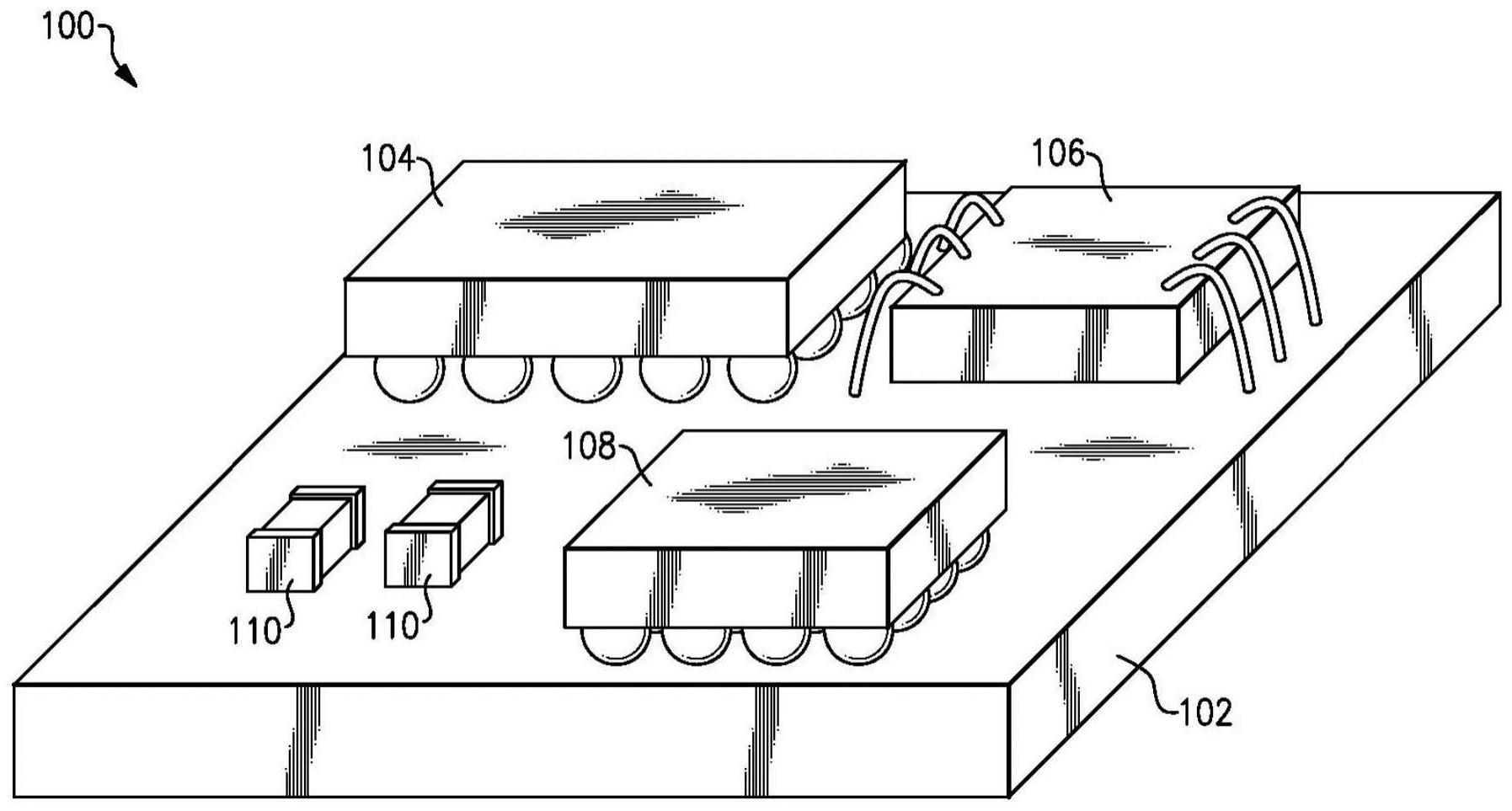

3、在另一方面,提供一种封装系统(sip),包括:板基板;和集成感测电阻器,包括:在至少第一横向方向上与多个第二金属焊盘或凸块交替的多个第一金属焊盘或者凸块,以及多个薄膜电阻器,每个薄膜电阻器设置在一对相邻的第一和第二金属焊盘或凸块之间并电连接;其中所述第一金属焊盘或凸块通过所述板基板彼此电连接,并且其中所述第二金属接触焊盘或凸点通过所述板基板彼此电相连。

4、在又一方面,提供一种集成感测电阻器,包括:在至少第一横向方向上与多个第二金属焊盘交替的多个第一金属焊盘;和多个薄膜电阻器,每个薄膜电阻器设置在第一和第二金属焊盘的一对相邻者之间并电连接,其中所述第一金属焊盘彼此电断开,并且其中所述第二金属焊盘彼此电断开。

技术特征:

1.一种集成感测电阻器,包括:

2.权利要求1所述的集成感测电阻器,其中所述集成感测电阻器形成在板基板上,其中所述第一和第二金属凸块通过所述板基板彼此电连接,并且其中所述第二金属凸块经由所述板基板彼此电连接。

3.权利要求1所述的集成感测电阻器,其中所述第一金属凸块和所述第二金属凸块进一步在与所述第一横向方向交叉的第二方向上交替。

4.权利要求3所述的集成感测电阻器,其中所述第二横向方向与所述第一横向方向正交,使得所述第一和第二金属凸块以棋盘图案布置。

5.权利要求4所述的集成感测电阻器,其中所述第一和第二金属凸块形成阵列,所述阵列包括在所述第一横向方向上延伸的行和在所述第二横向方向上延伸的列,所述行和列中的每一个包括与所述第二金属凸块交替的第一金属凸块。

6.权利要求5所述的集成感测电阻器,其中相邻行由在所述第一横向方向上对齐的一行薄膜电阻器插入,并且其中相邻列由在所述第二横向方向上对齐的一列薄膜电阻器插入。

7.权利要求1所述的集成感测电阻器,其中所述薄膜电阻器在半导体基板上光刻图案化。

8.权利要求1所述的集成感测电阻器,其中所述第一金属凸块在第一垂直金属水平处彼此电连接,并且所述第二金属凸块以不同于所述第一垂直金属水平的第二垂直金属水平彼此电连接。

9.一种封装系统(sip),包括:

10.权利要求9所述的sip,其中所述第一金属焊盘或凸块和所述第二金属焊盘或者凸块进一步在与所述第一横向方向交叉的第二方向上交替。

11.权利要求10所述的sip,其中所述薄膜电阻器在半导体基板上光刻图案化。

12.权利要求10所述的sip,其中所述第一金属焊盘或凸块在第一垂直金属水平处彼此电连接,并且所述第二金属焊盘或者凸块在不同于所述第一垂直金属水平的第二垂直金属水平处彼此电连接。

13.权利要求12所述的sip,其中所述第一金属焊盘或凸块在所述第一垂直金属水平处通过第一金属片彼此电连接,并且所述第二金属焊盘或者凸块在第二垂直金属处通过第二金属片彼此电连接。

14.权利要求9所述的sip,其中所述板基板包括层压聚合物基板,并且其中所述板基板在其上形成有附加的分立集成电路组件。

15.一种集成感测电阻器,包括:

16.权利要求15所述的集成感测电阻器,其中所述第一金属焊盘被配置为通过板基板彼此电连接,并且其中所述第二金属接触焊盘被配置成通过所述板基板彼此电连接。

17.权利要求15所述的集成感测电阻器,其中所述第一金属焊盘和所述第二金属焊盘进一步在与所述第一横向方向交叉的第二方向上交替。

18.权利要求15所述的集成感测电阻器,其中所述薄膜电阻器包括相同数量的薄膜电阻器,其中相对于电流在所述第一横向方向上从右向左流动的薄膜电阻器,电流在所述第一横向方向上从左向右流动。

19.权利要求15所述的集成感测电阻器,其中所述薄膜电阻器包括堆叠,所述堆叠包括具有正电阻系数(tcr)的第一层和具有负tcr的第二层,使得净tcr具有比所述第一层和所述第二层中的每一个的tcr的幅度小的幅度。

20.权利要求16所述的集成感测电阻器,其中所述第一金属焊盘被配置为在所述板基板上方的第一垂直金属水平处彼此电连接,并且所述第二金属焊盘被配置为在与所述第一垂直金属水平不同的所述板基底上方的第二垂直金属水平处彼此电连接。

技术总结

本公开涉及感测电阻器。公开用于感测电阻器的系统和方法。在一方面,集成感测电阻器包括:在至少第一横向方向上与多个第二金属凸块交替的多个第一金属凸块;和多个薄膜电阻器,每个薄膜电阻器设置在所述第一和第二金属凸块的一对相邻者之间并电连接。集成感测电阻器可被配置为感测由流过所述集成感测电阻器的电流产生的电压,以确定所述电流的值。

技术研发人员:P·M·迈克古尼斯,J·W·考德威尔

受保护的技术使用者:亚德诺半导体国际无限责任公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!