一种新的半导体参数测试硬件架构系统的制作方法

本发明涉及一种新的半导体参数测试硬件架构系统,尤其涉及一种新的半导体参数测试硬件架构系统。

背景技术:

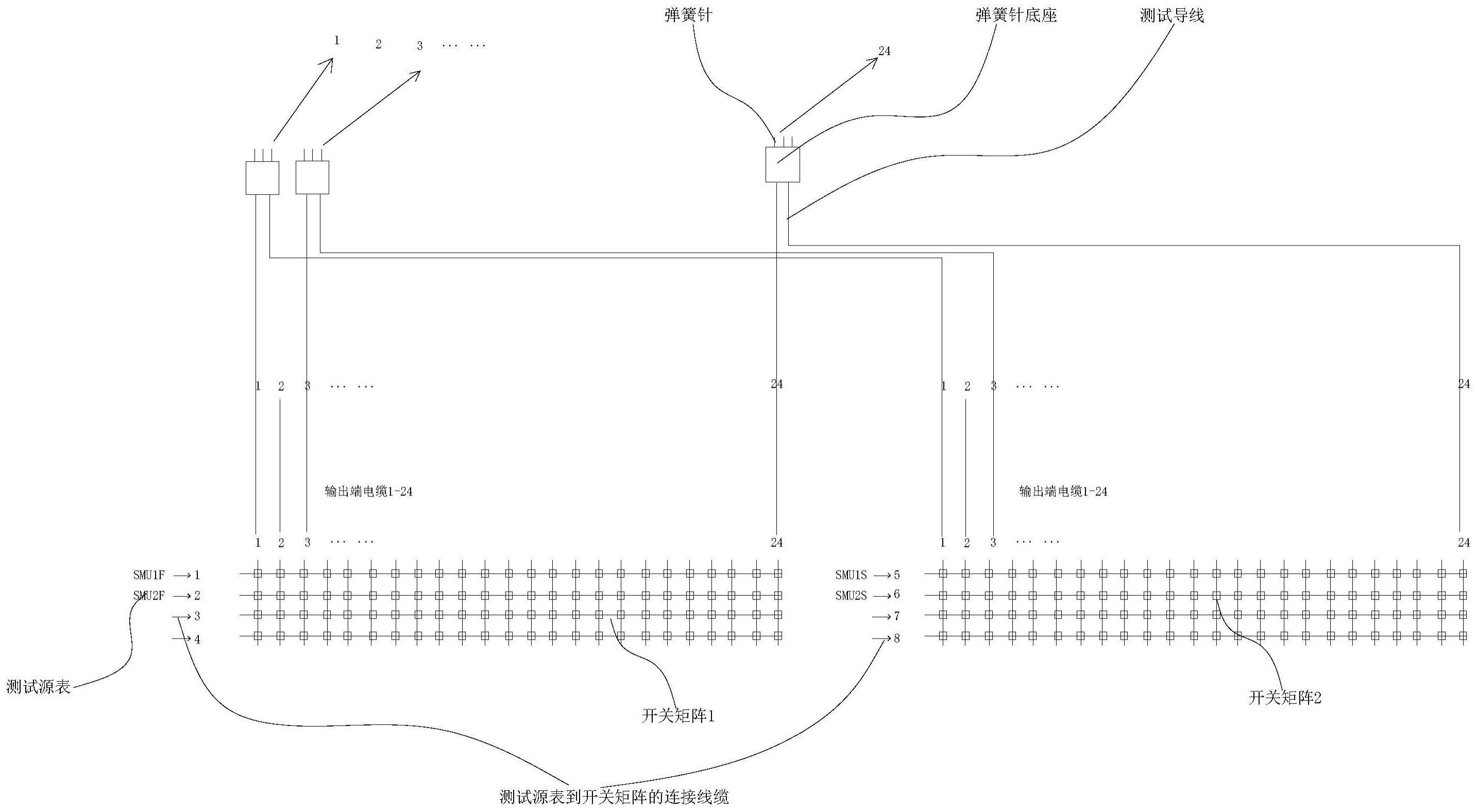

1、随着半导体制造技术的发展,半导体器件集成度不断提高。在晶圆级半导体参数测试领域,自动化测试机台的需求量在不断提高。传统半导体参数测试系统的开关矩阵为了实现半导体测试中需要的开尔文测试功能,对开关矩阵的需求比较大。以8个输入端口,24个输出端口为例如果需要实现kelvin测试,传统的开关矩阵需求规模为8*48。如附图1所示。传统的这种测试系统,使用起来成本较高,不利于对企业的发展。

技术实现思路

1、为了解决现有技术中存在的某种或某些技术问题,本申请的目的之一在于提供一种新的半导体参数测试硬件架构系统,能够降低企业的使用成本。

2、为解决上述现有的技术问题,本申请的目的之一采用如下技术方案实现:

3、一种新的半导体参数测试硬件架构系统,其包括测试模块和开关矩阵,所述测试模块包括源测量单元(sum)、数字万用表、电容测量单元和脉冲发生器单元(测试模块包括但不限于以上测试单元),所述开关矩阵上连接有弹簧针(pogo pin)测试导线。

4、进一步地,将传统的单个开关矩阵,按照输入端口拆分为两个独立的开关矩阵,将接有弹簧针的测试导线的两根线分别接到两个开关矩阵的对应端口,将sum的force端接到第一个开关矩阵的输入端,将smu的sense端接到第二个开关矩阵的输入端。

5、相比现有技术,本发明的有益效果在于:

6、通过合理的开关矩阵的组合和新的导线结构,可以将传统半导体参数测试系统的开关矩阵规模减半,实现半导体测试中必须的开尔文测试功能,显著的降低测试系统的使用成本。

技术特征:

1.一种新的半导体参数测试硬件架构系统,其特征在于:包括测试模块和开关矩阵,所述测试模块包括源测量单元(sum)、数字万用表、电容测量单元和脉冲发生器单元(测试模块包括但不限于以上测试单元),所述开关矩阵上连接有弹簧针(pogo pin)测试导线。

2.根据权利要求1所述的一种新的半导体参数测试硬件架构系统,其特征在于:将传统的单个开关矩阵,按照输入端口拆分为两个独立的开关矩阵,将接有弹簧针的测试导线的两根线分别接到两个开关矩阵的对应端口,将sum的force端接到第一个开关矩阵的输入端,将smu的sense端接到第二个开关矩阵的输入端。

技术总结

本申请公开了一种新的半导体参数测试硬件架构系统,其包括测试模块和开关矩阵,所述测试模块包括源测量单元(SUM)、数字万用表、电容测量单元和脉冲发生器单元(测试模块包括但不限于以上测试单元),所述开关矩阵上连接有弹簧针(pogo pin)测试导线。

技术研发人员:柯伟

受保护的技术使用者:海宁理万集成电路有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!