以芯片eCAP模块实现的链路口多时钟信号检测装置的制作方法

本技术属于芯片检测,具体地说,是涉及一种面向芯片的以芯片ecap模块实现的链路口多时钟信号检测装置。

背景技术:

1、时钟信号的稳定传输对芯片的有序、正常工作起着决定性作用。时钟信号的传输出现异常会导致芯片性能下降,甚至会导致芯片无法正常工作。此外,由于对信号要求实时处理并且数据量的不断增加,多片并行高速芯片的应用越来越广泛,在这之中起到关键作用的是桥接多芯片的链路口技术,因此当前芯片中的时钟单元往往都是通过链路口对外输出多路高频率的时钟信号,以供其他系统或者外设模块使用。因此,对链路口多路时钟信号进行检测是芯片测试中一个必要的项目。

2、现有的时钟信号检测方法,原理仍然停留在检测单一通道时钟信号上,面对多路传输的时钟信号,多是选择配备同数量的检测模块,这就增加了检测的成本,也削弱了检测装置的便携性,此外,由于链路口传输的高速和点对点特性,对检测设备的性能也提出了更高的要求。

3、如何简化检测装置、降低检测和设备成本、提高检测效率和适用范围和满足链路口高速特性的需求,是当前链路口多时钟信号检测领域需要解决的技术问题。

技术实现思路

1、本实用新型提出一种以芯片ecap模块实现的链路口多时钟信号检测装置,以芯片的捕捉单元(ecap模块)实现对多路链路口时钟信号的检测,具有结构简单、检测范围大的优点。

2、本实用新型采用以下技术方案予以实现:

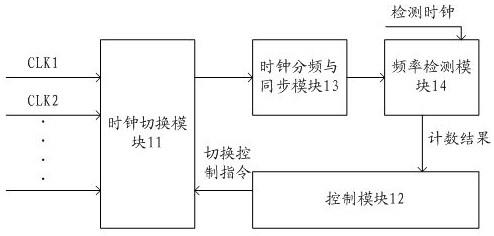

3、提出一种以芯片ecap模块实现的链路口多时钟信号检测装置,包括:

4、时钟切换电路,用于基于切换控制指令对链路口多时钟信号进行切换,输出多时钟信号之一作为时钟检测信号;

5、芯片,设有ecap模块;所述ecap模块被配置为捕捉模式,其计数器为捕捉时间提供基准时钟;所述时钟检测信号被接入所述ecap模块的输入端,经其预分频器分频得到分频信号;当检测到所述分频信号的第一个上升沿时,所述ecap模块的事件标志寄存器的值传递给其寄存器cap1,当检测到所述分频信号的第一个下降沿时,所述ecap模块的事件标志寄存器的值传递给其寄存器cap2;当检测到所述分频信号的第二个上升沿时,所述ecap模块的事件标志寄存器的值传递给其寄存器cap3,当检测到所述分频信号的第二个下降沿时,所述ecap模块的事件标志寄存器的值传递给其寄存器cap4,并触发中断输出计数结果;

6、控制器,连接所述时钟切换电路和所述芯片的ecap模块,用以对链路多时钟信号进行选择,向所述时钟切换电路发送所述切换控制指令;以及对所述ecap模块输出的计数结果进行处理得到检测结果。

7、在本实用新型一些实施例中,所述装置还包括:

8、输入设备,用以向所述控制器输入配置参数;所述配置参数包括时钟分频比、高频阈值和低频阈值;以使得所述控制器基于所述配置参数处理得到检测结果;其中,所述高频阈值和所述低频阈值为预设的参考计数值。

9、在本实用新型一些实施例中,所述预分频器对时钟检测信号分频时,对低频信号使用直通模式不进行分频。

10、在本实用新型一些实施例中,所述控制器还用于保存和显示检测结果。

11、与现有技术相比,本实用新型的优点和积极效果是:本实用新型提出的以芯片ecap模块实现的链路口多时钟信号检测装置,包括时钟切换电路、芯片的ecap模块和控制器;应用芯片的ecap模块的捕捉模式,以ecap模块的预分频器对时钟切换电路选择的时钟检测信号进行分频,将分频信号作为检测对象,以ecap模块的计数器实现对其上升沿和下降沿的计数,计数结果存储于ecap的寄存器中,在触发中断后向控制装置输出计数结果,控制模块则根据计数结果判断检测结果,对链路口被选择的一路时钟信号实现了检测,基于时钟切换电路的切换,能够实现对链路口多时钟信号的检测,本实用新型利用芯片的ecap模块,以单个链路口高频频率检测方式,根据需求按序对多路时钟信号均可实现监测,具有结构简单、检测范围广的优点。

12、结合附图阅读本实用新型实施方式的详细描述后,本实用新型的其他特点和优点将变得更加清楚。

技术特征:

1.一种以芯片ecap模块实现的链路口多时钟信号检测装置,其特征在于,包括:

2.根据权利要求1所述的以芯片ecap模块实现的链路口多时钟信号检测装置,其特征在于,所述装置还包括:

3.根据权利要求1所述的以芯片ecap模块实现的链路口多时钟信号检测装置,其特征在于,

4.根据权利要求1所述的以芯片ecap模块实现的链路口多时钟信号检测装置,其特征在于,所述控制器还用于保存和显示检测结果。

技术总结

本技术公开了一种以芯片eCAP模块实现的链路口多时钟信号检测装置,包括时钟切换电路、芯片的eCAP模块和控制器;应用eCAP模块的捕捉模式,以其预分频器对时钟切换电路选择的时钟检测信号进行分频,将分频信号作为检测对象,以其计数器实现对其上升沿和下降沿的计数,计数结果存储于其寄存器中,在触发中断后向控制装置输出计数结果,控制模块则根据计数结果判断检测结果,对链路口被选择的一路时钟信号实现了检测,基于时钟切换电路的切换,能够实现对链路口多时钟信号的检测,本技术利用芯片的eCAP模块,以单个链路口高频频率检测方式,根据需求按序对多路时钟信号均可实现监测,具有结构简单、检测范围广的优点。

技术研发人员:李瑞敏

受保护的技术使用者:青岛本原微电子有限公司

技术研发日:20221031

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!