一种芯片测试系统和方法与流程

本申请实施例涉及芯片检测领域,特别涉及一种芯片测试系统和方法。

背景技术:

1、在芯片成产工艺流程中,芯片生产完成后,需要通过检测部门对生产的芯片进行出厂前的检测工作,以确保芯片的各个模块和功能都能正常运行。测试内容至少包括中断、串口、复位、gpio以及存储功能等。

2、现阶段的芯片检测主要分为两部分,1.在ate机台上利用ate测试板进行功能和性能测试;2.在实装功能测试系统进行实装功能。也就是说,完成一个完成的芯片测试流程至少需要准备两套测试系统,这就导致完成整个测试流程需要将芯片在两个机台上来回装载测试,而中间转运装载启停的过程延长了整个测试周期,过程繁琐,且ate机台所需的测试程序开发难度大、周期长,不利于大批量芯片的检测。

技术实现思路

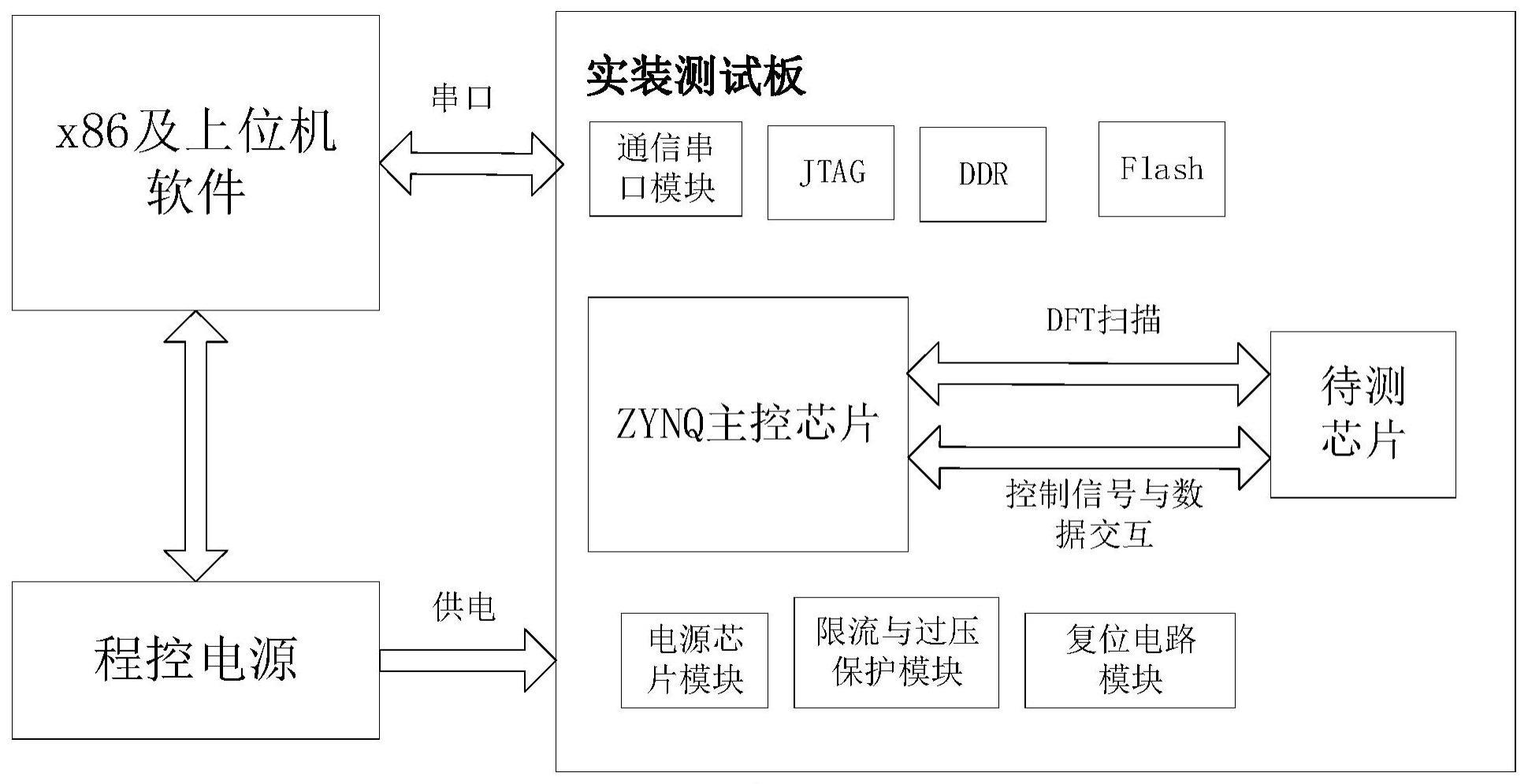

1、本申请实施例提供一种芯片测试系统,解决芯片测试周期长和检测繁琐的问题。所述系统包括上位机、程控电源、实装测试板、装载在实装测试板上的zynq主控芯片、待测芯片、电源芯片模块、和通信串口模块;

2、所述zynq主控芯片和所述待测芯片之间通过第一总线和第二总线相互连接,所述zynq主控芯片通过所述通信串口模块与所述上位机通信连接;所述电源芯片模块通过所述程控电源与所述上位机连接,且所述电源芯片模块分别连接所述zynq主控芯片和所述待测芯片,用于系统供电;

3、所述上位机用于通过所述通信串口模块向所述zynq主控芯片发送测试指令,控制系统进入扫描链dft模式或实装模式,并对所述待测芯片进行测试;

4、所述第一总线用于dft模式下数据交互,所述第二总线用于实装模式下数据交互。

5、具体的,实装测试板上还板载有ddr内存、第一flash闪存、第二flash闪存,以及两个复位电路模块;

6、所述ddr内存和所述第一flash闪存分别和所述zynq主控芯片连接,所述第二flash闪存和所述待测芯片,且所述待测芯片和所述zynq主控芯片分别连接有复位电路模块,用于芯片的初始化;

7、其中,所述第一flash闪存中存储有dft模式和实装模式的程序,所述第二flash闪存中存储有实装模式下所述待测芯片需要运行的程序。

8、具体的,所述zynq主控芯片还连接有第一jtag接口,所述待测芯片还连接有第二jtag接口,分别用于向各自芯片烧录测试程序到对应的flash闪存中。

9、具体的,所述电源芯片模块上还连接有限流与过压保护模块,所述程控电源与所述电源芯片模块基于gpib接口连接。

10、具体的,系统测试模式通过所述上位机发出dft指令和实装指令;在dft模式下,所述zynq主控芯片通过其中的pl/fpga的并行功能,并行发起对所述待测芯片中若干电路进行扫描;在实装功能模式下,所述zynq主控芯片通过在其中的ps/arm和所述待测芯片中运行实装功能测试程序,对所述待测芯片进行实装功能测试。

11、具体的,当系统进入dft模式时,所述zynq主控芯片通过读取所述第一flash闪存中的dft扫描链程序,将其搬运到与其相连的所述ddr内存中运行,并通过所述第一总线对所述待测芯片进行dft扫描;

12、所述zynq主控芯片施加各功能模块下测试激励信号到所述待测芯片的输出引脚上,以及接收所述待测芯片输出的反馈信号;

13、所述zynq主控芯片收集并比对所述测试激励信号和反馈信号,统计错误次数和错误率,并上报统计结果到所述上位机进行数据处理和显示测试数据。

14、具体的,当系统进入实装模式时,所述zynq主控芯片通过读取所述第一flash闪存中的实装测试程序,将其搬运到与其相连的所述ddr内存中运行,并通过所述第二总线控制所述待测芯片运行实装测试程序;

15、所述zynq主控芯片与所述待测芯片进行功能交互,测试所述待测芯片在各项功能是否正常;

16、所述zynq主控芯片将各项功能的测试结果上报所述上位机进行显示和数据处理。

17、具体的,当所述上位机向所述zynq主控芯片发送dft指令或实装指令后,通过限流与过压保护模块检测和显示系统电压和电流;当系统电压或电流超过正常值时,关闭所述程控电源,并结束测试。

18、本申请实施例提供的技术方案带来的有益效果至少包括:本系统利用上位机、zynq主控芯片、程控电源和实装测试板等组成的测试系统替代了传统的ate测试板和实装测试板,同时集成了ate测试板和实装测试板的功能,通过两条总线分别作为dft模式和实装模式下进行测试和数据交互的线路,利用上位机下发指令任意控制系统的测试模式,所以测试过程无需重复装载,减少了测试周期,大大提高了测试效率。

技术特征:

1.一种芯片测试系统,其特征在于,所述系统包括上位机、程控电源、实装测试板、装载在实装测试板上的zynq主控芯片、待测芯片、电源芯片模块、和通信串口模块;

2.根据权利要求1所述的芯片测试系统,其特征在于,实装测试板上还板载有ddr内存、第一flash闪存、第二flash闪存,以及两个复位电路模块;

3.根据权利要求2所述的芯片测试系统,其特征在于,所述zynq主控芯片还连接有第一jtag接口,所述待测芯片还连接有第二jtag接口,分别用于向各自芯片烧录测试程序到对应的flash闪存中。

4.根据权利要求1所述的芯片测试系统,其特征在于,所述电源芯片模块上还连接有限流与过压保护模块,所述程控电源与所述电源芯片模块基于gpib接口连接。

5.根据权利要求1所述的芯片测试系统,其特征在于,系统测试模式通过所述上位机发出dft指令和实装指令;在dft模式下,所述zynq主控芯片通过其中的pl/fpga的并行功能,并行发起对所述待测芯片中若干电路进行扫描;在实装功能模式下,所述zynq主控芯片通过在其中的ps/arm和所述待测芯片中运行实装功能测试程序,对所述待测芯片进行实装功能测试。

6.根据权利要求2所述的芯片测试系统,其特征在于,当系统进入dft模式时,所述zynq主控芯片通过读取所述第一flash闪存中的dft扫描链程序,将其搬运到与其相连的所述ddr内存中运行,并通过所述第一总线对所述待测芯片进行dft扫描;

7.根据权利要求2所述的芯片测试系统,其特征在于,当系统进入实装模式时,所述zynq主控芯片通过读取所述第一flash闪存中的实装测试程序,将其搬运到与其相连的所述ddr内存中运行,并通过所述第二总线控制所述待测芯片运行实装测试程序;

8.根据权利要求6或7所述的芯片测试系统,其特征在于,当所述上位机向所述zynq主控芯片发送dft指令或实装指令后,通过限流与过压保护模块检测和显示系统电压和电流;当系统电压或电流超过正常值时,关闭所述程控电源,并结束测试。

技术总结

本申请公开了一种芯片测试系统,涉及芯片检测领域,系统包括上位机、程控电源、实装测试板、ZYNQ主控芯片、待测芯片、电源芯片模块和通信串口模块;ZYNQ主控芯片和待测芯片之间通过第一和第二总线连接,ZYNQ主控芯片通过通信串口模块与上位机连接;电源芯片模块通过程控电源与上位机连接,且分别连接ZYNQ主控芯片和待测芯片;上位机用于通过通信串口模块向ZYNQ主控芯片发送测试指令,控制系统进入DFT模式或实装模式,对待测芯片进行测试。本系统利用ZYNQ芯片中PL/FPGA的并行能力和PS/ARM的实装功能,集成了ATE测试板和实装测试板的功能,测试过程无需重复装载,减少了测试周期,大大提高了测试效率。

技术研发人员:请求不公布姓名

受保护的技术使用者:深存科技(无锡)有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!