进位链延时的校准方法及装置与流程

本发明实施例涉及高精度时间测量领域,具体而言,涉及一种进位链延时的校准方法及装置。

背景技术:

1、高精度时间测量是激光雷达的核心技术之一,激光雷达想到达到厘米级别的测距精度则需要达到皮秒量级的时间测量技术。使用加法进位链构成的延迟链对时钟周期进行内插的方法已被广泛使用。但这种方法存在测量误差,每个延迟单元都是不一致的,这是由fpga制造工艺决定的,因此需要对每个单元的延迟进行校准,提升测量精度。然而,相关技术中存在无法自校准进位链延时的问题。

2、针对相关技术中存在的上述问题,目前尚未提出有效的解决方案。

技术实现思路

1、本发明实施例提供了一种进位链延时的校准方法及装置,以至少解决相关技术中存在的无法自校准进位链延时的问题。

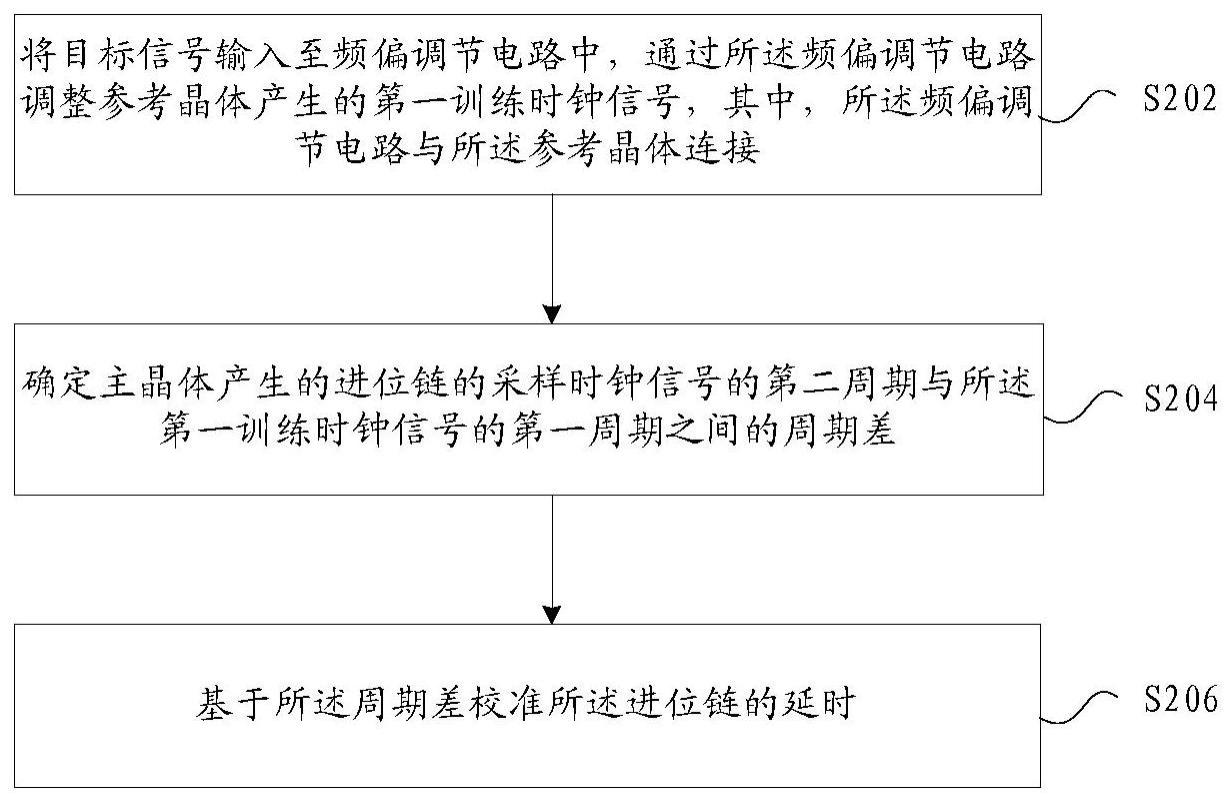

2、根据本发明的一个实施例,提供了一种进位链延时的校准方法,包括:将目标信号输入至频偏调节电路中,通过所述频偏调节电路调整参考晶体产生的第一训练时钟信号,其中,所述频偏调节电路与所述参考晶体连接;确定主晶体产生的进位链的采样时钟信号的第二周期与所述第一训练时钟信号的第一周期之间的周期差;基于所述周期差校准所述进位链的延时。

3、根据本发明的另一个实施例,提供了一种进位链延时的校准装置,用于运行上述实施例中的进位链延时的校准方法,包括:处理模块,用于将目标信号输入至频偏调节电路中;频偏调节电路,与所述处理模块的输出端连接,所述频偏调节电路还与参考晶体连接,用于将所述目标信号转换为第一电压信号转换为电容值;所述参考晶体,所述参考晶体还与所述处理模块连接,用于基于所述电容值产生第一训练时钟信号,并将所述第一训练时钟信息发送给所述处理模块;主晶体,与所述处理模块连接,用于产生进位链的采样时钟信号,并将所述采样时钟信号发送给所述处理模块;所述处理模块还用于确定主晶体输出的进位链的采样时钟信号的第二周期与所述第一训练时钟信号的第一周期之间的周期差,并基于所述周期差校准所述进位链的延时。

4、根据本发明的又一个实施例,还提供了一种计算机可读存储介质,所述计算机可读存储介质中存储有计算机程序,其中,所述计算机程序被设置为运行时执行上述任一项方法实施例中的步骤。

5、根据本发明的又一个实施例,还提供了一种电子装置,包括存储器和处理器,所述存储器中存储有计算机程序,所述处理器被设置为运行所述计算机程序以执行上述任一项方法实施例中的步骤。

6、通过本发明,将目标信号输入至与参考晶体连接的频偏调节电路中,通过频偏调节电路调整参考晶体产生的第一训练时钟信号,确定主晶体产生的进位链的采样时钟信号的第二周期与所述第一训练时钟信号的第一周期之间的周期差,根据周期差校准进位链的延时。由于可以通过频偏调节电路调整参考晶体产生的第一训练时钟信号,实现参考晶体产生的第一训练时钟信号与主晶体产生的采样时钟信号之间存在差频时钟,即周期差,利用周期差实现进位链校准测量,无需外部随机信号输入,因此,可以解决相关技术中存在的无法自校准进位链延时的问题,达到自校准进位链延迟的效果。

技术特征:

1.一种进位链延时的校准方法,其特征在于,包括:

2.根据权利要求1所述的方法,其特征在于,确定主晶体产生的进位链的采样时钟信号的第二周期与所述第一训练时钟信号的第一周期之间的周期差包括:

3.根据权利要求1所述的方法,其特征在于,基于所述周期差校准所述进位链的延时包括:

4.根据权利要求1所述的方法,其特征在于,所述方法还包括:

5.一种进位链延时的校准装置,其特征在于,用于运行权利要求1至4任一项所述的方法,包括:

6.根据权利要求5所述的进位链延时的校准装置,其特征在于,所述进位链延时的校准装置还包括:

7.根据权利要求6所述的进位链延时的校准装置,其特征在于,所述进位链延时的校准装置还包括:

8.根据权利要求7所述的进位链延时的校准装置,其特征在于,所述进位链延时的校准装置还包括:

9.根据权利要求5所述的进位链延时的校准装置,其特征在于,所述频偏调节电路包括:

10.根据权利要求9所述的进位链延时的校准装置,其特征在于,所述低通滤波器包括:第一电阻以及第一电容,所述第一电阻的第一端与所述处理模块连接,所述第一电阻的第二端与所述第一电容的第一端连接,所述第一电容的第二端接地。

11.根据权利要求9所述的进位链延时的校准装置,其特征在于,

12.根据权利要求11所述的进位链延时的校准装置,其特征在于,所述直流隔离模块包括第二电容以及第三电容,所述第二电容的第一端与所述第一变容二极管的第一端连接,所述第二电容的第二端与所述参考晶体连接,所述第三电容的第一端与所述第二变容二极管的第二端连接,所述第三电容的第二端与所述参考晶体连接。

技术总结

本发明实施例提供了一种进位链延时的校准方法及装置,其中,该方法包括:将目标信号输入至频偏调节电路中,通过频偏调节电路调整参考晶体产生的第一训练时钟信号,其中,频偏调节电路与参考晶体连接;确定主晶体产生的进位链的采样时钟信号的第二周期与第一训练时钟信号的第一周期之间的周期差;基于周期差校准进位链的延时。通过本发明,解决了相关技术中存在的无法自校准进位链延时的问题,达到自校准进位链延迟的效果。

技术研发人员:许兴玉,梅文轩,方勇军,周小勇,徐子良,吴云杰,邓志吉

受保护的技术使用者:浙江大华技术股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!