一种硅基芯片电离辐照敏感位置的识别方法与流程

本发明涉及一种硅基芯片电离辐照效应评估领域,更具体地说,它涉及一种硅基芯片电离辐照敏感位置的识别方法。

背景技术:

1、硅基芯片广泛应用于手机、电脑、家电、汽车等领域,以及航天、空间探测、卫星和核等高可靠性应用领域。但硅基芯片在遭遇到γ、x射线、电子束流等电离辐照环境时,会产生电离损伤,进而影响芯片电学性能,甚至失效,对硅基芯片在航天、空间探测、卫星和核等领域的高可靠性应用产生严重影响。随着航空航天、卫星及核领域的不断发展,对抗辐射加固集成电路的需求显著提高,对芯片的可靠性评估和抗辐射加固的要求也愈发严格。

2、硅基芯片受电离辐射影响,在场区氧化硅层、钝化层中产生电子空穴对,电子迁移率很高,被快速扫出氧化硅层或被复合;空穴迁移率低,会被氧化硅中氧空位缺陷俘获,产生氧化物电荷;同时带正电的氧空位缺陷与氢气反应,质子输运到硅-氧化硅界面产生悬挂键,即界面态。氧化物电荷和界面态影响其中晶体管的基极电流、放大倍数、输出曲线等电学特性,进而影响芯片电学性能,甚至使其失效。

3、硅基芯片内部包含大量三极管、二极管、晶闸管等结构单元,不同结构类型、不同结构尺寸、不同电路位置的晶体管对电路性能的影响不同,不同类型、不同电路结构的芯片,其内部对电离辐射敏感的位置也不相同。通过实验测试的方法识别出芯片内部对电离总剂量辐照敏感位置的结构单元,即哪种结构单元、哪个位置的结构单元在电离辐射下变化比较敏感;可以更准确的对硅基芯片的抗辐射性能进行准确评估,或者是针对性的进行电路或工艺方面的加固,无论是对硅基芯片的可靠性评估,还是对硅基芯片进行抗电离辐射总剂量加固都至关重要,也是目前亟待解决的问题。

4、因此,硅基芯片电离辐射效应敏感位置难以定位是目前急需解决的问题。

技术实现思路

1、本发明的目的是提供一种硅基芯片电离辐照敏感位置的识别方法,本发明采用微纳探针,通过辐射前后硅基芯片内的晶体管等单元结构的电学性能变化,快速识别出硅基芯片内部电离辐射敏感的结构单元类型和位置,从而实现对硅基芯片抗电离辐射性能的准确评估,为硅基芯片内敏感位置的晶体管提供针对性的电路设计加固或工艺加固。

2、本发明的上述技术目的是通过以下技术方案得以实现的:

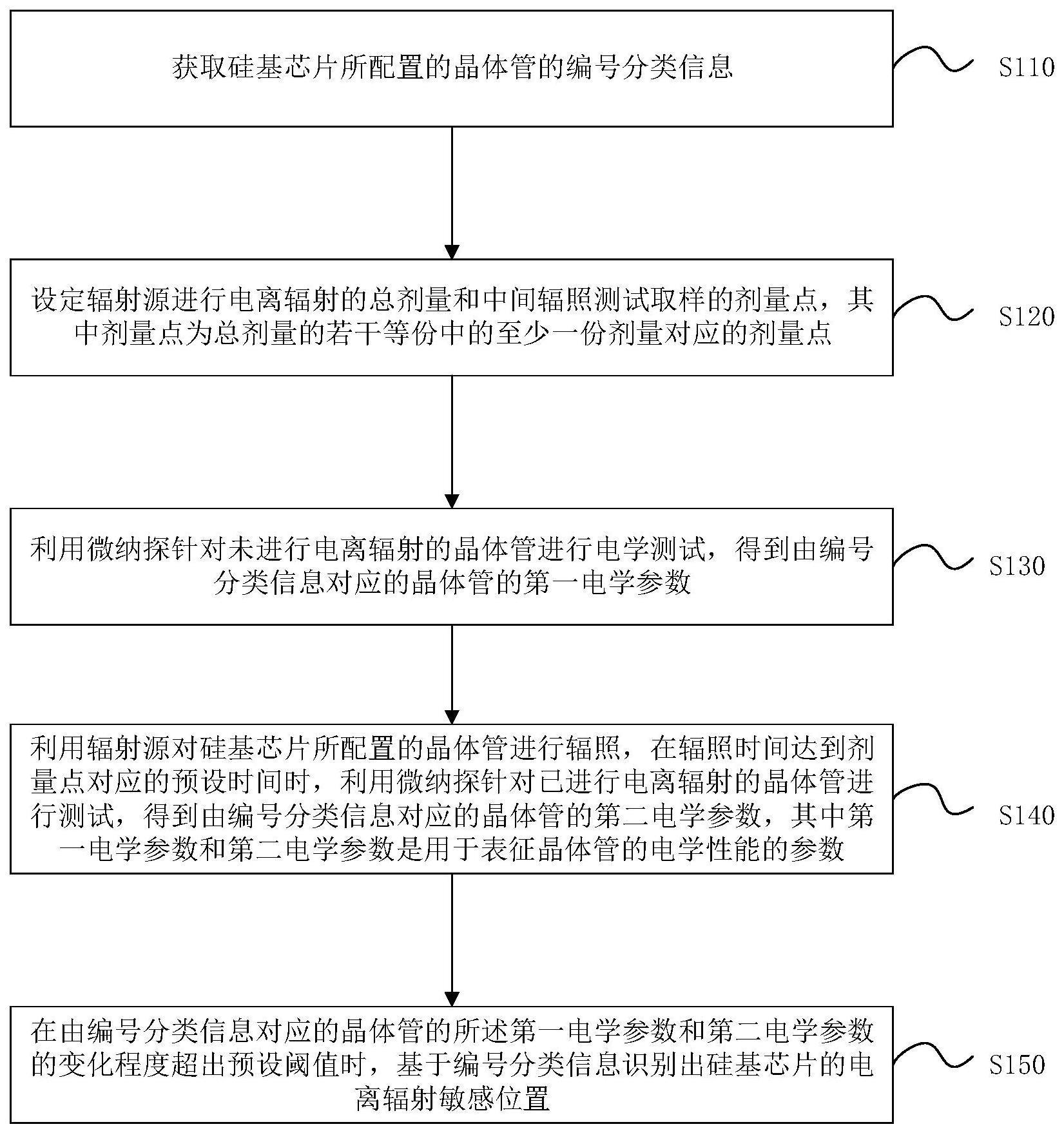

3、本申请提供了一种硅基芯片电离辐照敏感位置的识别方法,方法包括:

4、获取硅基芯片所配置的晶体管的编号分类信息;

5、设定辐射源进行电离辐射的总剂量和中间辐照测试取样的剂量点,其中剂量点为总剂量的若干等份中的至少一份剂量对应的剂量点;

6、利用微纳探针对未进行电离辐射的晶体管进行电学测试,得到由编号分类信息对应的晶体管的第一电学参数;

7、利用辐射源对硅基芯片所配置的晶体管进行辐照,在辐照时间达到剂量点对应的预设时间时,利用微纳探针对已进行电离辐射的晶体管进行测试,得到由编号分类信息对应的晶体管的第二电学参数,其中第一电学参数和第二电学参数是用于表征晶体管的电学性能的参数;

8、在由编号分类信息对应的晶体管的所述第一电学参数和第二电学参数的变化程度超出预设阈值时,基于编号分类信息识别出硅基芯片的电离辐射敏感位置。

9、在一种实施方案中,所述辐射源为x射线源、co60γ射线源两种中的任一种。

10、在一种实施方案中,所述利用微纳探针对未进行电离辐射的晶体管进行测试之前,还包括:通过干法刻蚀去除硅基芯片表面的钝化层使得,其中通过控制干法刻蚀的刻蚀气体、刻蚀功率和刻蚀时间来刻蚀硅基芯片表面的钝化层。

11、在一种实施方案中,所述晶体管包括三极管和二极管。

12、在一种实施方案中,在晶体管为三极管时,第一电学参数和第二电学参数均包括gummel电学参数、输出特性曲线以及放大倍数。

13、在一种实施方案中,在晶体管为二极管时,第一电学参数和第二电学参数均为电流-电压整流电学参数。

14、在一种实施方案中,根据辐射源标定的剂量率,利用总剂量或剂量点计算辐照时间以此判断辐照时间是否达到预设时间。

15、在一种实施方案中,方法还包括:在辐照时间达到设定的第一个剂量点对应的时间时,对晶体管的第二电学参数进行失效判断,若存在失效情况,则将最先失效的编号分类信息对应的晶体管确定为硅基芯片内电离辐射敏感位置,且不需对后续设定的剂量点进行辐照测试。

16、在一种实施方案中,若不存在失效情况,按照设定的剂量点对硅基芯片所配置的晶体管进行辐照,重复辐照和微纳探针的测试过程,直至辐射剂量达到设定的总剂量,或硅基芯片内的晶体管失效。

17、在一种实施方案中,所述微纳探针为显微镜或扫描电子显微镜所配置的微纳探针。

18、与现有技术相比,本发明具有以下有益效果:

19、本发明采用微纳探针,通过辐射前后硅基芯片内的晶体管等单元结构的电学性能变化,快速识别出硅基芯片内部电离辐射敏感的结构单元类型和位置,从而实现对硅基芯片抗电离辐射性能的准确评估,为硅基芯片内敏感位置的晶体管提供针对性的电路设计加固或工艺加固。

技术特征:

1.一种硅基芯片电离辐照敏感位置的识别方法,其特征在于,方法包括:

2.根据权利要求1所述的一种硅基芯片电离辐照敏感位置的识别方法,其特征在于,所述辐射源为x射线源、co60γ射线源两种中的任一种。

3.根据权利要求1所述的一种硅基芯片电离辐照敏感位置的识别方法,其特征在于,所述利用微纳探针对未进行电离辐射的晶体管进行测试之前,还包括:通过干法刻蚀去除硅基芯片表面的钝化层使得晶体管电极裸露出来,其中通过控制干法刻蚀的刻蚀气体、刻蚀功率和刻蚀时间来刻蚀硅基芯片表面的钝化层。

4.根据权利要求1所述的一种硅基芯片电离辐照敏感位置的识别方法,其特征在于,所述晶体管包括三极管和二极管。

5.根据权利要求4所述的一种硅基芯片电离辐照敏感位置的识别方法,其特征在于,在晶体管为三极管时,第一电学参数和第二电学参数均包括gummel电学参数、输出特性曲线以及放大倍数。

6.根据权利要求4所述的一种硅基芯片电离辐照敏感位置的识别方法,其特征在于,在晶体管为二极管时,第一电学参数和第二电学参数均为电流-电压整流电学参数。

7.根据权利要求1所述的一种硅基芯片电离辐照敏感位置的识别方法,其特征在于,根据辐射源标定的剂量率,利用总剂量或剂量点计算辐照时间以此判断辐照时间是否达到预设时间。

8.根据权利要求1所述的一种硅基芯片电离辐照敏感位置的识别方法,其特征在于,方法还包括:在辐照时间达到设定的第一个剂量点对应的时间时,对晶体管的第二电学参数进行失效判断,若存在失效情况,则将最先失效的编号分类信息对应的晶体管确定为硅基芯片内电离辐射敏感位置,且不需对后续设定的剂量点进行辐照测试。

9.根据权利要求8所述的一种硅基芯片电离辐照敏感位置的识别方法,其特征在于,若不存在失效情况,按照设定的剂量点对硅基芯片所配置的晶体管进行辐照,重复辐照和微纳探针的测试过程,直至辐射剂量达到设定的总剂量,或硅基芯片内的晶体管失效。

10.根据权利要求1所述的一种硅基芯片电离辐照敏感位置的识别方法,其特征在于,所述微纳探针为显微镜或扫描电子显微镜所配置的微纳探针。

技术总结

本发明公开了一种硅基芯片电离辐照敏感位置的识别方法,涉及电离辐照效应评估领域,获取硅基芯片所配置的晶体管的编号分类信息;设定辐射源进行电离辐射的总剂量和中间辐照测试取样的剂量点;利用微纳探针对未进行电离辐射的晶体管进行电学测试,得到由编号分类信息对应的晶体管的第一电学参数;利用辐射源对硅基芯片所配置的晶体管进行辐照,在辐照时间达到剂量点对应的预设时间时,利用微纳探针对已进行电离辐射的晶体管进行测试,得到由编号分类信息对应的晶体管的第二电学参数;在由编号分类信息对应的晶体管的第一电学参数和第二电学参数的变化程度超出预设阈值时,基于编号分类信息识别出硅基芯片的电离辐射敏感位置。

技术研发人员:张光辉,杨萍,刘杨,周航,孟德超

受保护的技术使用者:中国工程物理研究院电子工程研究所

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!