一种测试芯片内部电源的瞬态响应的方法和控制系统与流程

本申请涉及芯片的,更具体地,涉及一种测试芯片内部电源的瞬态响应的方法和控制系统。

背景技术:

1、为了确保芯片内部电源在负载变化较快的时候依旧能正常工作,需要测试电源的瞬态响应。一般的测试方法为给电源一个短时间内功耗变化大的激励,看电源能否长时间保持正常工作。目前常用的测试内部电源的瞬态响应的方式为:芯片外接一个电子负载产生装置,通过电子负载产生装置产生所需变化较快的负载,然后通过示波器观测电源输出vout的变化进行电源的瞬态测试。但是这种需要额外设备支持的测试方法中,可能为了节约引脚资源,有些芯片不一定将电源输出引出,而且这种电子负载的方式可能无法真实地模拟出芯片负载变化的真实情况,所以这种方式可能无法得到芯片内部电源的真实瞬态响应。

技术实现思路

1、提供了本申请以解决现有技术中存在的上述缺陷。需要一种测试芯片内部电源的瞬态响应的方法和控制系统,无需外接电子负载,充分利用芯片内的构件,以较低的改造成本,就能够方便地实现短时间内的较大负载变化,从而得到芯片内部电源对此的真实瞬态响应。

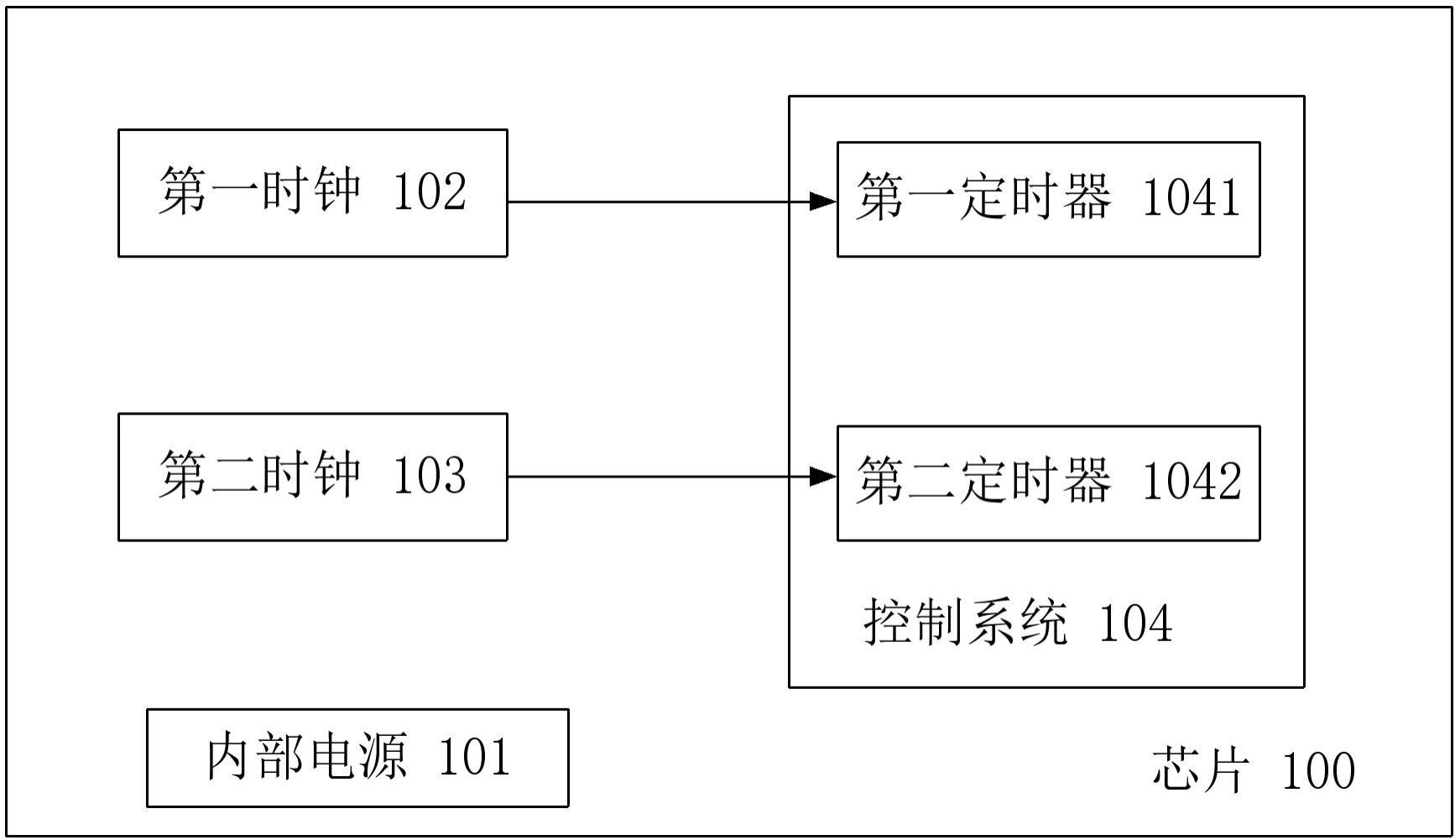

2、根据本申请的第一方案,提供了一种用于芯片的控制系统,所述芯片包括内部电源、第一时钟和第二时钟,所述控制系统包括:第一定时器,其以所述第一时钟作为工作时钟,且配置为以持续方式,交替地输出使得所述芯片休眠的第一休眠信号和使得所述芯片唤醒的第一唤醒信号;以及第二定时器,其以所述第二时钟作为工作时钟,所述第二时钟和所述第一时钟为异步时钟,且配置为以持续方式,交替地输出使得所述芯片休眠的第二休眠信号和使得所述芯片唤醒的第二唤醒信号;基于所述第一休眠信号、第一唤醒信号、第二休眠信号和第二唤醒信号,使得所述芯片在至少一次休眠后在小于所述第一时钟或第二时钟的一个时钟周期的第一时间段内被唤醒。

3、根据本申请的第二方案,提供了一种测试芯片内部电源的瞬态响应的方法,所述芯片包括内部电源、第一时钟和第二时钟,所述第二时钟和所述第一时钟为异步时钟,所述方法包括:以所述第一时钟作为工作时钟,以持续方式交替地输出使得所述芯片休眠的第一休眠信号和使得所述芯片唤醒的第一唤醒信号;以所述第二时钟作为工作时钟,以持续方式交替地输出使得所述芯片休眠的第二休眠信号和使得所述芯片唤醒的第二唤醒信号;基于所述第一休眠信号、第一唤醒信号、第二休眠信号和第二唤醒信号,使得所述芯片在至少一次休眠后在小于所述第一时钟或第二时钟的一个时钟周期的第一时间段内被唤醒。

4、本申请各个实施例提供的测试芯片内部电源的瞬态响应的方法和控制系统,充分利用了芯片内设置的第一时钟和第二时钟。第一定时器和第二定时器分别以第一时钟和第二时钟为工作时钟,第一时钟和第二时钟为异步时钟,使得第一定时器和第二定时器分别可以异步交替输出唤醒信号和休眠信号,这样能够使芯片出现在至少一次休眠后在小于任一时钟的一个时钟周期的第一时间段内被唤醒的情况,促使芯片在瞬时的休眠到唤醒的激励下产生短时间内的较大负载变化,进而得到芯片内部电源对此的真实瞬态响应,然后通过这种瞬态响应下的芯片内部电源的实际情况,能够更准确地得到芯片内部电源在负载变化较快的时候是否能够依旧正常工作。

技术特征:

1. 一种用于芯片的控制系统,其特征在于,所述芯片包括内部电源、第一时钟和第二时钟,所述控制系统包括:

2.根据权利要求1所述的控制系统,其特征在于,所述第一时钟或第二时钟存在时钟周期和/或占空比的波动。

3.根据权利要求1或2所述的控制系统,其特征在于,所述芯片在至少一次休眠后在小于所述第一时钟或第二时钟的一个时钟周期的时间段内被唤醒后的第二时间段内,所述芯片的内部电源的输出电压低于所述内部电源额定电压的最小值。

4.根据权利要求3所述的控制系统,其特征在于,在所述第二时间段之后的第三时间段内,所述芯片的内部电源的输出电压处于所述内部电源的额定电压范围内。

5.根据权利要求1或2所述的控制系统,其特征在于,在芯片的至少一次休眠到被唤醒之间的第一时间段小于所述第一时钟或第二时钟的一个时钟周期的0.1%。

6.根据权利要求1或2所述的控制系统,其特征在于,所述第二定时器对于所述第二休眠信号的定时计数值与所述第一定时器对于所述第一唤醒信号的定时计数值的偏差在第一阈值范围内,所述所述第二定时器对于所述第二唤醒信号的定时计数值与所述第一定时器对于所述第一休眠信号的定时计数值的偏差在第二阈值范围内,所述第一阈值范围和第二阈值范围小于所述第一时钟或第二时钟的时钟周期。

7.根据权利要求6所述的控制系统,其特征在于,所述第一阈值范围为1-3,所述第二阈值范围为10-100。

8.根据权利要求6所述的控制系统,其特征在于,所述第一定时器和所述第二定时器均设置为输出比较模式,且配置为:

9.根据权利要求8所述的控制系统,其特征在于,所述中断标志位表示下降沿或上升沿。

10.根据权利要求1或2所述的控制系统,其特征在于,所述至少一次休眠及其后在所述时间段内的唤醒为第一休眠信号作用下的休眠和所述第二唤醒信号作用下的唤醒,和/或所述第二休眠信号作用下的休眠和所述第一唤醒信号作用下的唤醒。

11.一种测试芯片内部电源的瞬态响应的方法,其特征在于,所述芯片包括内部电源、第一时钟和第二时钟,所述第二时钟和所述第一时钟为异步时钟,所述方法包括:

12.根据权利要求11所述的方法,其特征在于,所述第一时钟或第二时钟存在时钟周期和/或占空比的波动。

13.根据权利要求11所述的方法,其特征在于,所述芯片在至少一次休眠后在小于所述第一时钟或第二时钟的一个时钟周期的时间段内被唤醒后的第二时间段内,所述芯片的内部电源的输出电压低于所述内部电源额定电压的最小值。

14.根据权利要求11所述的方法,其特征在于,在所述第二时间段之后的第三时间段内,所述芯片的内部电源的输出电压处于所述内部电源的额定电压范围内。

15.根据权利要求11所述的方法,其特征在于,在芯片的至少一次休眠到被唤醒之间的第一时间段小于所述第一时钟或第二时钟的的一个时钟周期的0.1%。

16.根据权利要求11所述的方法,其特征在于,还包括:

17.根据权利要求16所述的方法,其特征在于,所述第一阈值范围为1-3,所述第二阈值范围为10-100。

18.根据权利要求16所述的方法,其特征在于,所述第一定时器和所述第二定时器均设置为输出比较模式:

19.根据权利要求18所述的方法,其特征在于,所述中断标志位表示下降沿或上升沿。

20.根据权利要求11所述的方法,其特征在于,所述至少一次休眠及其后在所述时间段内的唤醒为第一休眠信号作用下的休眠和所述第二唤醒信号作用下的唤醒,和/或所述第二休眠信号作用下的休眠和所述第一唤醒信号作用下的唤醒。

技术总结

本申请涉及一种测试芯片内部电源的瞬态响应的方法和控制系统,芯片包括内部电源、第一时钟和第二时钟,控制系统包括:第一定时器,以第一时钟作为工作时钟,配置为以持续方式,交替地输出使得芯片休眠的第一休眠信号和使得芯片唤醒的第一唤醒信号;第二定时器,以第二时钟作为工作时钟,第二时钟和第一时钟为异步时钟,配置为以持续方式,交替地输出使得芯片休眠的第二休眠信号和使得芯片唤醒的第二唤醒信号;基于第一休眠信号、第一唤醒信号、第二休眠信号和第二唤醒信号,使得芯片在至少一次休眠后在小于第一时钟或第二时钟的一个时钟周期的第一时间段内被唤醒,因此该控制系统能够使芯片在瞬时的休眠到唤醒的激励下产生真实的瞬态响应。

技术研发人员:胡登极

受保护的技术使用者:南京芯驰半导体科技有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!