一种实现高速切换的收发电路的制作方法

本申请涉及雷达,尤其是涉及一种实现高速切换的收发电路。

背景技术:

1、相控阵雷达中收发电路通常采用分时体制,当收发电路接收信号时,会关闭发射通道放大器的电源;当收发电路发射信号时,会关闭接收通道放大器的电源,以此来提高接收通道和发射通道之间的隔离度;否则,很容易引起收发电路环路自激,导致收发电路乃至雷达系统不能正常工作。

2、关闭收发电路中放大器的电源,需要对放大器的漏极或栅极进行调制,来实现放大器漏极或栅极工作电压的开启和关断。通常,对放大器进行漏极调制方案,是在漏极电源通路上引入功率pmos调制开关电路,对放大器进行栅极调制方案,是在栅极电源通路上引入ttl驱动电路。这里,pmos是指n型衬底、p沟道,靠空穴的流动运送电流的mos管。ttl(transistor-transistor-logic)驱动电路是一种晶体管-晶体管逻辑电路,属于数字集成电路的一大门类,采用双极型工艺制造,具有高速度和品种多等特点。

3、目前,相控阵雷达的收发电路中常用漏极调制方案电路如附图1所示,是放大器正常工作时的栅极电源,是放大器正常工作时的漏极电源,是控制功率pmos晶体管的使能电源;通过切换电压来控制功率pmos晶体管的开启与关断,当功率pmos晶体管关断时,与放大器断开,放大器停止工作;当功率pmos晶体管开启时,与放大器连接,放大器开始工作。

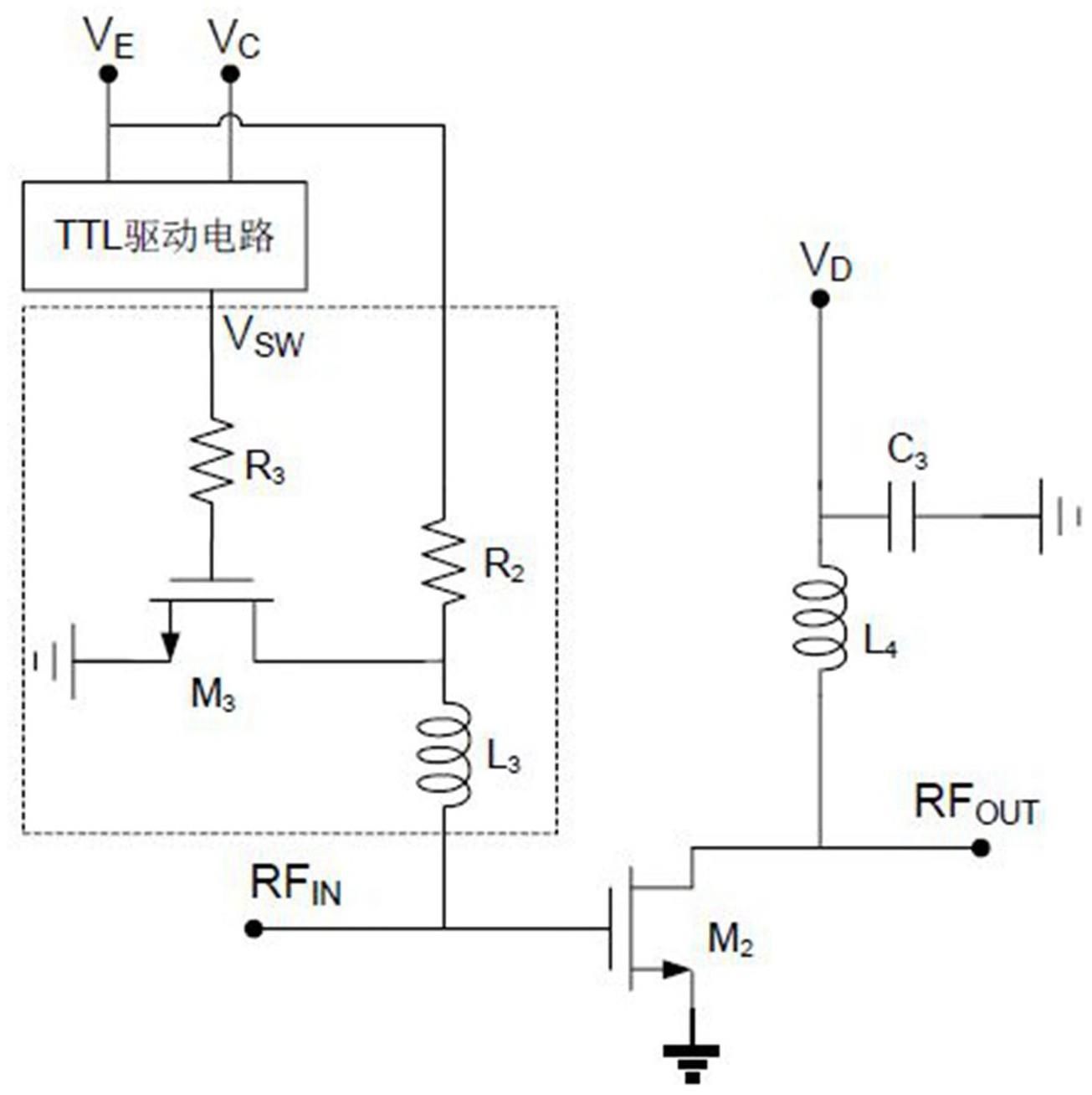

4、相控阵雷达的收发电路中常用栅极调制方案电路如附图2所示,是放大器正常工作时的栅极电源,是放大器正常工作时的漏极电源,是ttl驱动电路的外部电源,是ttl驱动电路的控制电源;通过控制电压,使得在高低电平间切换,当为低电平时,放大器停止工作,为高电平时,放大器开始工作。

5、常规收发电路中的放大器拓扑结构如附图3所示,包括晶体管、栅极偏置电路和漏极偏置电路;其中,栅极偏置电路由电阻、电感和电容组成;栅极偏置电路一端与晶体管的栅极连接,同时连接至射频信号输入端,栅极偏置电路另一端连接栅极电源;漏极偏置电路由电感和电容组成;漏极偏置电路一端与晶体管的漏极连接,同时晶体管的漏极连接至射频信号输出端,漏极偏置电路另一端连接漏极电源。

6、综合漏极调制方案电路、栅极调制方案电路以及放大器拓扑结构电路可知,栅极调制方案的收发切换时间主要受ttl驱动电路、电阻和电容的影响,漏极调制方案的收发切换时间主要受功率pmos晶体管和电容的影响。电路中的时间常数τ表示过渡反应的时间过程常数,在电阻、电容的电路中τ是电阻和电容的乘积:。若电容c的单位是uf(微法),电阻r的单位是mω(毫欧),时间常数τ的单位是秒。若要减小时间常数τ,可以从减小电阻r或电容c入手。

7、常规收发电路中放大器拓扑结构中电阻r在100~1000ω之间,电容在1~10pf之间,则时间常数τ在100~10000ns之间。在相控阵雷达某些要求收发切换时间≤40ns的应用场景下,现有常规技术无法达到要求。

技术实现思路

1、为了实现相控阵雷达中收发电路的收发高速切换,本申请提供了一种实现高速切换的收发电路。

2、本申请提出了一种实现高速切换的收发电路,收发电路中放大器的栅极电源通路上设置栅极调制电路;所述收发电路的结构包括栅极调制电路、晶体管和漏极偏置电路;其中,所述栅极调制电路包含一调制模块,用于快速切换放大器栅极工作电压的开启或关断;所述栅极调制电路一端与晶体管的栅极连接,同时连接至射频信号输入端,所述栅极调制电路的另一端连接至外部电源;晶体管的源极接地;晶体管的漏极与漏极偏置电路一端连接,同时连接至射频信号输出端;漏极偏置电路另一端连接至漏极电源。

3、优选的,所述栅极调制电路还包括电阻和电感;其中,所述调制模块一端连接至外部控制电源;所述调制模块另一端与电阻一端连接,同时与电感一端连接,电阻另一端连接至外部电源;电感另一端与晶体管的栅极连接,同时连接至射频信号输入端。

4、优选的,所述栅极调制电路中调制模块的结构包括晶体管和电阻;栅极调制电路中,电阻一端连接至外部控制电源,电阻另一端与晶体管的栅极连接;晶体管的源极接地,晶体管的漏极与电阻连接,电阻另一端连接至外部电源;

5、同时晶体管的漏极与电感一端连接;电感另一端与晶体管的栅极连接,同时连接至射频信号输入端。

6、优选的,所述漏极偏置电路的结构包括电容和电感,电感一端与晶体管的漏极连接;电感另一端接入栅极电源,同时与电容一端连接;电容另一端接地。

7、优选的,所述栅极调制电路一端增加设置一个ttl驱动电路,用于缩小所述收发电路的收发切换时间。

8、优选的,所述ttl驱动电路连接至外部电源和外部控制电源;ttl驱动电路的输出端与电阻一端连接,向电阻提供控制电源,电阻一端连接至外部电源。

9、优选的,所述外部控制电源在高/低电之间切换,所述ttl驱动电路的输出电压相应的在高/低电平之间切换。

10、优选的,所述ttl驱动电路的输出电压切换至低电平,晶体管截止;外部电源的电源电压通过电阻和电感输入到晶体管的栅极,导致晶体管截止,此时放大器关断;

11、所述ttl驱动电路的输出电压切换至高电平,晶体管导通;晶体管的栅极通过电感和晶体管接地,导致晶体管导通,此时放大器开启。

12、优选的,所述晶体管采用hemt或mesfet类型的放大晶体管。

13、优选的,所述晶体管采用fet类型的开关晶体管。

14、综上所述,本申请实现高速切换的收发电路具有如下有益效果:通过在放大器的栅极电源通路上设置栅极调制电路,同时增设ttl驱动电路,实现快速切换放大器栅极工作电压的开启或关断;解决了常规放大器栅极或漏极调制方案用时较长的问题;

15、放大器的栅极调制电路的响应时间可以控制在30ns以内,满足收发电路切换时间≤40ns的应用场景下,克服了现有常规技术无法解决的技术问题,填补行业技术空白,具有显著的进步性;

16、实现对相控阵雷达收发电路中放大器的高速调制,显著提高了相控阵雷达收发电路的切换速度;有效提高相控阵雷达探测目标时的分辨率;并且电路结构设计简单,实现方便,在行业应用中具有很好的实用性。

技术特征:

1.一种实现高速切换的收发电路,在收发电路的放大器的栅极电源通路上设置栅极调制电路,其特征在于:所述收发电路的结构包括栅极调制电路、晶体管和漏极偏置电路;其中,所述栅极调制电路包含一调制模块,用于快速切换放大器栅极工作电压的开启或关断;

2.根据权利要求1所述收发电路,其特征在于:所述漏极偏置电路的结构包括电容和电感;所述电感一端与所述晶体管的漏极连接;所述电感另一端接入栅极电源,同时与电容一端连接;所述电容另一端接地。

3.根据权利要求2所述收发电路,其特征在于:所述栅极调制电路还包括电阻和电感;其中,所述调制模块一端连接至外部控制电源;所述调制模块另一端与电阻一端连接,同时与电感一端连接,所述电阻另一端连接至外部电源;所述电感另一端与所述晶体管的栅极连接,同时连接至射频信号输入端。

4.根据权利要求3所述收发电路,其特征在于:所述栅极调制电路中调制模块的结构包括晶体管和电阻;所述电阻一端连接至外部控制电源,电阻另一端与晶体管的栅极连接;所述晶体管的源极接地,所述晶体管的漏极与电阻连接,所述电阻另一端连接至外部电源;

5.根据权利要求4所述收发电路,其特征在于:所述栅极调制电路一端增加设置一个ttl驱动电路,用于缩小所述收发电路的收发切换时间。

6.根据权利要求5所述收发电路,其特征在于:所述ttl驱动电路连接至外部电源和外部控制电源;所述ttl驱动电路的输出端与所述电阻一端连接,向电阻提供控制电源,所述电阻一端连接至所述外部电源。

7.根据权利要求6所述收发电路,其特征在于:所述外部控制电源在高/低电之间切换时,所述ttl驱动电路的输出电压相应的在高/低电平之间切换。

8.根据权利要求7所述收发电路,其特征在于:所述ttl驱动电路的输出电压切换至低电平,所述晶体管截止;所述外部电源的电源电压通过电阻和电感输入到晶体管的栅极,导致所述晶体管截止,则放大器关断;

9.根据权利要求1至8任一所述收发电路,其特征在于:所述晶体管采用hemt或mesfet类型的放大晶体管。

10.根据权利要求3至8任一所述收发电路,其特征在于:所述栅极调制电路中晶体管采用fet类型的开关晶体管。

技术总结

本申请提出一种实现高速切换的收发电路,收发电路中放大器的栅极电源通路上设置栅极调制电路,栅极调制电路设置一调制模块,能够快速切换放大器栅极工作电压的开启或关断;该收发电路还包括晶体管和漏极偏置电路;栅极调制电路一端与晶体管的栅极连接,另一端连接至外部电源;晶体管的源极接地;晶体管的漏极与漏极偏置电路一端连接,漏极偏置电路另一端连接至漏极电源。本申请解决了常规放大器栅极或漏极调制方案用时较长的问题;实现对相控阵雷达收发电路中放大器的高速调制,显著提高了相控阵雷达收发电路的切换速度;有效提高相控阵雷达探测目标时的分辨率;电路结构相对简单,具有很好的实用性。

技术研发人员:杨洲,黄华,陈普锋,全金海

受保护的技术使用者:中科海高(成都)电子技术有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!