闩锁效应的测试结构以及测试方法与流程

本发明涉及半导体测试领域,尤其涉及一种闩锁效应的测试结构以及测试方法。

背景技术:

1、闩锁效应(latch-up)广泛存在于cmos电路中,特别是器件中存在pnpn结构时,由于电源信号波动或者静电放电导致的浪涌电流出现时,很容易触发闩锁效应,严重时可能烧毁芯片。闩锁效应发生在i/o区域的风险较大,内部偶尔也有出现。随着工艺制成不断发展,器件的特征尺寸和间距不断减小,进一步增加了触发闩锁效应的风险。所以合理设计器件的结构尺寸,增大芯片抗闩锁效应的能力就显得尤为重要。

2、附图1a所示是现有技术中一种发生在cmos中的pnpn闩锁结构,附图1b所示是附图1a的闩锁结构的等效电路图。参考附图1a和附图1b所示,硅基pn结导通压降的典型值是0.6v-0.7v。当浪涌电流经过衬底寄生电阻rp产生的电压大于0.6v时,nmos源极,p阱和n阱形成的npn寄生晶体管发射结正偏,集电结反偏,器件导通。vdd与vss之间形成通路,电流流过rn,形成的压降大于0.6v时,pmos源极,n阱和p阱形成的寄生的pnp晶体管导通,npn和pnp形成一个闭环的正反馈低阻通路,触发闩锁效应。

3、但实际情况中并非只有出现pnpn结构才会出现闩锁效应,单管nmos和pmos寄生的npn或pnp结构也可能触发闩锁效应。附图2a所示是现有技术中一种nmos单管中npn闩锁结构示意图,附图2b所示是附图2a的闩锁结构的等效电路图。当电源vdd或者vss波动出现的浪涌电流经过p阱电阻rp时,寄生npn晶体管发射结两端会产生电压降。当该压降大于0.6v时,寄生的npn晶体管发射结正偏,集电极反偏,npn晶体管导通,与电阻rp形成正反馈通路,从而触发npn闩锁。pmos的情况与其类似,此处从略。当电路局部出现单管nmos或者pmos器件时,也需要要合理设置器件的结构和尺寸,降低其触发闩锁效应的风险,然而晶圆加工过程中对于单管npn或pnp结构触发闩锁效应及其器件结构的影响监控方法较少。

技术实现思路

1、本发明所要解决的技术问题是,提供一种闩锁效应的测试结构以及测试方法,针对单管npn或pnp闩锁效应进行评估性测试。

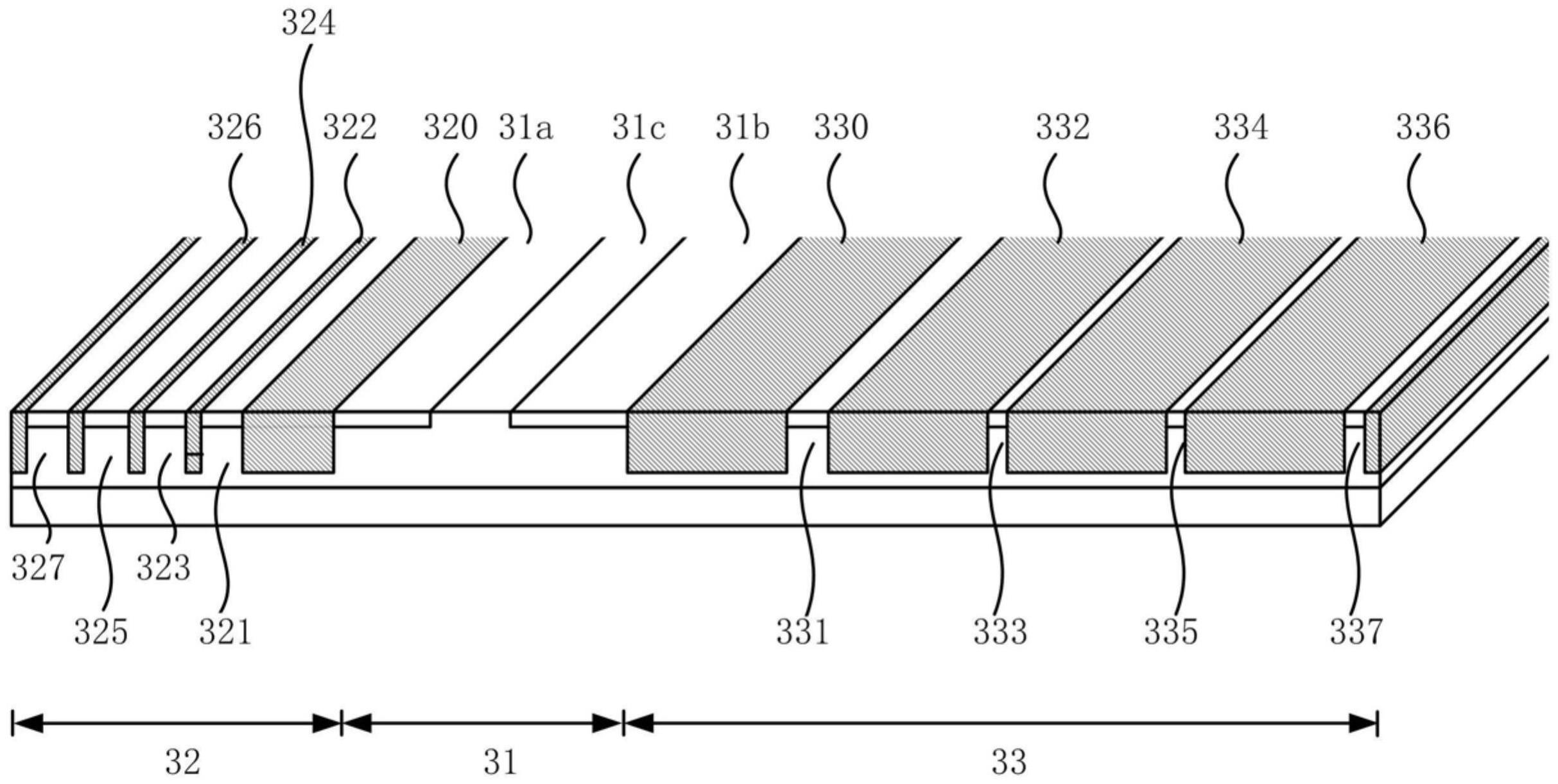

2、为了解决上述问题,本发明提供了一种闩锁效应的测试结构,包括:mos晶体管,所述mos晶体管的源区和漏区具有第一导电类型;闩锁效应测试模块,所述闩锁效应测试模块包括多个具有第二导电类型的反型区,且不同的反型区之间通过介质隔离区相互分隔。

3、可选的,所述闩锁效应测试模块包括反型区宽度测试单元和介质隔离区宽度测试单元中的至少一种:所述反型区宽度测试单元中的多个反型区的宽度相同;所述介质隔离区宽度测试单元的多个介质隔离区的宽度相同。

4、为了解决上述问题,本发明提供了一种闩锁效应的测试方法,包括如下步骤:提供一测试结构,所述测试结构包括mos晶体管以及反型区宽度测试单元,所述mos晶体管的源区和漏区具有第一导电类型;所述反型区宽度测试单元包括多个具有第二导电类型的反型区;选取第一数量的第二导电类型的反型区,同mos晶体管的源区或漏区电学并联;以及选取第二数量的第二导电类型的反型区,同mos晶体管的源区或漏区电学并联,以测试不同宽度的反型区对闩锁失效的影响。

5、为了解决上述问题,本发明提供了一种闩锁效应的测试方法,包括如下步骤:提供一测试结构,所述测试结构包括mos晶体管以及反型区宽度测试单元,所述mos晶体管的源区和漏区具有第一导电类型,所述介质隔离区宽度测试单元包括多个介质隔离区;选取第一位置的第二导电类型的反型区,同mos晶体管的源区或漏区电学并联;以及选取第二位置的第二导电类型的反型区,同mos晶体管的源区或漏区电学并联,以测试不同宽度的介质隔离区对闩锁失效的影响。

6、上述技术方案能够评估连接阱区的p+宽度(nmos)或n+宽度(pmos)以及介质隔离区的宽度对闩锁效应的影响,对工艺监测和设计规则提供参考。

7、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本申请。对于相关领域普通技术人员已知的技术、方法和设备可能不作详细讨论,但在适当情况下,所述技术、方法和设备应当被视为授权说明书的一部分。

技术特征:

1.一种闩锁效应的测试结构,其特征在于,包括:

2.根据权利要求1所述的结构,其特征在于,所述闩锁效应测试模块包括反型区宽度测试单元和介质隔离区宽度测试单元中的至少一种:

3.根据权利要求2所述的结构,其特征在于,反型区宽度测试单元中的反型区的宽度大于介质隔离区宽度测试单元中反型区的宽度。

4.根据权利要求2所述的结构,其特征在于,介质隔离区宽度测试单元中的介质隔离区的宽度大于反型区宽度测试单元中介质隔离区的宽度。

5.根据权利要求1所述的结构,其特征在于,所述第一导电类型为n型,所述第二导电类型为p型;或所述第一导电类型为p型,所述第二导电类型为n型。

6.一种闩锁效应的测试方法,其特征在于,包括如下步骤:

7.一种闩锁效应的测试方法,其特征在于,包括如下步骤:

技术总结

本发明提供一种闩锁效应的测试结构以及测试方法。所述结构包括:MOS晶体管,所述MOS晶体管的源区和漏区具有第一导电类型;闩锁效应测试模块,所述闩锁效应测试模块包括多个具有第二导电类型的反型区,且不同的反型区之间通过介质隔离区相互分隔。上述技术方案能够评估连接阱区的P+宽度或N+宽度以及介质隔离区的宽度对闩锁效应的影响,对工艺监测和设计规则提供参考。

技术研发人员:李东洁,朱钰,贾威,蒲义

受保护的技术使用者:上海积塔半导体有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!