芯片、芯片的输入输出多态检测方法及相关设备与流程

本发明适用于芯片多态检测,尤其涉及一种芯片、芯片的多态检测方法、计算机设备及计算机可读存储介质。

背景技术:

1、在芯片的方案应用中,会需要芯片有不同的参数配置。有主控的方案可以在主控中写不同的软件,让主控通过通信接口来配置芯片的不同参数。在没有主控的方案上,每种参数配置都使用一个新的芯片料号,会给原厂和方案厂商带来极大的管理负担。因此,在芯片内部内置多套参数,让客户可以通过在设计pcb时给予gpio不同输入来选择不同的参数配置,成为一种主流做法。

2、相关技术的芯片包括比较器、逻辑单元、上拉电阻及下拉电阻;通过芯片可以识别io口是上拉还是下拉,在上拉电阻和下拉电阻都不接的时候,芯片也可以识别出浮空。

3、然而,相关技术的芯片在两态识别时只有两种输入,可配置数量少,对于多配置组合来说不够用;三态识别输入数量稍多,但是在vio偏差时容易造成识别错误;当增加到五种状态,数量有增加但还是不够多,且需要两个比较器,更加占用资源。

技术实现思路

1、本发明提供一种芯片、芯片的多态检测方法及相关设备,旨在解决现有技术对于芯片的多态检测方法状态识别数量少、占用资源及检测精度低的技术问题。

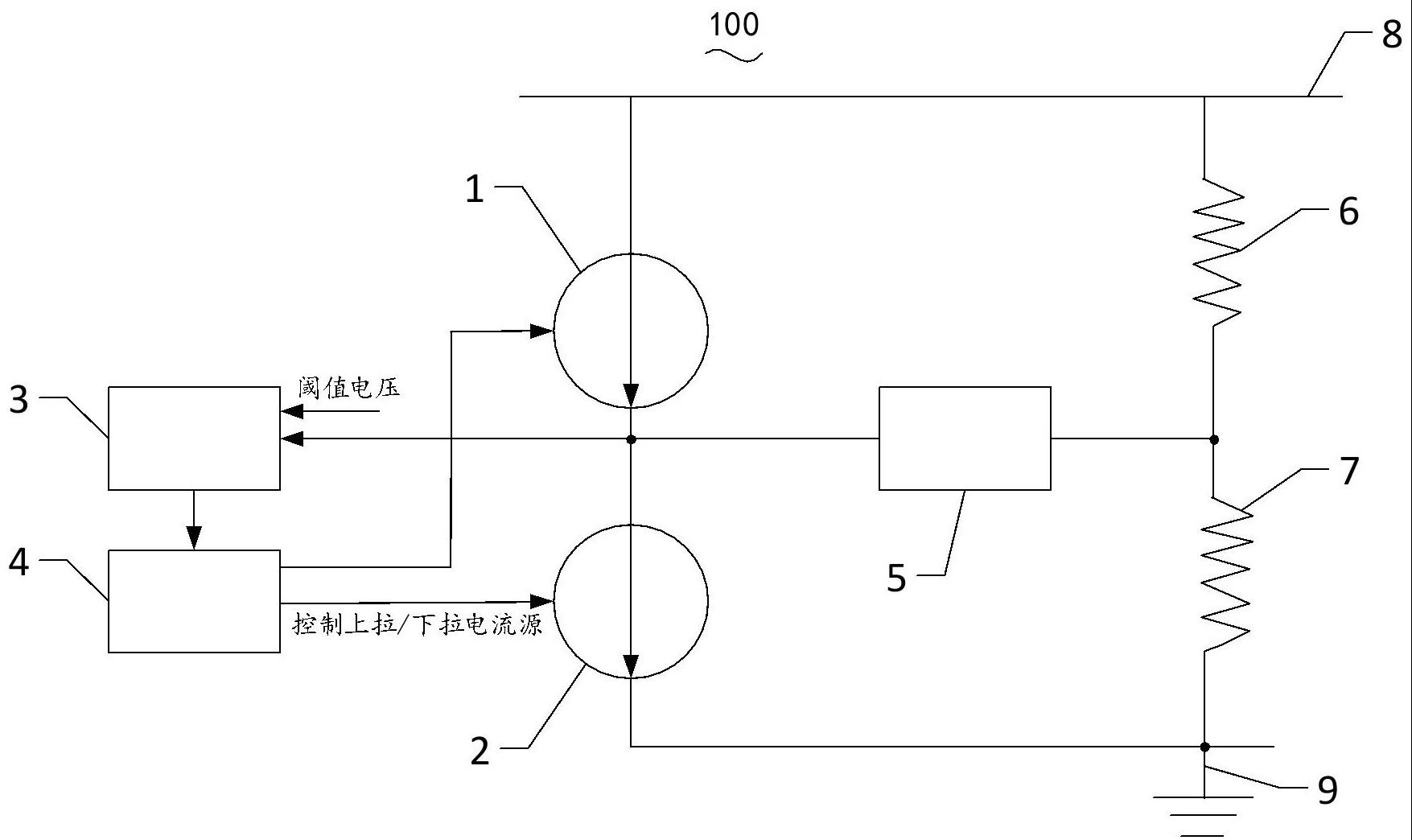

2、第一方面,本发明实施例提供一种芯片,所述芯片包括用于连接外部电源的电源端及用于接地的接地端,所述芯片还包括可调上拉电流源、可调下拉电流源、比较器、逻辑控制单元以及io口;

3、所述io口用于连接一个电阻节点,所述电阻节点为按顺序串接在所述外部电源与地之间的外部上拉电阻及外部下拉电阻的连接点;

4、所述可调上拉电流源设有对应不同电流值的至少两个档位,所述可调上拉电流源的正负极分别连接至所述电源端及所述io口,用于使不同电流值的电流流过所述外部下拉电阻,以在所述io口得到对应的第一电压;

5、所述可调下拉电流源设有对应不同电流值的至少两个档位,所述可调下拉电流源的正负极分别连接至所述io口及地,用于使不同电流值的电流流过所述外部上拉电阻,以在所述io口得到对应的第二电压;

6、所述比较器的第一输入端连接至所述io口,所述比较器的第二输入端连接至一个预设阈值电压,所述比较器的输出端连接至所述逻辑控制端元;所述比较器用于将所述第一电压和所述第二电压分别与所述预设阈值电压进行比较,并将电压比较结果输出至所述逻辑控制单元;

7、所述逻辑控制单元用于分别控制所述可调上拉电流源和所述可调下拉电流源的开与关以及输出的电流大小,并结合所述电压比较结果,判断外部电阻是上拉状态还是下拉状态,以及上拉状态或下接状态时的电阻阻值。

8、优选的,所述逻辑控制单元还用于控制所述可调下拉电流源关闭,控制所述可调上拉电流源输出最小档位电流,获得所述比较器的第一结果;

9、所述逻辑控制单元还用于控制所述可调上拉电流源关闭,控制所述可调下拉电流源输出最小档位电流,获得所述比较器的第二结果;根据所述第一结果和所述第二结果判断检测状态,所述检测状态包括io口为浮空、接入上拉电阻和接入下拉电阻三种。

10、优选的,在所述检测状态为接入下拉电阻时,所述逻辑控制单元还用于控制所述可调上拉电流源从最小档位开始逐级增大输出电流至所述外部下拉电阻,直至所述比较器的输出发生翻转,并在翻转后计算所述外部下拉电阻的阻值并保存。

11、优选的,所述可调上拉电流源相邻较大档位的电流值是较小档位的电流值的10或以上的倍数。

12、优选的,在所述检测状态为接入上拉电阻时,所述逻辑控制单元还用于控制所述可调下拉电流源从最小档位开始逐级增大输出电流至所述外部上拉电阻,直至所述比较器的输出发生翻转,并在翻转后计算所述外部上拉电阻的阻值并保存。

13、优选的,所述可调下拉电流源相邻较大档位的电流值是较小档位的电流值的10或以上的倍数。

14、第二方面,本发明实施例提供一种芯片的输入输出多态检测方法,所述输入输出多态检测方法基于上述的芯片,所述输入输出多态检测方法包括以下步骤:

15、s11、在芯片的逻辑控制单元控制可调下拉电流源关闭,控制可调上拉电流源输出最小档位电流,读取比较器的第一结果;

16、s12、所述逻辑控制单元控制所述可调上拉电流源关闭,控制所述可调下拉电流源输出最小档位电流,读取所述比较器的第二结果;

17、s13、根据所述第一结果和所述第二结果判断检测状态;

18、若所述检测状态为浮空,则直接结束;

19、若所述检测状态为接入外部下拉电阻,所述逻辑控制单元关闭所述可调下拉电流源,打开所述可调上拉电流源,并将所述可调上拉电流源的档位电流调到最小,所述比较器输出所述第一结果为0;所述逻辑控制单元逐步调大所述可调上拉电流源的档位电流,观测所述比较器输出结果,当所述比较器输出的所述第一结果由0变为1时,所述逻辑控制单元根据所述可调上拉电流源的档位电流判定所述外部下拉电阻的阻值;

20、若所述检测状态为接入外部上拉电阻,所述逻辑控制单元关闭所述可调上拉电流源,打开所述可调下拉电流源,并将所述可调下拉电流源的档位电流调到最小,所述比较器输出的所述第二结果为1;所述逻辑控制单元逐步调大所述可调下拉电流源的档位电流,观测所述比较器输出结果,当所述比较器输出的所述第二结果由1变为0时,所述逻辑控制单元根据所述可调下拉电流源的档位电流判定所述外部上拉电阻的阻值;其中,1和0表示判定真值;

21、s14、完成全部检测,关闭所述可调上拉电流源和所述可调下拉电流源,并将检测结果进行保存。

22、优选的,所述s14中,将所述检测结果保存于寄存器。

23、第三方面,本发明实施例提供一种计算机设备,包括:存储器、处理器及存储在所述存储器上并可在所述处理器上运行的芯片的输入输出多态检测程序,所述处理器执行所述芯片的输入输出多态检测程序时实现上述的芯片的输入输出多态检测方法中的步骤。

24、第四方面,本发明实施例提供一种计算机可读存储介质,所述计算机可读存储介质上存储有芯片的输入输出多态检测程序,所述芯片的输入输出多态检测程序被处理器执行时实现如上述的芯片的输入输出多态检测方法中的步骤。

25、本发明所达到的有益效果,在于提出了一种芯片、芯片的多态检测方法、计算机设备及计算机可读存储介质,芯片包括用于连接外部电源的电源端及用于接地的接地端,通过将可调上拉电流源、可调下拉电流源、比较器、逻辑控制单元以及io口连接;逻辑控制单元用于分别控制可调上拉电流源和可调下拉电流源的开与关以及输出的电流大小,并结合电压比较结果,判断外部电阻是上拉状态还是下拉状态,以及上拉状态或下接状态时的电阻阻值;使得外部可以挂多种阻值的上拉或下拉电阻,内部自动检测外部挂的是上拉还是下拉以及外挂电阻的阻值,从而实现一个io口有多种输入状态;对于芯片的多态检测方法状态识别数量多、节约资源及检测精度高。

技术特征:

1.一种芯片,所述芯片包括用于连接外部电源的电源端及用于接地的接地端,其特征在于,所述芯片还包括可调上拉电流源、可调下拉电流源、比较器、逻辑控制单元以及io口;

2.如权利要求1所述的芯片,其特征在于,所述逻辑控制单元还用于控制所述可调下拉电流源关闭,控制所述可调上拉电流源输出最小档位电流,获得所述比较器的第一结果;

3.如权利要求2所述的芯片,其特征在于,在所述检测状态为接入下拉电阻时,所述逻辑控制单元还用于控制所述可调上拉电流源从最小档位开始逐级增大输出电流至所述外部下拉电阻,直至所述比较器的输出发生翻转,并在翻转后计算所述外部下拉电阻的阻值并保存。

4.如权利要求3所述的芯片,其特征在于,所述可调上拉电流源相邻较大档位的电流值是较小档位的电流值的10或以上的倍数。

5.如权利要求2所述的芯片,其特征在于,在所述检测状态为接入上拉电阻时,所述逻辑控制单元还用于控制所述可调下拉电流源从最小档位开始逐级增大输出电流至所述外部上拉电阻,直至所述比较器的输出发生翻转,并在翻转后计算所述外部上拉电阻的阻值并保存。

6.如权利要求5所述的芯片,其特征在于,所述可调下拉电流源相邻较大档位的电流值是较小档位的电流值的10或以上的倍数。

7.一种芯片的输入输出多态检测方法,其特征在于,所述输入输出多态检测方法基于权利要求1-6任一项所述的芯片,所述输入输出多态检测方法包括以下步骤:

8.如权利要求7所述的输入输出多态检测方法,其特征在于,所述s14中,将所述检测结果保存于寄存器。

9.一种计算机设备,其特征在于,包括:存储器、处理器及存储在所述存储器上并可在所述处理器上运行的芯片的输入输出多态检测程序,所述处理器执行所述芯片的输入输出多态检测程序时实现如权利要求7-8任一项所述的芯片的输入输出多态检测方法中的步骤。

10.一种计算机可读存储介质,其特征在于,所述计算机可读存储介质上存储有芯片的输入输出多态检测程序,所述芯片的输入输出多态检测程序被处理器执行时实现如权利要求7-8任一项所述的芯片的输入输出多态检测方法中的步骤。

技术总结

本发明适用于芯片多态检测技术领域,尤其涉及一种芯片、芯片的输入输出多态检测方法及相关设备;芯片包括电源端、接地端、可调上拉电流源、可调下拉电流源、比较器、逻辑控制单元以及IO口;IO口连接一个电阻节点,电阻节点为按顺序串接在外部电源与地之间的外部上拉电阻及外部下拉电阻的连接点;可调上拉电流源用于使不同电流值的电流流过外部下拉电阻,以在IO口得到对应的第一电压;可调下拉电流源用于使不同电流值的电流流过外部上拉电阻,以在IO口得到对应的第二电压;比较器用于将第一电压和第二电压分别与预设阈值电压进行比较;逻辑控制单元用于结合电压比较结果。本发明的芯片检测状态识别数量多,节约资源,检测精度高。

技术研发人员:文浩飞

受保护的技术使用者:深圳市思远半导体有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!