用于进行芯片测试的系统及方法、装置、设备、存储介质与流程

本申请涉及集成芯片测试,例如涉及一种用于进行芯片测试的系统及方法、装置、设备、存储介质。

背景技术:

1、集成电路芯片在生产、出厂或使用前需要进行芯片测试,即对芯片的各个功能进行测试。随着集成电路芯片的功能复杂程度的提高和规模的日益增大,板级测试如何实现芯片复杂功能的测试已经成为迫切需要解决的问题。特别是进入深亚微米以及高级成度的发展阶段以来,通过集成各种ip(intellectualproperty,知识财产)核,多cpu(centralprocessing unit,中央处理器)核系统级芯片mcu(microcontroller unit,微控制器单元)的功能更加强大。

2、在实现本公开实施例的过程中,发现相关技术中至少存在如下问题:

3、相关技术中在进行芯片测试时,通常是针对芯片的不同功能逐个进行测试。而在芯片的功能较多的情况下进行芯片测试时容易导致测试时间较长。从而使得芯片的测试效率较差。

4、需要说明的是,在上述背景技术部分公开的信息仅用于加强对本申请的背景的理解,因此可以包括不构成对本领域普通技术人员已知的现有技术的信息。

技术实现思路

1、为了对披露的实施例的一些方面有基本的理解,下面给出了简单的概括。所述概括不是泛泛评述,也不是要确定关键/重要组成元素或描绘这些实施例的保护范围,而是作为后面的详细说明的序言。

2、本公开实施例提供了一种用于进行芯片测试的系统及方法、装置、设备、存储介质,以能够提高芯片的测试效率。

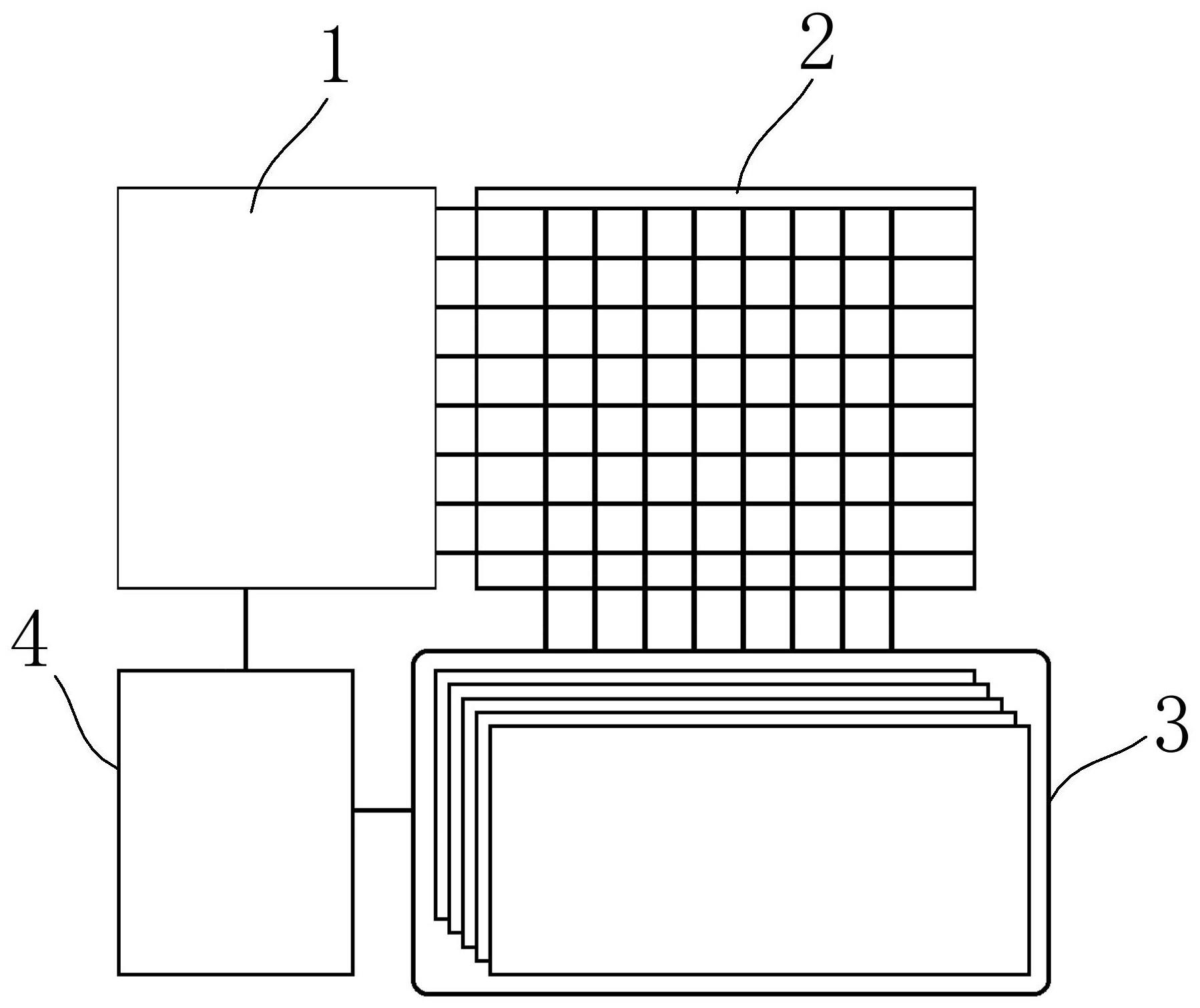

3、在一些实施例中,用于进行芯片测试的系统,包括:待测主板,所述待测主板上设置有待测芯片,待测主板与接口板连接。接口板,一端与待测主板连接,另一端与功能板模块连接。功能板模块,包括多个功能板;单个功能板对应待测芯片的一种功能;各功能板对应待测芯片的不同功能;各功能板用于接收预设的测试指令,并根据预设的测试指令对与待测芯片的多个功能同时进行测试。设备,分别与待测主板和功能板模块连接;所述设备被配置为发送预设的测试指令给各功能板,触发各功能板对待测芯片的多个功能同时进行测试。

4、在一些实施例中,所述接口板,包括:接口板总线接口,与通讯总线连接,以实现各功能板与设备之间的信息交互。接口板电源接口,与电源系统连接,以提供工作所需的电压给接口板。功能测试单元,包括多个io接口,所述功能测试单元与待测主板连接,所述功能测试单元被配置为受控通过各io接口与各功能板连接。

5、在一些实施例中,所述功能板,包括:功能测试电路,用于受控对待测主板中待测芯片的一种功能进行测试。fpga(field programmable gate array,现场可编程逻辑门阵列),被配置为受控将接口板与功能测试电路进行连通,以构建待测主板与功能板之间的测试通道。

6、在一些实施例中,所述用于进行芯片测试的方法,包括:确定待测主板中待测芯片的多个待测功能。确定各待测功能分别对应的功能板。发送预设的测试指令给各功能板,触发各功能板根据预设的测试指令对各待测功能同时进行测试。

7、在一些实施例中,发送预设的测试指令给各功能板,触发各功能板根据预设的测试指令对各待测功能同时进行测试,包括:分别构建待测主板与各功能板之间的测试通道。发送预设的测试指令给各功能板,触发各功能板通过各测试通道对各待测功能同时进行测试。

8、在一些实施例中,构建待测主板与功能板之间的测试通道,包括:确定功能板对应的目标输出io和目标输入io。将目标输出io与目标输入io连通,以构建功能板与待测主板之间的测试通道。

9、在一些实施例中,确定功能板对应的目标输出io,包括:从预设的数据库中匹配出与待测功能对应的第一备选输出io。预设的数据库中存储有待测功能与第一备选输出io之间的对应关系。将第一备选输出io确定为功能板对应的目标输出io。

10、在一些实施例中,确定功能板对应的目标输入io,包括:根据待测功能确定待测主板的选通io,并将选通io与功能板进行连接。根据目标输出io从选通io中确定出功能板对应的目标输入io。

11、在一些实施例中,根据目标输出io从选通io中确定出功能板对应的目标输入io,包括:从预设的数据库中匹配出与目标输出io对应的第二备选输入io。预设的数据库中存储有目标输出io与第二备选输入io之间的对应关系。第二备选输入io为功能测试单元中的io接口。将与第二备选输入io相同的选通io确定为功能板对应的目标输入io。

12、在一些实施例中,所述用于进行芯片测试的装置,包括处理器和存储有程序指令的存储器,所述处理器被配置为在运行所述程序指令时,执行上述的用于进行芯片测试的方法。

13、在一些实施例中,所述设备包括设备本体;如上述的用于进行芯片测试的装置,被安装于所述设备本体。

14、在一些实施例中,所述存储介质存储有程序指令,所述程序指令在运行时,执行上述的用于进行芯片测试的方法。

15、本公开实施例提供的用于进行芯片测试的系统及方法、装置、设备、存储介质,可以实现以下技术效果:用于进行芯片测试的系统包括待测主板、接口板、功能板模块和设备。待测主板上设置有待测芯片,待测主板与接口板连接。接口板一端与待测主板连接,另一端与功能板模块连接。由于功能板模块包括多个功能板,单个功能板对应待测芯片的一种功能,各功能板对应待测芯片的不同功能。通过设备发送预设的测试指令给各功能板,这样能够通过各功能板同时对待测芯片的不同功能进行测试,从而能够提高芯片的测试效率。

16、以上的总体描述和下文中的描述仅是示例性和解释性的,不用于限制本申请。

技术特征:

1.一种用于进行芯片测试的系统,其特征在于,包括:

2.根据权利要求1所述的系统,其特征在于,所述接口板,包括:

3.根据权利要求1所述的系统,其特征在于,所述功能板,包括:

4.一种基于权利要求1至3任一项所述的系统的用于进行芯片测试的方法,其特征在于,包括:

5.根据权利要求4所述的方法,其特征在于,发送预设的测试指令给各功能板,触发各功能板根据预设的测试指令对各待测功能同时进行测试,包括:

6.根据权利要求5所述的方法,其特征在于,构建待测主板与功能板之间的测试通道,包括:

7.根据权利要求6所述的方法,其特征在于,确定功能板对应的目标输出io,包括:

8.根据权利要求6所述的方法,其特征在于,确定功能板对应的目标输入io,包括:

9.根据权利要求8所述的方法,其特征在于,根据目标输出io从选通io中确定出功能板对应的目标输入io,包括:

10.一种用于进行芯片测试的装置,包括处理器和存储有程序指令的存储器,其特征在于,所述处理器被配置为在运行所述程序指令时,执行如权利要求4至9任一项所述的用于进行芯片测试的方法。

11.一种设备,其特征在于,包括:

12.一种存储介质,存储有程序指令,其特征在于,所述程序指令在运行时,执行如权利要求4至9任一项所述的用于进行芯片测试的方法。

技术总结

本申请涉及集成芯片测试技术领域,公开一种用于进行芯片测试的系统,包括:待测主板,待测主板上设置有待测芯片,待测主板与接口板连接。接口板,一端与待测主板连接,另一端与功能板模块连接。功能板模块,包括多个功能板。单个功能板对应待测芯片的一种功能;各功能板对应待测芯片的不同功能;各功能板用于接收预设的测试指令,并根据预设的测试指令对待测芯片的多个功能同时进行测试。设备,分别与待测主板和功能板模块连接。设备被配置为发送预设的测试指令给各功能板,触发各功能板根据预设的测试指令对待测芯片的多个功能同时进行测试。这样能够提高芯片的测试效率。本申请还公开一种用于进行芯片测试的方法及装置、设备、存储介质。

技术研发人员:刘新华,罗伟,段冬辉,黄钧

受保护的技术使用者:北京紫光芯能科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!