一种芯片电性失效分析的方法与流程

本发明涉及半导体制造,具体为一种芯片电性失效分析的方法。

背景技术:

1、在对单颗芯片进行电性失效分析(electrical failure analysis,efa)的测试过程中,通过先在球面扎针或者打线(wire bonding),再进行efa测试。而在球面扎针测试中,扎针的数量有限,但对于球面样品容易造成滑针,且受震动时会导致脱针等,从而导致接触不良或短路(short),影响测试结果,且扎针过程中会损伤样品,导致测试结果不准确。在球栅阵列(ball grid array,bga)封装结构中,打线时,需在锡球面结构上打线,同时又是在锡材料上焊接金线,而锡容易被氧化,则会发生打线困难、导线脱落和导线断裂等情况,导致efa测试无法顺利进行。

技术实现思路

1、本发明提出了一种芯片电性失效分析的方法,能有效提高打线的效率和质量,降低打线困难、导线脱落和断裂等情况的发生,从而提高芯片封装测试的效率及准确性。

2、为解决上述技术问题,本发明是通过如下的技术方案实现的:

3、本发明提出一种芯片电性失效分析的方法,至少包括以下步骤:

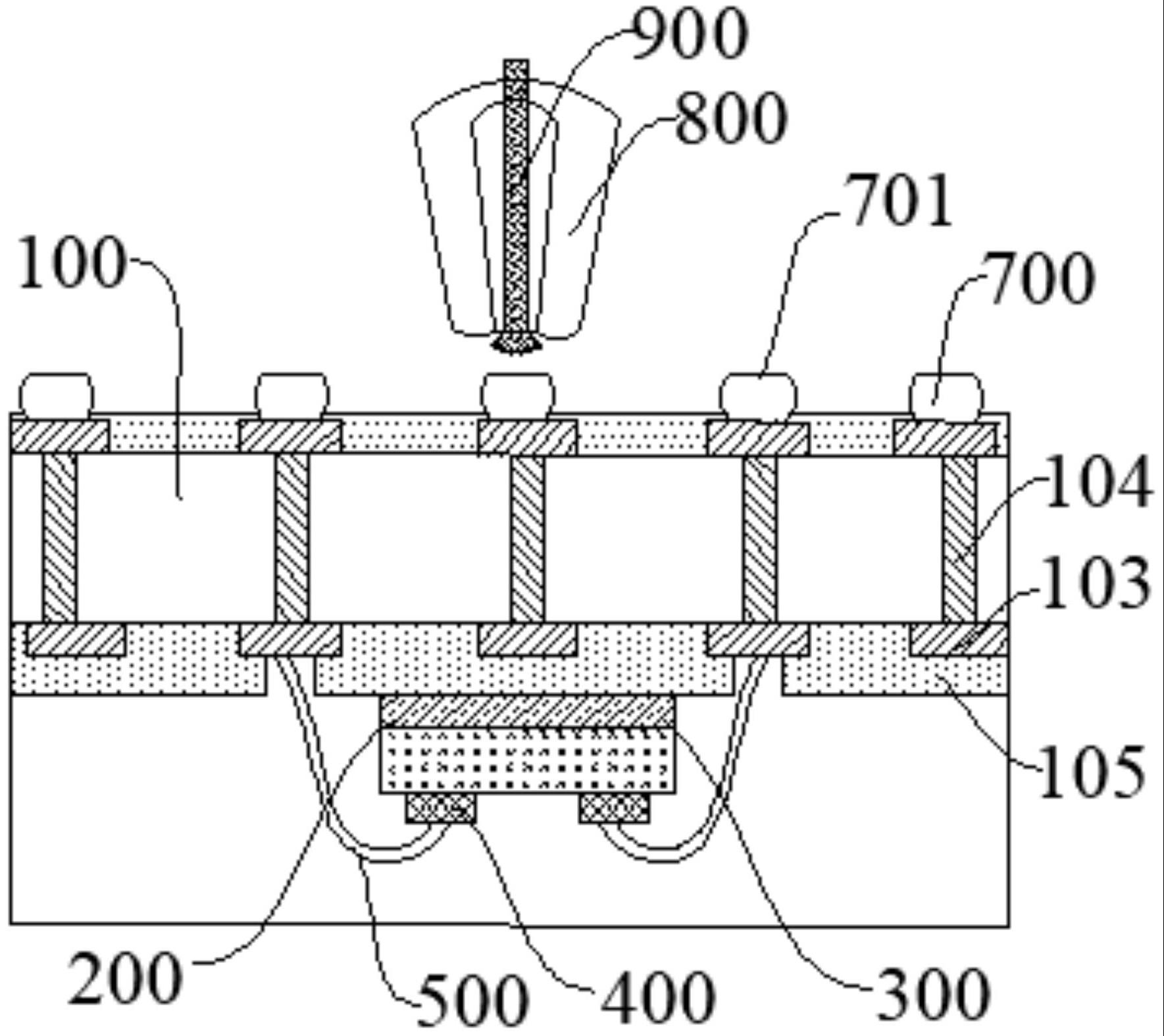

4、提供一基板,所述基板包括相对设置的第一表面和第二表面;

5、在所述第一表面和所述第二表面设置导电线路;

6、在所述导电线路上形成保护层,所述保护层暴露所述第一表面上的部分所述导电线路;

7、将晶粒粘接在所述第一表面上,且所述晶粒与暴露的所述导电线路电性连接;

8、在所述第一表面上形成密封膜,所述密封膜覆盖所述晶粒;

9、在所述第二表面上植入多个焊球;

10、将多个所述焊球表面进行摩擦,形成平面,所述平面位于远离所述基板的一侧;以及

11、将金属导线焊接在所述焊球表面的平面上,进行电性失效分析。

12、在本发明一实施例中,形成所述平面的步骤包括:将劈刀靠近所述焊球,以去除所述焊球表面的氧化层。

13、在本发明一实施例中,在形成所述平面的步骤之前,所述方法包括将植入所述焊球的所述基板进行回流焊处理,且回流焊处理的温度为215℃-245℃。

14、在本发明一实施例中,所述平面的直径为所述焊球直径的1/10-1/5。

15、在本发明一实施例中,所述焊球上的所述平面与所述第二表面平行。

16、在本发明一实施例中,所述焊球与所述基板的接触界面至所述焊球球心的距离为所述焊球半径的1/2-9/10。

17、在本发明一实施例中,所述晶粒粘接在所述第一表面上的步骤之前,所述方法包括在所述保护层上设置粘着剂层。

18、在本发明一实施例中,所述粘着剂层的宽度与所述晶粒的宽度相等。

19、在本发明一实施例中,在形成所述密封膜的步骤之前,所述方法包括在所述晶粒上设置多个接合垫。

20、在本发明一实施例中,在形成所述密封膜的步骤之前,所述方法还包括,在多个所述接合垫上进行打线,形成接合线,所述晶粒通过所述接合线与暴露的所述导电线路电性连接。

21、本发明提出了一种芯片电性失效分析的方法,在焊球表面上形成平面,本申请意想不到的效果是能有效提高在球栅阵列封装结构上打线的效率和质量,降低打线困难、导线脱落和断裂等情况的发生。能够提高芯片电性失效分析测试的效率及准确性,从而能及时发现问题并及时调整芯片生产及芯片封装工艺,从而提高芯片的良品率。

22、当然,实施本发明的任一产品并不一定需要同时达到以上所述的所有优点。

技术特征:

1.一种芯片电性失效分析的方法,其特征在于,至少包括以下步骤:

2.根据权利要求1所述的一种芯片电性失效分析的方法,其特征在于,形成所述平面的步骤包括:将劈刀靠近所述焊球,以去除所述焊球表面的氧化层。

3.根据权利要求1所述的一种芯片电性失效分析的方法,其特征在于,在形成所述平面的步骤之前,所述方法包括:将植入所述焊球的所述基板进行回流焊处理,且回流焊处理的温度为215℃-245℃。

4.根据权利要求1所述的一种芯片电性失效分析的方法,其特征在于,所述平面的直径为所述焊球直径的1/10-1/5。

5.根据权利要求1所述的一种芯片电性失效分析的方法,其特征在于,所述焊球上的所述平面与所述第二表面平行。

6.根据权利要求1所述的一种芯片电性失效分析的方法,其特征在于,所述焊球与所述基板的接触界面至所述焊球球心的距离为所述焊球半径的1/2-9/10。

7.根据权利要求1所述的一种芯片电性失效分析的方法,其特征在于,在所述晶粒粘接在所述第一表面上的步骤之前,所述方法包括在所述保护层上设置粘着剂层。

8.根据权利要求7所述的一种芯片电性失效分析的方法,其特征在于,所述粘着剂层的宽度与所述晶粒的宽度相等。

9.根据权利要求1所述的一种芯片电性失效分析的方法,其特征在于,在形成所述密封膜的步骤之前,所述方法包括在所述晶粒上设置多个接合垫。

10.根据权利要求9所述的一种芯片电性失效分析的方法,其特征在于,在形成所述密封膜的步骤之前,所述方法还包括,在多个所述接合垫上进行打线,形成接合线,所述晶粒通过所述接合线与暴露的所述导电线路电性连接。

技术总结

本发明提出了一种芯片电性失效分析的方法,属于半导体制造技术领域,所述方法至少包括:提供一基板,包括相对设置的第一表面和第二表面;在所述第一表面和所述第二表面设置导电线路;在所述导电线路上形成保护层,所述保护层暴露所述第一表面上的部分所述导电线路;将晶粒粘接在所述第一表面上,且所述晶粒与暴露的所述导电线路电性连接;在所述第一表面上形成密封膜,所述密封膜覆盖所述晶粒;在所述第二表面上植入多个焊球;将多个所述焊球表面进行摩擦,形成平面,所述平面位于远离所述基板的一侧;以及将金属导线焊接在所述平面上,进行电性失效分析。本发明提供的一种芯片电性失效分析的方法,能有效提高芯片失效分析测试的效率及准确性。

技术研发人员:陈红军,龚超,张琳琳,许桐

受保护的技术使用者:合肥晶合集成电路股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!