一种应用于MCU的EFT检测电路的制作方法

本技术涉及模拟集成电路领域,具体涉及一种应用于mcu的eft检测电路。

背景技术:

1、mcu是ic的一个重要组件。由于其成本低但性能强大,mcu在许多领域都有较为广泛的运用。一些研究机构的mcu市场行情分析报告指出,随着家居产品、汽车产品、工业产品的迭代更新,mcu的产量使用量逐年提高。对于含有mcu的微电子产品而言,eft(electricalfasttransient,电快速瞬变脉冲群)具有上升时间短、频率高、能量高的特点,是设计时需要考虑的一个典型的瞬态干扰。由于eft对mcu的干扰,通常导致mcu中出现信号紊乱以及瞬态闩锁效应的问题。

2、传统的eft保护方案是在pcb板上添加分立的噪声旁路元件或板级噪声滤波器,来旁路或吸收瞬态干扰产生的能量。但是,添加额外的分立元件会大大增加产品的成本以及产品的面积。为了不增加额外的成本与面积,越来越多的设计者开始考虑芯片级的eft保护方案。

技术实现思路

1、本实用新型针对现有技术中存在的技术问题,提供一种应用于mcu的eft检测电路,符合低功耗设计要求,具有易实现、灵敏度高、可调性好的特点。

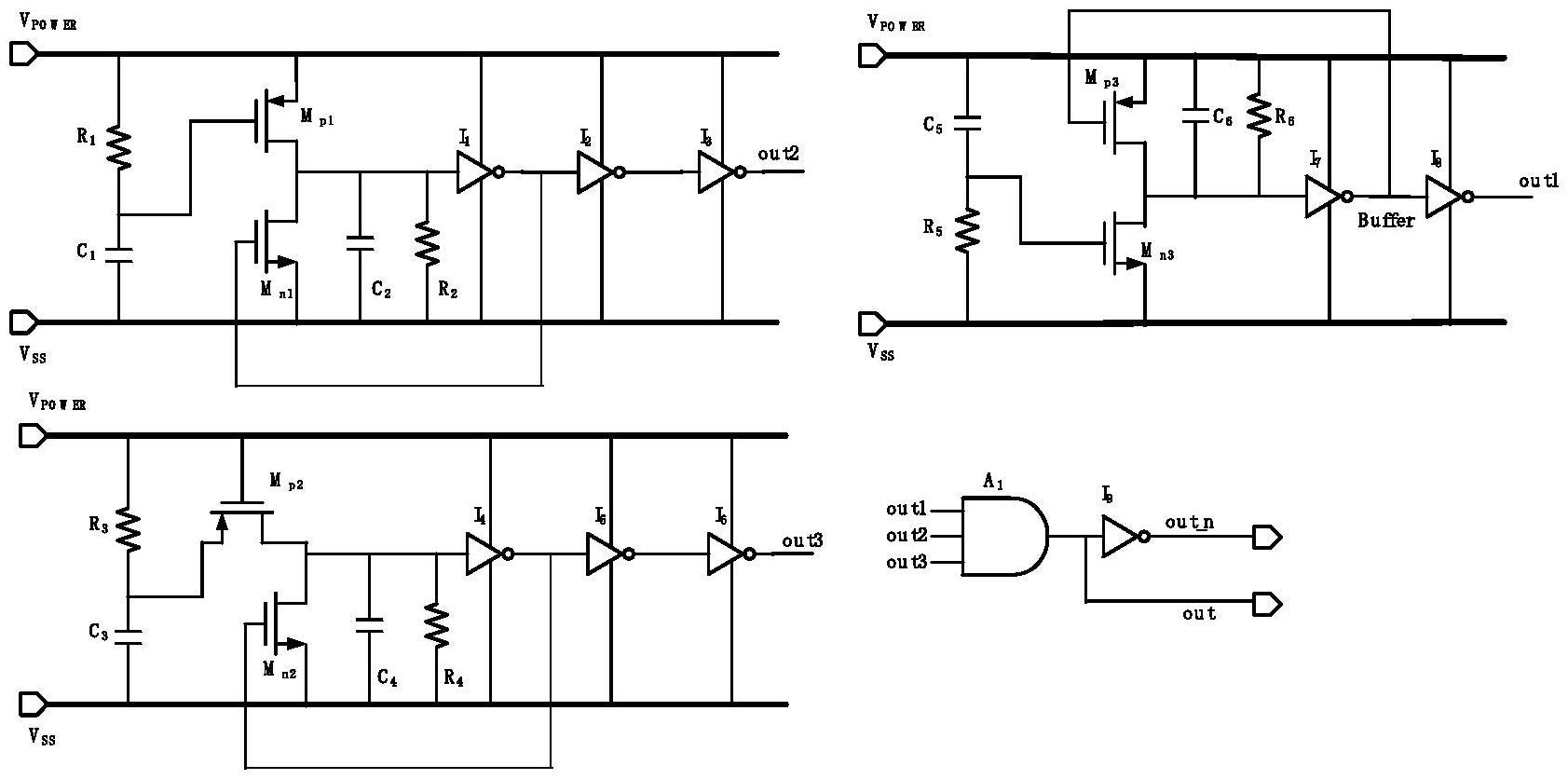

2、本实用新型解决上述技术问题的技术方案如下:一种应用于mcu的eft检测电路,包括:至少一个的检测单元;所述检测单元包括:依次连接的检测模块和延时缓冲模块;

3、所述检测模块包括:mos管、电阻和电容,mcu的电源线与所述检测模块连接,所述mcu有eft干扰时所述mos管的栅源两端产生电压差使所述mos管导通;

4、所述延时缓冲模块包括:mos管、电阻、电容和反向器,所述电容在所述eft干扰产生和结束时分别进行充电和放电。

5、在上述技术方案的基础上,本实用新型还可以做如下改进。

6、进一步,所述eft检测电路包括:至少两个的所述检测单元和逻辑单元;

7、所述逻辑单元包括:与门;

8、各个检测单元的输出与所述与门的各个输入端连接。

9、进一步,所述逻辑单元包括:反相器;

10、所述与门的输出端连接至所述反相器的输入端;

11、所述与门的输出端与所述反相器的输出端作为所述eft检测电路双路信号输出端。

12、进一步,所述检测单元包括:检测单元a;

13、所述检测单元a的检测模块包括:电阻r1、电容c1和pmos管mp1;

14、所述电阻r1的一端连接所述mcu的电源线,所述电阻r1的另一端连接至所述pmos管mp1的栅极,所述电阻r1的另一端还通过所述电容c1接地;所述pmos管mp1的源极连接所述mcu的电源线,所述pmos管mp1的漏极连接至所述延时缓冲模块。

15、进一步,所述检测单元a的延时缓冲模块包括:nmos管mn1、电阻r2、电容c2、反相器i1、反相器i2和反相器i3;

16、所述pmos管mp1的漏极与所述nmos管mn1的漏极以及所述反相器i1的输入端连接;所述pmos管mp1的漏极还通过并联的所述电阻r2和所述电容c2接地;

17、所述nmos管mn1的源极接地,nmos管mn1的栅极连接至所述反相器i1的输出端,所述nmos管mn1的栅极还连接至所述反相器i2的输入端;所述反相器i2的输出端连接到所述反相器i3的输入端,所述反相器i3的输出端为所述检测单元a的输出端。

18、进一步,所述检测单元包括:检测单元b;

19、所述检测单元b的检测模块包括:电阻r3、电容c3和pmos管mp2;

20、所述电阻r3一端连接所述mcu的电源线,所述电阻r3的另一端连接至所述pmos管mp2的源极,所述电阻r3的另一端还通过所述电容c3接地;所述pmos管mp2的栅极连接所述mcu的电源线,所述pmos管mp2漏极连接至所述延时缓冲模块。

21、进一步,所述检测单元b的延时缓冲模块包括:nmos管mn2、电阻r4、电容c4、反相器i4、反相器i5和反相器i6;

22、所述pmos管mp2的漏极连接至所述nmos管mn2的漏极和所述反相器i4的输入端;所述pmos管mp2的漏极还通过并联的所述电阻r4和所述电容c4接地;

23、所述nmos管mn2的源极接地,所述nmos管mn2的栅极连接至所述反相器i4的输出端,所述nmos管mn2的栅极还连接至所述反相器i5的输入端;所述反相器i5的输出端连接到所述反相器i6的输入端,所述反相器i6的输出端为所述检测单元b的输出端。

24、进一步,所述检测单元包括:检测单元c;

25、所述检测单元c的检测模块包括:电阻r5、电容c5和nmos管mn3;

26、所述电容c5一端连接所述mcu的电源线,所述电容c5的另一端连接至nmos管mn3的栅极,所述电容c5的另一端还通过电阻r5接地;所述nmos管mn3的源极接地,所述nmos管mn3的漏极连接至所述延时缓冲模块。

27、进一步,所述检测单元c的延时缓冲模块包括:pmos管mp3、电阻r6、电容c6、反相器i7和反相器i8;

28、所述nmos管mn3的漏极连接至所述pmos管mp3的漏极和所述反相器i7的输入端;所述nmos管mn3的漏极还通过并联的所述电阻r6和所述电容c6连接所述mcu的电源线;所述pmos管mp3的栅极连接至所述反相器i7的输出端和所述反相器i8的输入端;所述反相器i7的输出端连接到所述反相器i8的输入端,所述反相器i8的输出端为所述检测单元c的输出端。

29、采用上述进一步方案的有益效果是:

30、1、本实用新型采用三个检测电路单元输出相与的方式,提高了检测的灵敏度,能够保证检测电路对不同幅度、类型的eft干扰均具有良好的检测效果。

31、2.通过调节电阻r2、电容c2、电阻r4、电容c4、电阻r6、电容c6的器件参数值,可以实现输出脉冲宽度的动态调整,以应对不同的设计需求。

32、3.电路的整体结构较为简单,电路设计易实现,芯片级的解决方案可以大大降低面积。

技术特征:

1.一种应用于mcu的eft检测电路,其特征在于,所述eft检测电路包括:至少一个的检测单元;所述检测单元包括:依次连接的检测模块和延时缓冲模块;

2.根据权利要求1所述的eft检测电路,其特征在于,所述eft检测电路包括:至少两个的所述检测单元和逻辑单元;

3.根据权利要求2所述的eft检测电路,其特征在于,所述逻辑单元包括:反相器;

4.根据权利要求1所述的eft检测电路,其特征在于,所述检测单元包括:检测单元a;

5.根据权利要求4所述的eft检测电路,其特征在于,所述检测单元a的延时缓冲模块包括:nmos管mn1、电阻r2、电容c2、反相器i1、反相器i2和反相器i3;

6.根据权利要求1所述的eft检测电路,其特征在于,所述检测单元包括:检测单元b;

7.根据权利要求6所述的eft检测电路,其特征在于,所述检测单元b的延时缓冲模块包括:nmos管mn2、电阻r4、电容c4、反相器i4、反相器i5和反相器i6;

8.根据权利要求1所述的eft检测电路,其特征在于,所述检测单元包括:检测单元c;

9.根据权利要求8所述的eft检测电路,其特征在于,所述检测单元c的延时缓冲模块包括:pmos管mp3、电阻r6、电容c6、反相器i7和反相器i8;

技术总结

本技术涉及一种应用于MCU的EFT检测电路,包括:至少一个的检测单元;检测单元包括:依次连接的检测模块和延时缓冲模块;检测模块包括:MOS管、电阻和电容,MCU的电源线与检测模块连接,MCU有EFT干扰时MOS管的栅源两端产生电压差使MOS管导通;延时缓冲模块包括:MOS管、电阻、电容和反向器,电容在EFT干扰产生和结束时分别进行充电和放电;采用多个检测电路单元输出相与的方式,提高了检测的灵敏度,能够保证检测电路对不同幅度、类型的EFT干扰均具有良好的检测效果;通过调节电路的器件参数值,可以实现输出脉冲宽度的动态调整,以应对不同的设计需求;电路的整体结构较为简单,电路设计易实现,芯片级的解决方案可以大大降低面积。

技术研发人员:龚明杨,刘徐港,孙缵,徐芳

受保护的技术使用者:武汉瑞纳捷半导体有限公司

技术研发日:20230316

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!