芯片测试电路及测试设备的制作方法

本技术涉及芯片测试,具体涉及一种芯片测试电路及测试设备。

背景技术:

1、对芯片进行测试时,例如,芯片可以指dut(待测器件或待测单元),往往存在部分待测单元所需要的供电电压较高,如5~8v,而部分待测单元所需要的供电电压较低,如5v以下。为了对待测单元实现宽电压范围供电,目前,要么使用dc-dc电源进行宽电压范围供电,要么使用ldo电源进行宽电压范围供电。

2、然而,上述宽电压范围供电方案仍存在以下缺陷:使用dc-dc电源进行宽电压范围供电会形成较大纹波,从而影响待测单元的测试精度;而使用ldo电源进行宽电压范围供电又会导致为待测单元提供较低电压时,整个电路压差大,导致发热过高功耗大,也难以提升待测单元的测试精度。

3、由上可知,如何在宽电压范围供电的前提下,减小压差、降低功耗、减小纹波,从而提高待测单元的测试精度的问题仍有待解决。

技术实现思路

1、本实用新型各实施例提供了一种芯片测试电路及测试设备,可以解决相关技术中存在的测试精度不高的问题。所述技术方案如下:

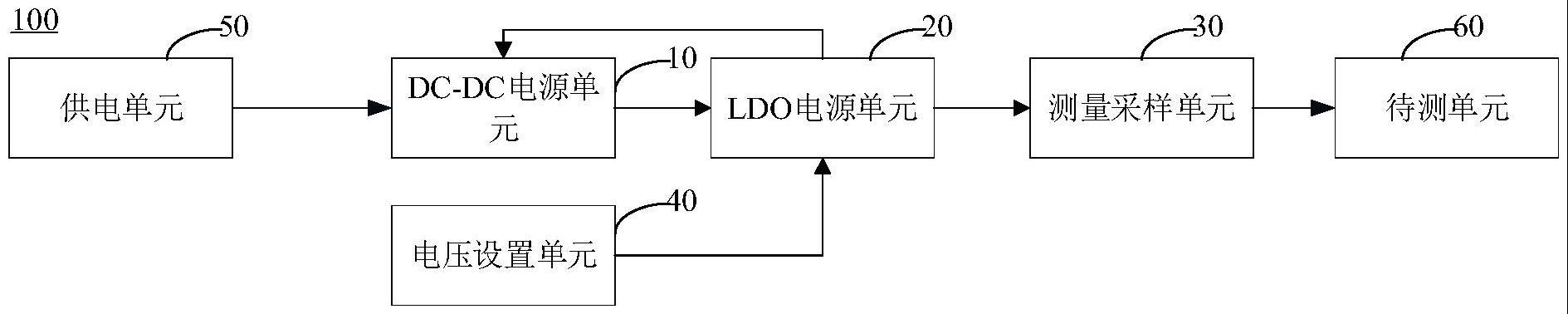

2、根据本实用新型实施例的一个方面,一种芯片测试电路,所述芯片测试电路连接在供电单元与待测单元之间,包括:dc-dc电源单元,与所述供电单元连接,对所述供电单元输出的电压进行稳压;ldo电源单元,与所述dc-dc电源单元连接,将所述dc-dc电源单元稳压输出的电压作为输入电压,并对所述输入电压进行稳压,得到输出电压;测量采样单元,与所述ldo电源单元连接,将所述ldo电源单元输出的输出电压作为供电电压,对所述待测单元进行宽电压范围供电,使得所述测量采样单元基于所述供电电压对所述待测单元进行芯片测试;其中,所述ldo电源单元的反馈端与所述dc-dc电源单元相连,以对所述dc-dc电源单元稳压输出的电压进行调节,使得所述输入电压与所述输出电压之间的压差在设定范围内。

3、可选地,所述ldo电源单元的输入电压与输出电压之间压差的设定范围为0~1v。

4、可选地,所述测量采样单元包括连接在所述ldo电源单元与所述待测单元之间的提供不同测试档位的多个采样模块、以及分别与多个采样模块连接的第一测量模块和第二测量模块;

5、通过所述第一测量模块或所述第二测量模块对不同采样模块进行采样,测试所述待测单元在不同测试档位下的测试数据。

6、可选地,所述采样模块包括连接在所述ldo电源单元与所述待测单元之间的采样限流元件和/或与所述采样限流元件连接的开关管元件;

7、通过导通所述开关管元件,导通所述ldo电源单元与所述待测单元之间的路径,以通过所述第一测量模块或所述第二测量模块对与所述开关管元件连接的采样限流元件进行采样,测试所述待测单元在所述采样限流元件对应的测试档位下的测试数据。

8、可选地,所述开关管元件包括mos管。

9、可选地,所述采样限流元件包括采样电阻。

10、可选地,所述采样模块的数量为三个;第一个采样模块包括第一采样电阻和第一mos管,第二个采样模块包括第二采样电阻和第二mos管,第三个采样模块包括第三采样电阻;

11、第一采样电阻的输出端分别与第一mos管、第二采样电阻、第三采样电阻的输入端连接;第二采样电阻的输出端与第二mos管的输入端连接;第一mos管、第二mos管、第三采样电阻的输出端与所述待测单元的输入端连接;

12、所述第一测量单元与第一采样电阻并联;所述第二测量单元与第三采样电阻并联。

13、可选地,所述电路还包括与所述ldo电源单元连接的电压设置单元,所述电压设置单元根据所述待测单元所需要的供电电压设置所述ldo电源单元的输出电压。

14、可选地,所述供电单元输出的电压的范围为0.6~10v。

15、根据本实用新型实施例的一个方面,一种测试设备,所述测试设备包括如前所述的芯片测试电路。

16、可选地,所述测试设备包括ate设备。

17、本实用新型提供的技术方案带来的有益效果是:

18、在上述技术方案中,本实用新型提供了一种芯片测试电路,通过与供电单元连接的dc-dc电源单元将供电单元输出的电压进行一次稳压后,并作为输入电压输入至与dc-dc电源单元连接的ldo电源单元,通过该ldo电源单元对输入电压进行二次稳压后得到输出电压,并作为供电电压经测量采样单元对待测单元进行宽电压范围供电,使得测量采样单元基于供电电压对待测单元进行芯片测试,其中,通过ldo电源单元的反馈端与dc-dc电源单元的反馈相连,以对dc-dc电源单元稳压输出的电压进行调节,使得输入ldo电源单元的输入电压与输出电压之间的压差在设定范围内,从而有利于降低输入电压与输出电压之间的压差,使该压差的设定范围可以控制在0~1v,此外,通过测量采样单元中开关管元件的导通与关断,使得测量采样单元中的采样限流元件提供不同测试档位,以实现对待测单元进行不同测试档位的测量,能够有效地解决相关技术中存在的测试精度不高的问题。

技术特征:

1.一种芯片测试电路,所述芯片测试电路连接在供电单元与待测单元之间,其特征在于,所述电路包括:

2.如权利要求1所述的电路,其特征在于,所述ldo电源单元的输入电压与输出电压之间压差的设定范围为0~1v。

3.如权利要求1所述的电路,其特征在于,所述测量采样单元包括连接在所述ldo电源单元与所述待测单元之间的提供不同测试档位的多个采样模块、以及分别与多个采样模块连接的第一测量模块和第二测量模块;

4.如权利要求3所述的电路,其特征在于,所述采样模块包括连接在所述ldo电源单元与所述待测单元之间的采样限流元件和/或与所述采样限流元件连接的开关管元件;

5.如权利要求4所述的电路,其特征在于,所述开关管元件包括mos管。

6.如权利要求4所述的电路,其特征在于,所述采样限流元件包括采样电阻。

7.如权利要求4所述的电路,其特征在于,所述采样模块的数量为三个;第一个采样模块包括第一采样电阻和第一mos管,第二个采样模块包括第二采样电阻和第二mos管,第三个采样模块包括第三采样电阻;

8.如权利要求1至7任一项所述的电路,其特征在于,所述电路还包括与所述ldo电源单元连接的电压设置单元,所述电压设置单元根据所述待测单元所需要的供电电压设置所述ldo电源单元的输出电压。

9.如权利要求1至7任一项所述的电路,其特征在于,所述供电单元输出的电压的范围为0.6~10v。

10.一种测试设备,其特征在于,所述测试设备包括如权利要求1至9任一项所述的芯片测试电路。

技术总结

本技术实施例提供了一种芯片测试电路及测试设备,涉及芯片测试技术领域。其中,该芯片测试电路连接在供电单元与待测单元之间,包括:与所述供电单元连接的DC‑DC电源单元、与所述DC‑DC电源单元连接的LDO电源单元、与所述LDO电源单元连接的测量采样单元;其中,所述LDO电源单元的反馈端与所述DC‑DC电源单元相连,以对所述DC‑DC电源单元稳压输出的电压进行调节,使得所述输入电压与所述输出电压之间的压差在设定范围内。本技术所述的一种芯片测试电路,输入电压范围大,输入电压与输出电压之间的压差小,纹波低,功耗低,测试精度高,大大提高了适用性。

技术研发人员:吴海涛,吴志盛

受保护的技术使用者:深圳市辰卓科技有限公司

技术研发日:20230331

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!