一种USB3.0PHY芯片验证测试板的制作方法

本技术涉及usb3.0测试,具体涉及一种usb3.0 phy芯片验证测试板。

背景技术:

1、usb是为大众所熟知的一种通用接口,其先后经历了usb1.0 low speed(1.5mbps)、全速usb1.1 full speed(12mbps)、高速usb2.0 high speed(480mbps)和超高速usb3.0(5gbps)等阶段。

2、usb3.0接口主要应用在电脑、摄像机、打印机、移动硬盘、手机、汽车等,用一根usb3.0线就可以将两台主从设备连接起来,实现数据互通。随着usb的不断发展,新开发的usb协议往往向下兼容,使用人员无需考虑兼容性问题。

3、usb3.0采用一种新的物理层,通过两个信道将数据的传输、确认过程分离,同时采用了一种封包路由(packet-routing)技术,并且仅允许终端设备有数据要发送时才进行传输,因此达到了5gbps的数据传输速率。

4、为了满足用户验证测试usb3.0 phy芯片功能的需求,需要设计一种usb3.0 phy芯片验证测试板,这块测试板需要满足用户对usb3.0系列兼容测试cts(compatibility testsuite)的要求,预留芯片debug pin和连接fpga的fmc(fpga mezzanine card)接口,还需要满足对esd(electro-static discharge)的设计要求等。

5、对于市场上现有的usb3.0phy芯片验证测试板,能够与其适配的fpga很少,即使有也都是基于高端fpga实现的,导致验证测试成本较高,并且现有的usb3.0 phy芯片验证测试板难以充分满足用户的验证测试要求。

技术实现思路

1、(一)解决的技术问题

2、针对现有技术所存在的上述缺点,本实用新型提供了一种usb3.0phy芯片验证测试板,能够有效克服现有技术所存在的验证测试成本较高,以及难以充分满足用户验证测试要求的缺陷。

3、(二)技术方案

4、为实现以上目的,本实用新型通过以下技术方案予以实现:

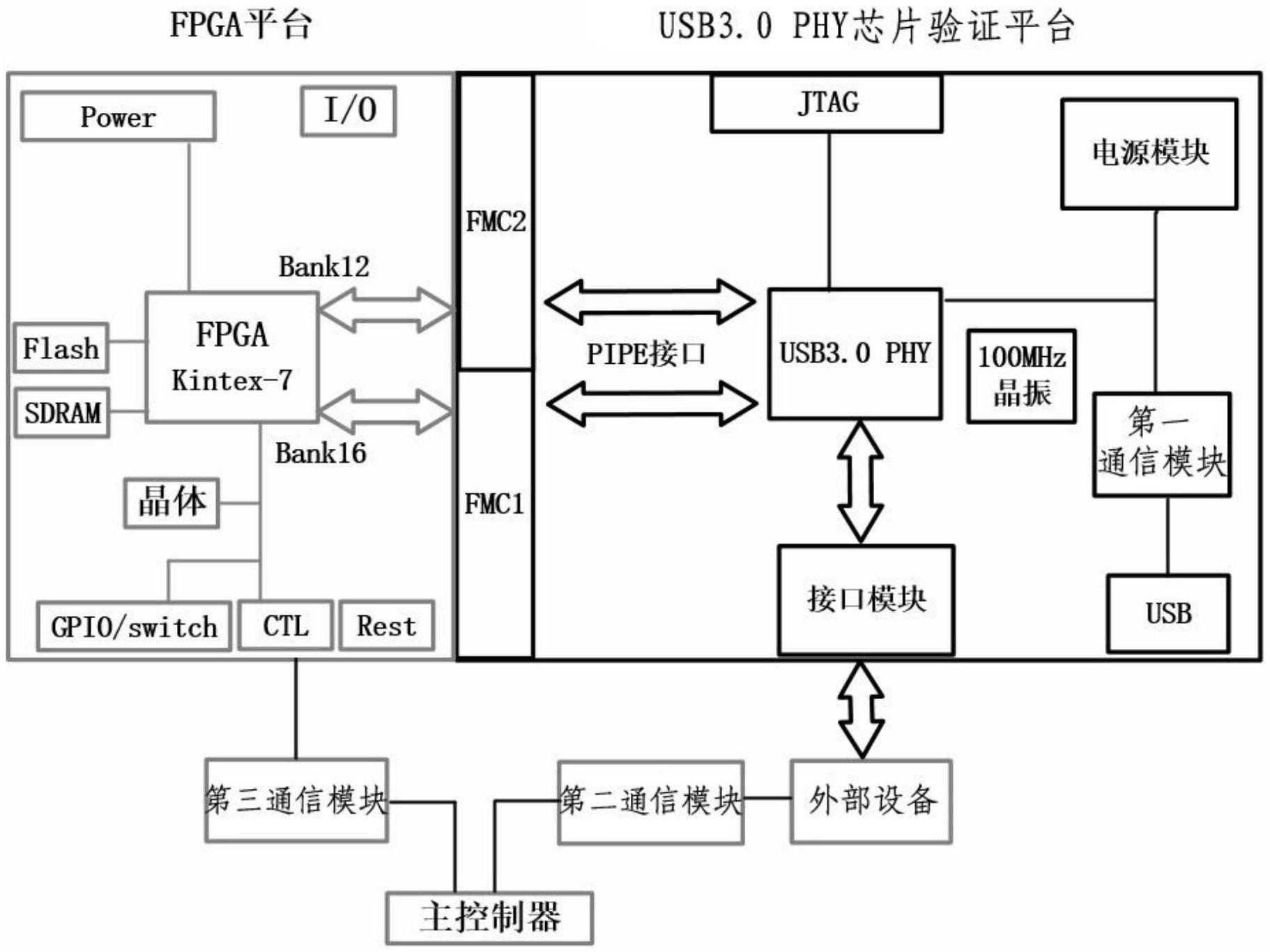

5、一种usb3.0phy芯片验证测试板,包括主控制器、fpga芯片和usb3.0phy芯片验证平台;

6、主控制器,对fpga芯片和usb3.0phy芯片验证平台进行控制,并接收usb3.0phy芯片验证平台反馈的测试数据;

7、fpga芯片,用于对usb3.0phy芯片验证平台的功能进行验证测试;

8、usb3.0phy芯片验证平台,搭载usb3.0phy芯片,与fpga芯片进行交互通信,对usb3.0phy芯片进行配置,同时对usb3.0phy芯片进行debug调试,并向主控制器发送测试数据。

9、优选地,所述主控制器通过第三通信模块对fpga芯片和usb3.0phy芯片验证平台进行控制,所述第三通信模块具有jtag接口。

10、优选地,所述主控制器通过第二通信模块连接用于接收usb3.0phy芯片验证平台反馈测试数据的外部设备;

11、其中,外部设备包括示波器和/或误码仪。

12、优选地,所述usb3.0phy芯片验证平台包括usb3.0phy芯片,以及与usb3.0phy芯片相连的fmc接口、第一通信模块、jtag接口和接口模块;

13、fmc接口,用于usb3.0phy芯片与fpga芯片进行交互通信;

14、第一通信模块,将usb接口的usb总线信号转换为i2c信号对usb3.0phy芯片进行配置;

15、jtag接口,用于对usb3.0phy芯片进行debug调试,并读取clk和register状态;

16、接口模块,向外部设备发送usb3.0 phy芯片的测试数据。

17、优选地,所述fpga芯片的第十二bank区域通过第二fmc接口与usb3.0 phy芯片的pipe接口中的tx_data、pclk进行信号连接;

18、所述fpga芯片的第十六bank区域通过第一fmc接口与usb3.0phy芯片的pipe接口中的rx_data、reset、powerdown进行信号连接;

19、其中,fpga芯片的第十二bank区域、第十六bank区域均包括clk、gpio信号。

20、优选地,所述fpga芯片采用xilinx kintex-7系列芯片。

21、(三)有益效果

22、与现有技术相比,本实用新型所提供的一种usb3.0 phy芯片验证测试板,能够与较低端的fpga芯片有效适配,从而能够降低usb3.0 phy芯片的验证测试成本,同时还能够充分满足用户对于usb3.0 phy芯片功能的验证测试要求。

技术特征:

1.一种usb3.0phy芯片验证测试板,其特征在于:包括主控制器、fpga芯片和usb3.0phy芯片验证平台;

2.根据权利要求1所述的usb3.0phy芯片验证测试板,其特征在于:所述主控制器通过第三通信模块对fpga芯片和usb3.0phy芯片验证平台进行控制,所述第三通信模块具有jtag接口。

3.根据权利要求2所述的usb3.0phy芯片验证测试板,其特征在于:所述主控制器通过第二通信模块连接用于接收usb3.0phy芯片验证平台反馈测试数据的外部设备;

4.根据权利要求3所述的usb3.0phy芯片验证测试板,其特征在于:所述usb3.0phy芯片验证平台包括usb3.0phy芯片,以及与usb3.0phy芯片相连的fmc接口、第一通信模块、jtag接口和接口模块;

5.根据权利要求4所述的usb3.0phy芯片验证测试板,其特征在于:所述fpga芯片的第十二bank区域通过第二fmc接口与usb3.0phy芯片的pipe接口中的tx_data、pclk进行信号连接;

6.根据权利要求5所述的usb3.0phy芯片验证测试板,其特征在于:所述fpga芯片采用xilinxkintex-7系列芯片。

技术总结

本技术涉及USB3.0测试,具体涉及一种USB3.0PHY芯片验证测试板,主控制器,对FPGA芯片和USB3.0PHY芯片验证平台进行控制,并接收USB3.0PHY芯片验证平台反馈的测试数据;FPGA芯片,用于对USB3.0PHY芯片验证平台的功能进行验证测试;USB3.0PHY芯片验证平台,搭载USB3.0PHY芯片,与FPGA芯片进行交互通信,对USB3.0PHY芯片进行配置,同时对USB3.0PHY芯片进行Debug调试,并向主控制器发送测试数据;本技术提供的技术方案能够有效克服现有技术所存在的验证测试成本较高,以及难以充分满足用户验证测试要求的缺陷。

技术研发人员:费勤顺

受保护的技术使用者:芯思原微电子有限公司

技术研发日:20230426

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!