一种SAR图像实时成像的硬件构架设计方法与流程

本发明涉及sar信号处理以及图像处理,特别涉及一种sar图像实时成像的硬件构架设计方法。

背景技术:

1、随着遥感技术以及合成孔径雷达(sar)成像技术研究的不断发展,sar图像实时成像成为了研究和应用领域的热点。sar图像实时成像需要在保证高成像质量的前提下,以尽可能高的集成度,小体积重量和功耗,完成实时成像处理。sar图像实时成像系统将大大减少传统sar成像所需的时间,从而可以保障对时效性有较高要求的应用。同时,当使用星载处理系统时,可通过对成像和识别以及目标提取后的信息进行回传,将大大减少传输所需的时延及带宽。有助于减少对载体的空间和负荷的需求,增加灵活性和续航能力。

2、中国科学院电子学研究所在其提出的专利申请文献“一种sar成像方法、装置及系统”(申请日:2013.07.15,申请号cn201310296193.5,公告号cn103472448a)中公开了一种sar成像装置。该装置内部包括多个单元,根据其步骤描述可知,该装置的优点是采用多个模块划分的方法从而提升gpu并行处理sar回波数的速度,但是,该装置仍然存在的不足之处是,该装置中的传输带宽相对于gpu的内存读取带宽较小,严重制约gpu的并行处理速度,对于大数据量的sar回波处理,为达到数据处理的实时性要求,gpu资源消耗将大幅增加,对sar成像装置而言,不利于工程化应用中的硬件平台搭建。

3、西安电子科技大学提出的专利申请“微型调频连续波实时sar成像系统”(专利申请号cn201310191614.8,公开号cn103336277a)公开了一种微型调频连续波实时sar成像系统,也详细描述了其内部的多个组成模块及其对应功能,但同样的,该专利申请仍然存在的不足是:fpga与单一的数据存储模块完成数据的写入,读取操作。由于在sar成像处理过程多,涉及到多次对图像数据的写入和读取,使得大量时间被消耗的数据的读写访问上,从而处理过程时间较长,造成数据延时较大,实时性较低。

4、更通用的来说,由于sar成像具备大数据量特点,其原始回波数据可能高达数十gb,且各种成像算法过程中,都涉及到对存储器的多次读写访问,当前工程实现上,大多是选择使用ddr作为存储器,但即便是ddr4,受限于dsp/fpga等外围控制器,其读写速率能实现2400mhz就非常高了,因此即便一组64bit位宽的ddr4存储器,其理论带宽19.2gb,考虑到访问时等待周期,开销等,实际带宽更小,更严重的是,由于ddr特点,按行顺序读写时效率尚可,但按列读写的效率非常低。比如xilinx ddr4控制器,按行顺序读写时效率可达90%,但按列读写时,效率仅为20%~30%;在sar成像算法中,由于需要对方位向和距离向分别进行fft和ifft等计算,等效于需要对回波数据矩阵进行按行和按列分别读写,因此,如何实现对存储器的高速访问成为了制约sar实时成像的关键问题。

技术实现思路

1、本申请的目的在于提供一种sar图像实时成像的硬件构架设计方法,在于解决sar成像处理过程耗时长的问题,其关键在于解决成像过程中减少存储器访问耗时太长的问题。

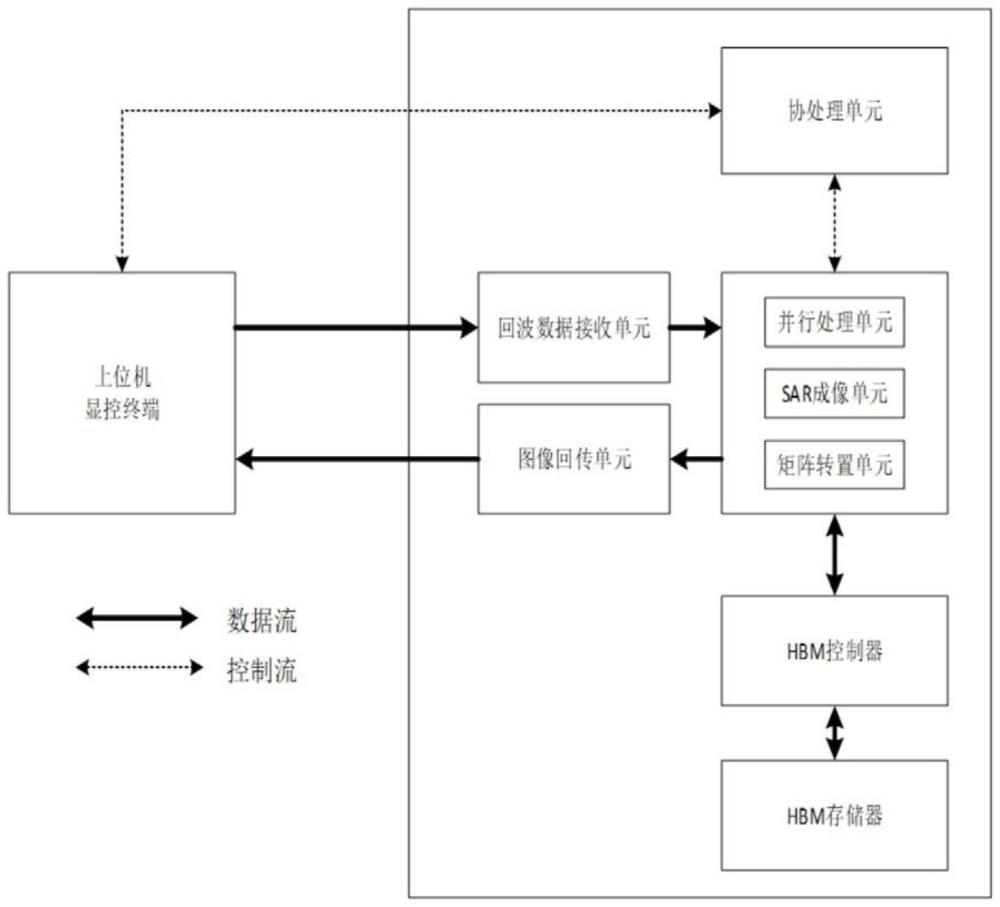

2、为实现上述目的,本申请提供如下技术方案:一种sar图像实时成像的硬件构架设计方法,包括回波数据接收单元、协处理单元、sar成像单元、并行处理单元、矩阵转置单元、hbm控制器单元、hbm存储器单元和图像回传单元,具体如下:

3、回波数据接收单元:用于从外部设备获取原始回波数据,通过高速数据接口实现实时数据传输;

4、协处理单元:用于配置成像过程中所需的各种条件参数,并可实现简单计算,该模块与外部设备上位机互联,通过以太网口或usb接口进行互联;

5、sar成像单元,完成sar成像算法的各个流程步骤;

6、并行处理单元:满足实时成像要求,利用fpga特性,将不同的数据分段后送至不同通道,并行计算后再将结果拼接,并行处理单元构建多个并行计算通道,以及各通道间的逻辑时序控制;

7、矩阵转置单元:是适配于sar成像算法中,需要对数据进行按行或者按列的不同访问方式,当按行访问完毕后,在fpga内部先利用高速ram将矩阵进行分块转置后存放入hbm;

8、hbm控制器单元,是实现对hbm物理存储区域的读写所需的控制模块,该模块可以对用户侧提供简单易用的用户接口,对hbm存储器侧提供满足存储器访问时序所需的信号接口,同时,内部生成物理访问地址,自动完成刷新操作,以及不同模式下的配置功能;

9、hbm存储器单元,是集成于fpga内部的存储器,由若干个ddr芯片堆叠在一起后和fpga封装在一起,实现大容量,高位宽的ddr组合阵列;

10、优选的,所述sar图像实时成像流程如下:通过回波数据接收单元得到sar目标回波并行数据;通过协处理单元、sar成像单元、并行处理单元得到方位向数据;通过矩阵转置单元对方位向数据进行转置操作;获取方位向校正数据;对方位向校正数据进行转置操作;得到sar图像。

11、综上,本发明的技术效果和优点:

12、本发明是基于hbm存储器的fpga硬件构架,优化了对服务器的访问速度,面对高分辨率或者是大幅宽的sar图像时,可实现实时处理,读写数据耗时可降低至毫秒量级,该硬件构架完全具备实时成像的能力。

技术特征:

1.一种sar图像实时成像的硬件构架设计方法,其特征在于:包括回波数据接收单元、协处理单元、sar成像单元、并行处理单元、矩阵转置单元、hbm控制器单元、hbm存储器单元和图像回传单元,具体如下:

2.根据权利要求1所述的一种sar图像实时成像的硬件构架设计方法,其特征在于:所述sar图像实时成像流程如下:通过回波数据接收单元得到sar目标回波并行数据;通过协处理单元、sar成像单元、并行处理单元得到方位向数据;通过矩阵转置单元对方位向数据进行转置操作;获取方位向校正数据;对方位向校正数据进行转置操作;得到sar图像。

技术总结

本发明公开了一种SAR图像实时成像的硬件构架设计方法,包括回波数据接收单元、协处理单元、SAR成像单元、并行处理单元、矩阵转置单元、HBM控制器单元、HBM存储器单元和图像回传单元,回波数据接收单元:用于从外部设备获取原始回波数据,协处理单元用于配置成像过程中所需的各种条件参数,SAR成像单元完成SAR成像算法的各个流程步骤;并行处理单元满足实时成像要求,将不同的数据分段后送至不同通道,并行计算后再将结果拼接,并行处理单元构建多个并行计算通道,以及各通道间的逻辑时序控制;矩阵转置单元是适配于SAR成像算法中,需要对数据进行按行或者按列的不同访问方式,当按行访问完毕后将矩阵进行分块转置后存放入HBM。本发明实现SAR实时成像。

技术研发人员:胡亮

受保护的技术使用者:北京普航科技有限公司

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!