授时方法及相关设备

1.本发明涉及授时技术领域,尤其涉及一种授时方法、装置、系统及相关设备。

背景技术:

2.随着多年经济的飞速发展,人类对矿产资源和油气资源的需求量已达到惊人的程度。然而,近地表浅层资源已基本被开采殆尽,因此人类在提高矿产和能源资源利用率的同时,向海洋进军是一个主要的发展趋势。

3.要对海底资源进行勘探,首要解决的问题就是提高地球物理仪器勘探的深度、精度和抗干扰能力。分布式地震电磁勘探系统由于支持同步采集地震和电磁的信息,所以可以有效结合地震和电磁数据,从不同维度对地质结构进行重构和解析,大幅度提升勘探的准确度。再者,这类勘探系统由于采用信息多次覆盖技术,可大幅度增强源信号的强度,从而提高勘探深度和精度。此外,该类勘探系统布点密集,一次布点就可完成对测区的测量,具有勘探效率高,横向分辨率高等优点。对于分布式勘探系统,各采集节点需要同步采集数据,并且时钟的同步误差越小,压制共模噪声就越有效,采集数据的质量就越有保证。在后续数据处理中,也需要在全局公共时钟下对采集的数据进行组合和分析,以进一步提高数据的信噪比。所以时钟同步技术是分布式地震电磁勘探系统的一项基本支撑技术,甚至是该类系统能被有效应用的先决条件。

4.目前在地球物理仪器中应用最广的时钟同步技术是gps授时法和ieee1588协议授时法。gps授时法就是地球物理仪器直接或者间接通过gps接收器来获取统一时钟。这种方法虽然具有同步误差小等优点,但由于海水对电磁信号的天然屏蔽性,使得工作在海底的勘探系统完全不能接收到gps信号,从而也就无法通过这种方法来完成授时。基于ieee1588协议的授时法是一种不依赖gps的授时法。在同步过程中,主节点周期发送时间数据包,当从节点接收到主节点的数据包后就立刻标记自身的本地时钟,然后计算自身本地时钟与主节点时钟的差值,用这个差值来对自身本地时钟的相位进行补偿,从而得到同步的时钟。这种方法同样依靠电磁波来传输信息,所以同样不能给工作在海底的分布式勘探系统提供授时。

5.综上所述,目前存在的海底授时法,要么先天性增加了操作不便性和授时成本,要么易受周围传输介质影响导致信号传输错误和衰减较快,增加了授时的不准确性和低效率性,总体上存在授时难度高的问题。

技术实现要素:

6.本发明实施例提供一种授时方法,旨在解决目前存在的海底授时法,要么先天性增加了操作不便性和授时成本,要么易受周围传输介质影响导致信号传输错误和衰减较快,增加了授时的不准确性和低效率性,总体上存在授时难度高的问题。通过采用分体式设计,将校准设备与执行设备分开设计,进一步降低了功耗,从而增加勘探装备在海底的续航时间,通过采用电磁波信号来进行解析和同步处理,降低同步误差,可以得到更准确授时信

息,不仅保证了长期授时漂移极少,而且也大幅度简化了授时的方式,从而解决了海底授时难度高的问题。

7.第一方面,本发明实施例提供一种授时方法,所述授时方法应用于海底勘探设备的授时系统中的校准设备,所述海底勘探设备的授时系统包括所述校准设备,以及与所述校准设备信号连接的执行设备,所述授时方法包括以下步骤:

8.将接收到的电磁波信号进行解析,得到第一解析信息;

9.对所述第一解析信息进行同步处理,得到授时信息;

10.将所述授时信息发送到所述执行设备中,以使所述执行设备根据所述授时信息进行授时校准,并在所述执行设备授时校准完成后,断开与所述执行设备的信号连接。

11.可选的,所述第一解析信息包括第一同步秒脉冲信号和报文信息,所述将接收到的电磁波信号进行解析,得到第一解析信息的步骤包括:

12.对所述电磁波信号进行解析,得到解析信息;

13.将所述解析信息进行转换,得到第一同步秒脉冲信号和报文信息。

14.可选的,所述授时信息包括第二同步秒脉冲和同步时间,所述报文信息包括所述同步时间,所述对所述第一解析信息进行同步处理,得到授时信息的步骤包括:

15.获取本地秒脉冲;

16.测量所述本地秒脉冲与所述第一同步秒脉冲之间的时间间隔值;

17.根据所述时间间隔值对所述本地秒脉冲所述第一同步秒脉冲进行同步,得到第二同步秒脉冲;

18.对所述报文信息进行解析处理,得到所述同步时间;

19.根据所述第二同步秒脉冲与所述同步时间,得到授时信息。

20.可选的,在所述根据所述时间间隔值对所述本地秒脉冲所述第一同步秒脉冲进行同步,得到第二同步秒脉冲的步骤之前,所述方法还包括:

21.通过预设的滤波算法压制所述第一同步脉冲的随机抖动。

22.可选的,所述测量所述本地秒脉冲与所述第一同步秒脉冲之间的时间间隔值的步骤包括:

23.测量所述第一同步秒脉冲的上升沿到所述下一个系统驱动时钟上升沿之间的时间,得到所述本地秒脉冲与所述第一同步秒脉冲之间的时间间隔值;或者

24.记录所述第一同步秒脉冲的上升沿到所述本地秒脉冲的上升沿之间的系统驱动时钟的数量,得到所述本地秒脉冲与所述第一同步秒脉冲之间的时间间隔值。

25.第二方面,本发明初稿例提供一种授时校准方法,所述授时方法应用于海底勘探设备的授时系统中的执行设备,所述海底勘探设备的授时系统包括所述执行设备,以及与所述执行设备信号连接的校准设备,所述校准设备在所述执行设备授时校准完成后,断开与所述执行设备的信号连接,所述授时校准方法包括以下步骤:

26.将接收到的授时信息进行解析,得到第二解析信息,所述校准设备将接收到的电磁波信号进行解析,得到第一解析信息,对所述第一解析信息进行同步处理,得到所述授时信息;

27.根据所述第二解析信息进行授时校准。

28.第三方面,本发明实施例提供一种授时装置,所述授时装置设置于海底勘探设备

的授时系统中的校准设备,所述海底勘探设备的授时系统包括所述校准设备,以及与所述校准设备信号连接的执行设备,所述授时装置包括:

29.第一接收模块,用于将接收到的电磁波信号进行解析,得到第一解析信息;

30.第一处理模块,用于对所述第一解析信息进行同步处理,得到授时信息;

31.发送模块,用于将所述授时信息发送到所述执行设备中,以使所述执行设备根据所述授时信息进行授时校准,并在所述执行设备授时校准完成后,断开与所述执行设备的信号连接。

32.第四方面,本发明实施例提供一种授时校准装置,所述授时校准装置设置于海底勘探设备的授时系统中的执行设备,所述海底勘探设备的授时系统包括所述执行设备,以及与所述执行设备信号连接的校准设备,所述校准设备在所述执行设备授时校准完成后,断开与所述执行设备的信号连接,所述授时校准装置包括:

33.第二接收模块,用于将接收到的授时信息进行解析,得到第二解析信息,所述校准设备将接收到的电磁波信号进行解析,得到第一解析信息,对所述第一解析信息进行同步处理,得到所述授时信息;

34.校准模块,用于根据所述第二解析信息进行授时校准。

35.第五方面,本发明实施例提供一种海底勘探设备的授时系统,包括:校准设备以及执行设备,所述校准设备与所述执行设备信号连接,所述校准设备在所述执行设备授时校准完成后,断开与所述执行设备的信号连接;

36.其中,所述校准设备执行如本发明实施例中任一项所述的授时方法中的步骤;

37.所述执行设备执行如本发明实施例中所述的授时校准方法中的步骤。

38.第六方面,本发明实施例提供一种计算机可读存储介质,所述计算机可读存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现如本发明实施例中任一项所述的授时方法中的步骤,或者所述计算机程序被处理器执行时实现如本发明实施例中所述的授时方法中的步骤。

39.本发明实施例中,授时方法应用于海底勘探设备的授时系统中的校准设备,所述海底勘探设备的授时系统包括校准设备,以及与校准设备信号连接的执行设备;校准设备将接收到的电磁波信号进行解析,得到第一解析信息;对第一解析信息进行同步处理,得到授时信息;将授时信息发送到执行设备中,以使执行设备根据授时信息进行授时校准,并在执行设备授时校准完成后,断开与执行设备的信号连接。通过采用分体式设计,将校准设备与执行设备分开设计,进一步降低了功耗,从而增加勘探装备在海底的续航时间,通过采用电磁波信号来进行解析和同步处理,降低同步误差,可以得到更准确的授时信息,不仅保证了长期授时漂移极少,而且也大幅度简化了授时的方式,从而解决了海底授时难度高的问题。

附图说明

40.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

41.图1是本发明实施例提供的一种授时系统的架构图;

42.图2是本发明实施例提供的一种fpga处理器的架构图;

43.图3是本发明实施例提供的一种cpld处理器的架构图;

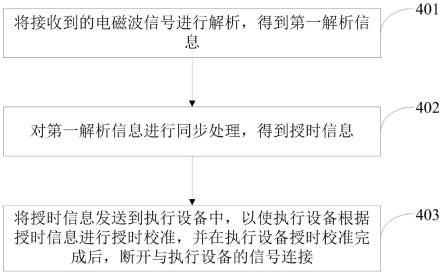

44.图4是本发明实施例提供的一种授时方法的流程图;

45.图5是本发明实施例提供的一种授时校准方法的流程图;

46.图6是本发明实施例提供的另一种授时方法的流程图;

47.图7是本发明实施例提供的一种授时装置的结构示意图;

48.图8是本发明实施例提供的一种授时校准装置的结构示意图;

49.图9是本发明实施例提供的一种电子设备的结构示意图。

具体实施方式

50.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

51.本发明实施例提供一种授时系统,该授时系统包括:校准设备以及执行设备,校准设备与执行设备信号连接,校准设备在执行设备授时校准完成后,断开与执行设备的信号连接。

52.在本发明实施例中,上述信号连接可以是线缆连接,上述校准设备中设置有校准电路板,上述执行设备中设置有执行电路板,上述执行设备可以设置在海底勘探装备中,上述校准设备则不安装在上述海底勘探装备中,所述校准设备只有在对所述执行设备的秒脉冲和时间进行校准时才通过线缆进行连接,当完成校准后校准设备会断开线缆,并与海底勘探装备分离。

53.具体的,请参考图1,图1是本发明实施例提供的一种授时系统的架构图,授时系统包括:单个校准电路板和多个执行电路板,上述校准电路板提供校准所需的第二同步秒脉冲lps1和同步时间t_fpga,上述执行电路板根据上述第二同步秒脉冲lps1和上述同步时间t_fpga对自身进行校准。

54.进一步,上述校准电路板包括:gps接收器、fpga处理器、da转换器、恒温晶振ocxo,其中,gps接收器的输出端与fpga处理器的输入端信号连接,fpga处理器的输出端与da转换器的输入端信号连接,da转换器的输出端与恒温晶振ocxo的输入端信号连接,恒温晶振ocxo的输出端与fpga处理器的输入端信号连接,可以看出,fpga处理器、da转换器、恒温晶振ocxo形成一个反馈环,该反馈环可以理解为一个锁定环,用于将本地时钟与gps接收器接收到的第一同步秒脉冲1pps进行同步锁定。fpga处理器的输出端还与执行电路板信号连接。上述信号连接可以是电连接或线缆连接。

55.gps接收器,用于接收gps系统发送的电磁波,并对电磁波进行解析,然后把解析的信息转换成第一同步秒脉冲1pps,以及包含有同步时间和gps锁定标识符等信息的报文;上述第一同步秒脉冲1pps通过管脚输出到fpga处理器,上述报文通过uart协议每秒周期性输出到fpga处理器。

56.fpga处理器,用于测量上述第一同步秒脉冲1pps信号的上升沿到上述fpga处理器

分频产生的本地秒脉冲lps2的上升沿之间的时间间隔值;还用于缓存测量的上述时间间隔值;还用于通过均值滤波算法压制上述第一同步秒脉冲1pps的随机抖动;还用于根据测量的上述时间间隔值计算出上述恒温晶振的频率准确度,并根据上述频率准确度所处的范围,计算上述da转换器的控制数据然后输出;还用于接收上述gps接收器输出的报文,并对报文进行解析和丢包等处理以获得gps接收器的锁定状态和同步时间t_fpga;还用于输出第二同步秒脉冲lps1和同步时间t_fpga。

57.da转换器,用于接收上述fpga处理器输出的上述控制数据,并转换成对应的电压值,从而对上述恒温晶振进行频率校准。

58.恒温晶振,用于给上述fpga处理器提供系统驱动时钟;还用于根据控制电压值调节自身频率。

59.上述执行电路板包括:cpld处理器以及芯片级原子钟,cpld处理器与芯片级原子钟之间信号连接。

60.cpld处理器,用于判断上述校准电路板是否通过线缆与上述执行电路板连接;还用于接收上述校准电路板输出的上述同步时间t_fpga,并把上述同步时间t_fpga按照uart协议和特定的数据发送顺序配置到上述芯片级原子钟的寄存器中以调节上述芯片级原子钟的时间;还用于接收上述校准电路板输出的第二同步秒脉冲lps1,对上述第二同步秒脉冲lps1进行若干路扩展,以适用于更大范围的同步授时;还用于接收上述芯片级原子钟每秒周期性输出的报文,并对报文进行解析,从而获取同步时间t_cpld;还用于对获取的上述同步时间t_cpld按照uart或spi等协议等进行输出,以适用于不同的应用场景;

61.芯片级原子钟,用于接收上述校准电路板输出的第二同步秒脉冲lps1和上述cpld处理器输出的同步时间t_fpga,并把自身输出的秒脉冲同步到上述第二同步秒脉冲lps1,把自身的时间同步到上述t_fpga上;还用于通过uart协议每秒周期性输出自身报文。

62.进一步的,fpga处理器是所述校准电路板的控制和计算核心,所有的功能单元均可以在该处理器中设计和实现。

63.具体的,请参考图2,图2是本发明实施例提供的一种fpga处理器的架构图,如图2所示,上述fpga处理器包括:dcm单元、时间间隔测量单元、时间信息量化单元、ram缓存单元、gps报文接收单元、校频计算单元、dac数据输出单元、同步输出单元。

64.dcm单元,用于对上述恒温晶振输出的波形进行倍频、去抖动、控延时和调相位等处理,以得到性能稳定和质量优良的系统驱动时钟,从而驱动所有单元工作。

65.时间间隔测量单元,用于测量上述gps接收器产生的秒脉冲1pps的上升沿与以上述恒温晶振为时钟源分频产生的本地秒脉冲上升沿之间的时间间隔信息。

66.时间转化模块(也可以称为时间信息量化单元),用于把测得的上述时间间隔信息量化为单位统一的时间间隔值。

67.ram缓存单元,用于对上述时间间隔值按照滤波算法的要求进行缓存。

68.gps报文接收单元,用于接收上述gps接收器输出的报文,并对报文进行解析和丢包等处理以获得gps接收器的锁定状态和同步时间t_fpga;当gps锁定时点亮绿色指示灯,上述校准电路板启动正常工作;当gps未锁定时点亮红色指示灯,上述校准电路板暂停工作,保存当前状态不变。

69.校频计算单元,用于采用均值滤波算法对1pps的随机抖动进行压制;还用于根据

上述时间间隔值计算出上述恒温晶振的频率准确度,并根据频率准确度所处的范围,计算上述da转换器的控制数据。

70.dac数据输出单元,用于把上述校频计算单元产生的控制数据按照da转换器适用的传输协议输出给da转换器。

71.同步输出单元,用于对上述系统驱动时钟分频以产生本地秒脉冲,以及在本地秒脉冲与第一同步秒脉冲同步时,输出第二同步秒脉冲;还用于把上述gps报文接收单元获取的同步时间t_fpga按照uart协议输出给上述执行电路板以完成对时间的校准。

72.复位模块,用于对fpga处理器进行复位。

73.进一步的,上述时间间隔测量单元可以包括精测量模块和粗测量模块;上述精测量模块可以通过预设方法测量第一同步秒脉冲1pps上升沿到下一个系统驱动时钟上升沿之间的时间;上述粗测量模块是通过构建计数器来记录第一同步秒脉冲1pps上升沿到本地秒脉冲上升沿之间系统驱动时钟的整数个数。

74.上述精测量模块的预设方法可以是延迟线法或高频相移法。

75.具体的,上述延迟线法具体步骤为:首先是准备阶段,在上述fpga处理器中通过设置多位加法器构建一条进位延迟线来测量时间间隔,然后把每个二进制加法器通过进位线级联,所有二进制加法器的被加数位均设置为1,加数位均设置为0,并且把上述最低位二进制加法器的进位输入端与第一同步秒脉冲1pps连接;然后是测量阶段,当第一同步秒脉冲1pps信号的上升沿到来并在延迟线上传输时,加法器的输出端就会从低位到高位依次由1变为0,通过统计输出端0的个数就能完成时间信息精测量。

76.上述高频相移法为:首先通过上述dcm单元把上述恒温晶振输入的方波倍频到较高的频率,然后通过上述dcm单元把较高频率的方波分别调相90度、180度和270度,最后根据第一同步秒脉冲1pps的上升沿所处的较高频率方波的相位区间估算出时间间隔。

77.在本发明实施例中,在准备阶段,通过fpga开发软件的布局布线仿真或外接专用时延芯片测得每位延迟线的时间参数,根据上述粗测量计数器的系统驱动时钟频率计算系统驱动时钟的周期参数。在计算阶段,结合时间间隔信息和上述的时间参数、周期参数,通过加法和移位的方式可以计算出单位统一的上述时间间隔值。

78.进一步的,上述ram缓存单元包括ram存储器和ram控制器;上述ram存储器是调用上述fpga处理器内部资源建立而成,用来缓存上述时间信息量化单元输出的时间间隔值;上述ram控制器是根据滤波算法的要求来设计ram存储器的读写。

79.进一步的,在上述校频计算单元所采用的均值滤波算法中,可以记上述时间信息量化单元第i次输出的时间间隔值为t(i),可以按照下述公式计算第i次的时间间隔均值a(i):

[0080][0081]

其中m》0是滑动窗口的值,该值可根据实际使用效果来选取。

[0082]

上述频率准确度的具体计算方法中,可以按照如下公式计算第i次恒温晶振的频率准确度s1(i):

[0083][0084]

其中t0是标准的秒脉冲周期,即为1s。

[0085]

上述频率准确度s1(i)有下述的变形形式:

[0086]

s2(i)=mt0s1(i)=t(i)-t(i-m)

[0087]

其中s2(i)为s1(i)的变形形式,s2(i)同样反映了上述恒温晶振的频率准确度信息。

[0088]

在上述da转换器的控制数据的具体计算步骤中,可以首先任意初始化一个控制数据;然后计算上述s1的数值,根据s1所处的不同数量级,设置对应的恒温晶振的调节步长和调节周期,步长为正,表明频率偏低,步长为负,表明频率偏高;计算s2的数值,用s2替代s1判断恒温晶振的频率准确度所处的数量级;根据s2的数值选取调节步长和调节周期,用当前的控制数据加上调节步长就可更新控制数据。

[0089]

进一步的,cpld处理器是所述执行电路板的控制核心,所有的功能单元均在该处理器中设计和实现。

[0090]

具体的,请参考图3,图3是本发明实施例提供的一种cpld处理器的架构图,如图3所示,cpld处理器包括:校准时钟收发单元、报文接收单元、内核单元、同步时间输出单元、秒脉冲扩展单元。

[0091]

校准时钟收发单元,在上述cpld处理器内核模块的控制下,一方面按照uart协议接收上述校准电路板发送的上述同步时间t_fpga,一方面按照uart协议和特定的数据发送顺序发送上述同步时间t_fpga到上述芯片级原子钟,以完成对芯片级原子钟的时间调节。

[0092]

报文接收单元,接收上述芯片级原子钟发送的周期性报文,并把上述周期性报文输出给内核单元。

[0093]

内核单元,优先用于检测上述校准电路板输出的上述第二同步秒脉冲lps1的上升沿,以判断上述校准电路板是否与执行电路板连接。当检测到第二同步秒脉冲lps1的上升沿时,表明校准电路板与执行电路板通过线缆连接,这时触发上述校准时钟收发单元工作,停止上述报文接收单元、上述同步时间输出单元和上述秒脉冲扩展单元工作;当没有检测到上升沿时,表明上述校准电路板断开,这时对上述芯片级原子钟输出的报文进行解析和丢包等处理,提取出同步时间,并通过上述同步时间输出单元把同步时间输出,同时触发上述秒脉冲扩展单元工作,停止上述校准时钟收发单元工作。

[0094]

同步时间输出单元,用于把上述内核单元输出的上述同步时间t_cpld按照uart或spi等协议输出,以提供授时服务。

[0095]

秒脉冲扩展单元,在cpld处理器内核模块的控制下,用于把上述芯片级原子钟输出的秒脉冲通过扩展器复制成若干份秒脉冲,然后让每一路秒脉冲通过上述fpga处理器内部的缓冲器输出,以增加每路同步秒脉冲的驱动能力。

[0096]

在一种可能的实施例中,上述cpld处理器可以单独存在上述执行电路板中,也可以把上述cpld处理器中的功能单元集成到其他处理器中,而不需要cpld处理器。

[0097]

本发明实施例与现有技术相比,提供的一种授时系统,应用于海底勘探装备的长期稳定授时,通过采用分体式设计,即校准电路板与执行电路板分开设计,进一步降低了功耗以增加勘探装备在海底的续航时间;通过采用gps与恒温晶振协同的方式提供校准所需

的同步秒脉冲和同步时间,并采用均值滤波的方法对gps秒脉冲1pps的随机抖动进行压制,进一降低了执行电路板的同步误差;通过采用芯片级原子钟与cpld芯片协作的方式来给海底勘探装备提供授时,不仅保证了长期授时漂移极少,而且也大幅度简化了授时的方式。此外,由于授时服务具有一定的普遍性,这使得本授时系统不仅适用于海底勘探装备,对室内工厂、井下隧道这种较为密闭性的空间同样具有很好的适用性。

[0098]

本发明实施例还提供一种授时方法,所述授时方法应用于海底勘探设备的授时系统中的校准设备,所述海底勘探设备的授时系统包括所述校准设备,以及与所述校准设备信号连接的执行设备,请参考图4,图4是本发明实施例提供的一种授时方法的流程图,如图4所示,所述授时方法包括以下步骤:

[0099]

401、将接收到的电磁波信号进行解析,得到第一解析信息。

[0100]

在本发明实施例中,上述电磁波信号可以是gps系统发送的电磁波信号,上述电磁波信号中包括第一同步秒脉冲1pps和包含有同步时间和gps锁定标识符等信息的报文,可以通过对电磁波信号进行解析,得到第一同步秒脉冲1pps和包含有同步时间和gps锁定标识符等信息的报文作为第一解析信息。

[0101]

在一种可能的实施例中,在步骤402之前,可以校准电路板和某一个执行电路板通过线缆连接,并上电启动。初始化校准电路板和执行电路板。初始化包括对一些控制数据设置初始值,复位寄存器和状态机的状态等。判断gps是否锁定。只有当gps锁定时,校准电路板中的测量和计算才有意义。如果gps锁定,则进入步骤402;如果gps没有锁定,则保持当前状态不变。校准电路板和执行电路板处在待机的状态,所有的寄存器和控制参数均保持当前状态不变。

[0102]

402、对第一解析信息进行同步处理,得到授时信息。

[0103]

在本发明实施例中,可以将第一解析信息中的第一同步秒脉冲与本地秒脉冲进行同步处理,使得校准设备的时钟驱动系统与gps系统的时钟同步,输出更准确的授时信息。

[0104]

403、将授时信息发送到执行设备中,以使执行设备根据授时信息进行授时校准,并在执行设备授时校准完成后,断开与执行设备的信号连接。

[0105]

在本发明实施例中,在得到授时信息后,可以将授时信息通过线缆传输到执行设备中,使得执行设备根据接收到的授时信息进行解析和授时校准。

[0106]

在执行设备授时校准完成后,断开与执行设备的信号连接,可以不需要对校准设备进行供电,从而使得执行设备所在海底勘探装备的耗电量降低,提高海底勘探装备的使用时长。

[0107]

在本发明实施例中,校准设备将接收到的电磁波信号进行解析,得到第一解析信息;对第一解析信息进行同步处理,得到授时信息;将授时信息发送到执行设备中,以使执行设备根据授时信息进行授时校准,并在执行设备授时校准完成后,断开与执行设备的信号连接。通过采用分体式设计,将校准设备与执行设备分开设计,进一步降低了功耗,从而增加勘探装备在海底的续航时间,通过采用电磁波信号来进行解析和同步处理,降低同步误差,可以得到更准确的授时信息,不仅保证了长期授时漂移极少,而且也大幅度简化了授时的方式,从而解决了海底授时难度高的问题。

[0108]

可选的,上述第一解析信息包括第一同步秒脉冲信号和报文信息,上述将接收到的电磁波信号进行解析,得到第一解析信息的步骤中,可以对上述电磁波信号进行解析,得

到解析信息;将上述解析信息进行转换,得到第一同步秒脉冲信号和报文信息。

[0109]

具体的,可以通过gps接收器接收gps系统发送的电磁波,并对电磁波进行解析,然后把解析的信息转换成第一同步秒脉冲1pps,以及包含有同步时间和gps锁定标识符等信息的报文。其中,第一同步秒脉冲1pps可以通过管脚输出,报文可以通过uart协议每秒周期性输出。

[0110]

可选的,上述授时信息包括第二同步秒脉冲和同步时间,上述报文信息包括上述同步时间,上述对上述第一解析信息进行同步处理,得到授时信息的步骤中,可以获取本地秒脉冲;测量上述本地秒脉冲与上述第一同步秒脉冲之间的时间间隔值;根据上述时间间隔值对上述本地秒脉冲上述第一同步秒脉冲进行同步,得到第二同步秒脉冲;对上述报文信息进行解析处理,得到上述同步时间;根据上述第二同步秒脉冲与上述同步时间,得到授时信息。

[0111]

具体的,可以通过fpga处理器测量上述第一同步秒脉冲1pps信号的上升沿到上述fpga处理器分频产生的本地秒脉冲lps2的上升沿之间的时间间隔值,并缓存测量的上述时间间隔值,根据测量的上述时间间隔值计算出上述恒温晶振的频率准确度,并根据上述频率准确度所处的范围,计算上述da转换器的控制数据然后输出;根据上述gps接收器输出的报文,并对报文进行解析和丢包等处理以获得gps接收器的锁定状态和同步时间t_fpga;还用于输出第二同步秒脉冲lps1和同步时间t_fpga。

[0112]

可选的,在上述根据上述时间间隔值对上述本地秒脉冲上述第一同步秒脉冲进行同步,得到第二同步秒脉冲的步骤之前,还可以通过预设的滤波算法压制上述第一同步脉冲的随机抖动。

[0113]

具体的,上述滤波算法可以是均值滤波算法或线性滤波算法,本发明实施例优选为均值滤波算法。更具体的,可以通过fpga处理器中预设的均值滤波算法压制上述第一同步秒脉冲1pps的随机抖动。

[0114]

进一步的,在上述校频计算单元所采用的均值滤波算法中,可以记上述时间信息量化单元第i次输出的时间间隔值为t(i),可以按照下述公式计算第i次的时间间隔均值a(i):

[0115][0116]

其中m》0是滑动窗口的值,该值可根据实际使用效果来选取。

[0117]

可选的,上述测量上述本地秒脉冲与上述第一同步秒脉冲之间的时间间隔值的步骤中,可以测量上述第一同步秒脉冲的上升沿到上述下一个系统驱动时钟上升沿之间的时间,得到上述本地秒脉冲与上述第一同步秒脉冲之间的时间间隔值;或者记录上述第一同步秒脉冲的上升沿到上述本地秒脉冲的上升沿之间的系统驱动时钟的数量,得到上述本地秒脉冲与上述第一同步秒脉冲之间的时间间隔值。

[0118]

具体的,上述测量上述本地秒脉冲与上述第一同步秒脉冲之间的时间间隔值的步骤中,可以采用精测量与粗测量中至少一种测量方法来得到上述时间间隔值。

[0119]

在精测量中,可以测量上述第一同步秒脉冲的上升沿到上述下一个系统驱动时钟上升沿之间的时间,得到上述本地秒脉冲与上述第一同步秒脉冲之间的时间间隔值。在粗测量中,记录上述第一同步秒脉冲的上升沿到上述本地秒脉冲的上升沿之间的系统驱动时

钟的数量,得到上述本地秒脉冲与上述第一同步秒脉冲之间的时间间隔值。

[0120]

进一步的,上述精测量可以是延迟线法或高频相移法。

[0121]

具体的,上述延迟线法具体步骤为:首先是准备阶段,在上述fpga处理器中通过设置多位加法器构建一条进位延迟线来测量时间间隔,然后把每个二进制加法器通过进位线级联,所有二进制加法器的被加数位均设置为1,加数位均设置为0,并且把上述最低位二进制加法器的进位输入端与秒脉冲1pps连接;然后是测量阶段,当第一同步秒脉冲1pps信号的上升沿到来并在延迟线上传输时,加法器的输出端就会从低位到高位依次由1变为0,通过统计输出端0的个数就能完成时间信息精测量。

[0122]

上述高频相移法为:首先通过上述dcm单元把上述恒温晶振输入的方波倍频到较高的频率,然后通过上述dcm单元把较高频率的方波分别调相90度、180度和270度,最后根据第一同步秒脉冲1pps的上升沿所处的较高频率方波的相位区间估算出时间间隔。

[0123]

在本发明实施例中,在准备阶段,通过fpga开发软件的布局布线仿真或外接专用时延芯片测得每位延迟线的时间参数,根据上述粗测量计数器的系统驱动时钟频率计算系统驱动时钟的周期参数。在计算阶段,结合时间间隔信息和上述的时间参数、周期参数,通过加法和移位的方式可以计算出单位统一的上述时间间隔值。

[0124]

本发明实施例还提供一种授时校准方法,上述授时校准方法应用于海底勘探设备的授时系统中的执行设备,上述海底勘探设备的授时系统包括上述执行设备,以及与上述执行设备信号连接的校准设备,校准设备在上述执行设备授时校准完成后,断开与上述执行设备的信号连接,请参考图5,图5是本发明实施例提供的一种授时校准方法的流程图,如图5所示,上述授时校准方法包括以下步骤:

[0125]

501、将接收到的授时信息进行解析,得到第二解析信息。

[0126]

在本发明实施例中,校准设备将接收到的电磁波信号进行解析,得到第一解析信息,对第一解析信息进行同步处理,得到授时信息后,将授时信息发送到执行设备。

[0127]

502、根据第二解析信息进行授时校准。

[0128]

具体的,执行设备在接收到授时信息后,可以将授时信息解析为第二同步秒脉冲和同步时间,根据第二同步秒脉冲和同步时间进行授时校准。校准板完成对恒温晶振频率的校准后就输出第二同步秒脉冲lps1和同步时间到执行电路板。完成此步骤后,判断执行电路板是否检测到第二同步秒脉冲lps1的上升沿。执行电路板会周期性的检查同步秒脉冲lps1的上升沿。当检测到第二同步秒脉冲lps1的上升沿信号后,表明校准电路板在位,即校准电路板通过线缆与执行电路板连接。当没检测到第二同步秒脉冲lps1的上升沿信号时,表明校准电路板已断开,读取芯片级原子钟的报文,解析出同步时间。芯片级原子钟会每秒输出自己的报文,报文中就含有时间信息。为获得同步时间,需要剔除报文中的其它信息,然后保留同步时间,不再对芯片级原子钟校准。对芯片级原子钟的秒脉冲进行同步。调节芯片级原子钟的时间。接收校准板输出的同步时间,然后把这个同步时间写入到芯片级原子钟对应的寄存器中,以完成芯片级原子钟的时间调节。读取芯片级原子钟的报文,解析出同步时间。芯片级原子钟会每秒输出自己的报文,报文中就含有时间信息。为获得同步时间,需要剔除报文中的其它信息,然后保留同步时间。扩展芯片级原子钟输入的秒脉冲至若干份,通过缓冲器输出。通过扩展和复制的方式来提高芯片级原子钟输出的秒脉冲的驱动能力和驱动范围。按照uart或spi等协议在秒脉冲的中间时刻输出同步时间。当检测到芯片级

原子钟输出的同步秒脉冲的上升沿后,启动计数器记录时间。当经过0.5s后,这时就按照uart或spi等协议输出同步时间。

[0129]

在本发明实施例中,通过采用分体式设计,将校准设备与执行设备分开设计,进一步降低了功耗,从而增加勘探装备在海底的续航时间,通过采用电磁波信号来进行解析和同步处理,降低同步误差,可以得到更准确的授时信息,不仅保证了长期授时漂移极少,而且也大幅度简化了授时的方式,从而解决了海底授时难度高的问题。

[0130]

本发明实施例还提供另一种授时方法,应用于上述授时系统,上述授时系统包括:单个校准电路板和多个执行电路板,上述校准电路板提供校准所需的第二同步秒脉冲lps1和同步时间t_fpga,上述执行电路板根据上述第二同步秒脉冲lps1和上述同步时间t_fpga对自身进行校准。请参考图6,图6是本发明实施例提供的另一种授时方法,如图6所示,所述授时方法包括:

[0131]

步骤601,校准电路板和某一个执行电路板通过线缆连接,并上电启动。

[0132]

步骤602,初始化校准电路板和执行电路板。初始化包括对一些控制数据设置初始值,复位寄存器和状态机的状态等。

[0133]

步骤603,判断gps是否锁定。只有当gps锁定时,校准电路板中的测量和计算才有意义。如果gps锁定,则进入步骤605;如果没有,则进入步骤604。

[0134]

步骤604,保持当前状态不变。校准电路板和执行电路板处在待机的状态,所有的寄存器和控制参数均保持当前状态不变。

[0135]

步骤605,测量lps1与1pps之间上升沿的时间间隔信息。通过粗测量和精测量结合的方式精确测出本地秒脉冲lps1的上升沿与gps接收器输出的秒脉冲1pps的上升沿之间的时间间隔信息。完成测量后进入步骤606。

[0136]

步骤606,把时间间隔信息量化为单位统一的时间间隔值。通过结合时间间隔信息和一些时间参数,计算得到单位统一的时间间隔值。完成计算后进入步骤607。

[0137]

步骤607,把时间间隔值存入到ram存储器中。在ram控制器的作用下,把时间间隔值按照滤波算法和计算频率准确度的要求存入到ram存储器中。完成存储后,进入步骤608。

[0138]

步骤608,读取滤波窗口两端的时间间隔值,并滑动窗口。根据滤波算法和频率准确度的计算方法,需要同时读取窗口两端的时间间隔值,然后把窗口滑动到下一个地址位。完成此步骤后,进入步骤609。

[0139]

步骤609,计算系统驱动时钟的频率准确度。根据频率准确度公式计算出系统驱动时钟的频率准确度,完成计算后则进入步骤10。

[0140]

步骤610,判断频率准确度范围,从调节列表中选取调节步长和调节周期。根据计算得到的频率准确度判断该值所处的范围区间,完成确定后,从调节列表中读出对应的调节步长和周期。频率准确度越高,调节步长越小,调节周期越大。完成此步骤后,进入步骤611。

[0141]

步骤611,读取当前保存的dac控制数据,结合调节参数计算新的控制数据。读取当前保存的控制数据,然后根据调节步长和调节周期计算得到新的控制数据。调节周期表示每次计算新的控制数据的时间。完成此步骤后,进入步骤612。

[0142]

步骤612,通过既定协议把控制数据输出到dac中。得到新的控制数据后,按照既定的协议,一般为spi或uart协议,把数据输入到dac中。完成此步骤后,进入步骤613。

[0143]

步骤613,dac把对应控制数据转换为模拟电压,以调节恒温晶振的频率。dac接收到控制数据后,会转换为对应的模拟电压,然后作用到恒温晶振的频率调节端。该调节端是通过控制恒温晶振的温度来调节频率的。完成此步骤后,进入步骤614。

[0144]

步骤614,判断频率准确度是否满足设定要求。如果计算得到的频率准确度达到了设定要求,则表明频率准确度达到了要求,进入步骤615;如果没有达到设定要求,则继续等待。

[0145]

步骤615,频率锁定指示灯由亮红色变为亮绿色。当频率准确度达到了设定要求时,就表明系统驱动时钟的频率已经被锁定,这时对应的指示灯由红变绿。完成此步骤后,进入步骤616。

[0146]

步骤616,输出同步秒脉冲和同步时间到执行板。校准板完成对恒温晶振频率的校准后就输出同步秒脉冲lps1和同步时间到执行电路板。完成此步骤后,进入步骤617。

[0147]

步骤617,判断执行电路板是否检测到lps1的上升沿。执行电路板会周期性的检查同步秒脉冲lps1的上升沿。当检测到lps1的上升沿信号后,表明校准电路板在位,即校准电路板通过线缆与执行电路板连接,这时进入步骤618。当没检测到时,表明校准电路板已断开,这时进入步骤620,不再对芯片级原子钟校准。

[0148]

步骤618,对芯片级原子钟的秒脉冲进行同步。

[0149]

步骤619,调节芯片级原子钟的时间。接收校准板输出的同步时间,然后把这个同步时间写入到芯片级原子钟对应的寄存器中,以完成芯片级原子钟的时间调节。完成此步骤后,进入步骤620。

[0150]

步骤620,读取芯片级原子钟的报文,解析出同步时间。芯片级原子钟会每秒输出自己的报文,报文中就含有时间信息。为获得同步时间,需要剔除报文中的其它信息,然后保留同步时间。完成此步骤后,进入步骤621。

[0151]

步骤621,扩展芯片级原子钟输入的秒脉冲至若干份,通过缓冲器输出。通过扩展和复制的方式来提高芯片级原子钟输出的秒脉冲的驱动能力和驱动范围。完成此步骤后,进入步骤622。

[0152]

步骤622,按照uart或spi等协议在秒脉冲的中间时刻输出同步时间。当检测到芯片级原子钟输出的同步秒脉冲的上升沿后,启动计数器记录时间。当经过0.5s后,这时就按照uart或spi等协议输出同步时间。完成此步骤后,进入步骤623。

[0153]

步骤623,返回。返回到步骤603,重新判断gps状态是否锁定,等待下一次的触发。

[0154]

综上所述,本技术提供的一种应用于海底勘探装备的长稳定授时系统,通过采用分体式设计,即校准电路板与执行电路板分开设计,进一步降低了功耗以增加勘探装备在海底的续航时间;通过采用gps与恒温晶振协同的方式提供校准所需的同步秒脉冲和同步时间,并采用均值滤波的方法对gps秒脉冲1pps的随机抖动进行压制,进一降低了执行电路板的同步误差;通过采用芯片级原子钟与cpld芯片协作的方式来给海底勘探装备提供授时,不仅保证了长期授时漂移极少,而且也大幅度简化了授时的方式。此外,由于授时服务具有一定的普遍性,这使得本授时系统不仅适用于海底勘探装备,对室内工厂、井下隧道这种较为密闭性的空间同样具有很好的适用性。

[0155]

可选的,请参见图7,图7是本发明实施例提供的一种授时装置的结构示意图,如图7所示,授时装置包括:

[0156]

第一接收模块701,用于将接收到的电磁波信号进行解析,得到第一解析信息;

[0157]

第一处理模块702,用于对所述第一解析信息进行同步处理,得到授时信息;

[0158]

发送模块703,用于将所述授时信息发送到所述执行设备中,以使所述执行设备根据所述授时信息进行授时校准,并在所述执行设备授时校准完成后,断开与所述执行设备的信号连接。

[0159]

可选的,所述第一解析信息包括第一同步秒脉冲信号和报文信息,所述第一接收模块701,包括:

[0160]

解析子模块,用于对所述电磁波信号进行解析,得到解析信息;

[0161]

转换子模块,用于将所述解析信息进行转换,得到第一同步秒脉冲信号和报文信息。

[0162]

可选的,所述授时信息包括第二同步秒脉冲和同步时间,所述报文信息包括所述同步时间,所述第一处理模块702,包括:

[0163]

获取子模块,用于获取本地秒脉冲;

[0164]

测量子模块,用于测量所述本地秒脉冲与所述第一同步秒脉冲之间的时间间隔值;

[0165]

同步子模块,用于根据所述时间间隔值对所述本地秒脉冲所述第一同步秒脉冲进行同步,得到第二同步秒脉冲;

[0166]

第一处理子模块,用于对所述报文信息进行解析处理,得到所述同步时间;

[0167]

第二处理子模块,用于根据所述第二同步秒脉冲与所述同步时间,得到授时信息。

[0168]

可选的,所述装置还包括:

[0169]

压制模块,用于通过预设的滤波算法压制所述第一同步脉冲的随机抖动。

[0170]

可选的,所述测量子模块,包括:

[0171]

测量单元,用于测量所述第一同步秒脉冲的上升沿到所述下一个系统驱动时钟上升沿之间的时间,得到所述本地秒脉冲与所述第一同步秒脉冲之间的时间间隔值;或者

[0172]

记录单元,用于记录所述第一同步秒脉冲的上升沿到所述本地秒脉冲的上升沿之间的系统驱动时钟的数量,得到所述本地秒脉冲与所述第一同步秒脉冲之间的时间间隔值

[0173]

可选的,请参见图8,图8是本发明实施例提供的一种授时校准装置的结构示意图,如图8所示,授时校准装置包括:

[0174]

第二接收模块801,用于将接收到的授时信息进行解析,得到第二解析信息,所述校准设备将接收到的电磁波信号进行解析,得到第一解析信息,对所述第一解析信息进行同步处理,得到所述授时信息;

[0175]

校准模块802,用于根据所述第二解析信息进行授时校准

[0176]

需要说明的是,本发明实施例提供的授时装置可以应用于可以进行图层级的业务分析的智能手机、电脑、服务器等设备。

[0177]

本发明实施例提供的授时装置能够实现上述方法实施例中授时方法实现的各个过程,且可以达到相同的有益效果。为避免重复,这里不再赘述。

[0178]

参见图9,图9是本发明实施例提供的一种电子设备的结构示意图,如图9所示,包括:存储器902、处理器901及存储在存储器902上并可在处理器901上运行的授时方法的计算机程序,其中:

[0179]

将接收到的电磁波信号进行解析,得到第一解析信息;

[0180]

对所述第一解析信息进行同步处理,得到授时信息;

[0181]

将所述授时信息发送到所述执行设备中,以使所述执行设备根据所述授时信息进行授时校准,并在所述执行设备授时校准完成后,断开与所述执行设备的信号连接。

[0182]

可选的,所述第一解析信息包括第一同步秒脉冲信号和报文信息,处理器901执行的所述将接收到的电磁波信号进行解析,得到第一解析信息的步骤包括:

[0183]

对所述电磁波信号进行解析,得到解析信息;

[0184]

将所述解析信息进行转换,得到第一同步秒脉冲信号和报文信息。

[0185]

可选的,所述授时信息包括第二同步秒脉冲和同步时间,所述报文信息包括所述同步时间,处理器901执行的所述对所述第一解析信息进行同步处理,得到授时信息的步骤包括:

[0186]

获取本地秒脉冲;

[0187]

测量所述本地秒脉冲与所述第一同步秒脉冲之间的时间间隔值;

[0188]

根据所述时间间隔值对所述本地秒脉冲所述第一同步秒脉冲进行同步,得到第二同步秒脉冲;

[0189]

对所述报文信息进行解析处理,得到所述同步时间;

[0190]

根据所述第二同步秒脉冲与所述同步时间,得到授时信息。

[0191]

可选的,在所述根据所述时间间隔值对所述本地秒脉冲所述第一同步秒脉冲进行同步,得到第二同步秒脉冲的步骤之前,处理器901执行的所述方法还包括:

[0192]

通过预设的滤波算法压制所述第一同步脉冲的随机抖动。

[0193]

可选的,处理器901执行的所述测量所述本地秒脉冲与所述第一同步秒脉冲之间的时间间隔值的步骤包括:

[0194]

测量所述第一同步秒脉冲的上升沿到所述下一个系统驱动时钟上升沿之间的时间,得到所述本地秒脉冲与所述第一同步秒脉冲之间的时间间隔值;或者

[0195]

记录所述第一同步秒脉冲的上升沿到所述本地秒脉冲的上升沿之间的系统驱动时钟的数量,得到所述本地秒脉冲与所述第一同步秒脉冲之间的时间间隔值。

[0196]

或者,处理器901用于调用存储器902存储的计算机程序,执行如下步骤:

[0197]

将接收到的授时信息进行解析,得到第二解析信息,所述校准设备将接收到的电磁波信号进行解析,得到第一解析信息,对所述第一解析信息进行同步处理,得到所述授时信息;

[0198]

根据所述第二解析信息进行授时校准。

[0199]

需要说明的是,本发明实施例提供的电子设备可以应用于可以进行授时的智能手机、电脑、服务器等设备。

[0200]

本发明实施例提供的电子设备能够实现上述方法实施例中授时方法实现的各个过程,且可以达到相同的有益效果。为避免重复,这里不再赘述。

[0201]

本发明实施例还提供一种计算机可读存储介质,计算机可读存储介质上存储有计算机程序,该计算机程序被处理器执行时实现本发明实施例提供的授时方法或应用端授时方法的各个过程,且能达到相同的技术效果,为避免重复,这里不再赘述。

[0202]

本领域普通技术人员可以理解实现上述实施例方法中的全部或部分流程,是可以

通过计算机程序来指令相关的硬件来完成,的程序可存储于一计算机可读取存储介质中,该程序在执行时,可包括如上述各方法的实施例的流程。其中,的存储介质可为磁碟、光盘、只读存储记忆体(read-only memory,rom)或随机存取存储器(random access memory,简称ram)等。

[0203]

以上所揭露的仅为本发明较佳实施例而已,当然不能以此来限定本发明之权利范围,因此依本发明权利要求所作的等同变化,仍属本发明所涵盖的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1