基于异步通信的时钟校正方法及电能表与流程

本发明涉及一种智能电能表的内部时钟的校正方法,还涉及一种电能表。

背景技术:

1、时钟系统是智能电能表重要的硬件组成部分,它为整个电能表的软件功能运转提供稳定的时钟节拍,保证程序稳定、有序的运行。作为时钟系统核心的晶体振荡器具有极高的准确性,非常适合作为电能表系统的时钟源。随着用电环境的越来越复杂,用户对电能表的稳定性也提出了更高的要求。例如,更快的通信速度,更准确的时间,更加灵敏的电压,电流数值采集,更加准确的电能计量等等。上述功能的实现,都离不开晶体精确的时钟信号。

2、但是,一旦晶体振荡器发生故障而停振,将会导致电能表数据错乱,通信失败,拉合闸误动作甚至其它一些不可预料的严重后果。电能表在晶体停振后,一般会切换使用内部高频rc作为临时的时钟源,但是该时钟源精度较低,并且容易受温度影响,如果误差超过一定限度,将会导致mcu与外设通信异常,无法保证电能表正常工作运行。现有技术中暂无实时校正内部高频rc精度的有效手段。

技术实现思路

1、本发明提出了一种基于异步通信的时钟校正方法及电能表,其目的是:对内部高频rc的精度进行实时校正,解决内部高频rc精度低、无法保证电能表正常运行的问题。

2、本发明技术方案如下:

3、一种基于异步通信的时钟校正方法,用于校正mcu内部rc的时钟误差;启用内部rc作为mcu的时钟源后,mcu接收外部模块通过异步通信方式发送的数据,所述外部模块内部带有独立的时钟源,所述mcu通过接收数据时高低电平变化特征之间的时长计算出内部rc的偏差值,然后基于该偏差值对内部rc进行校正。

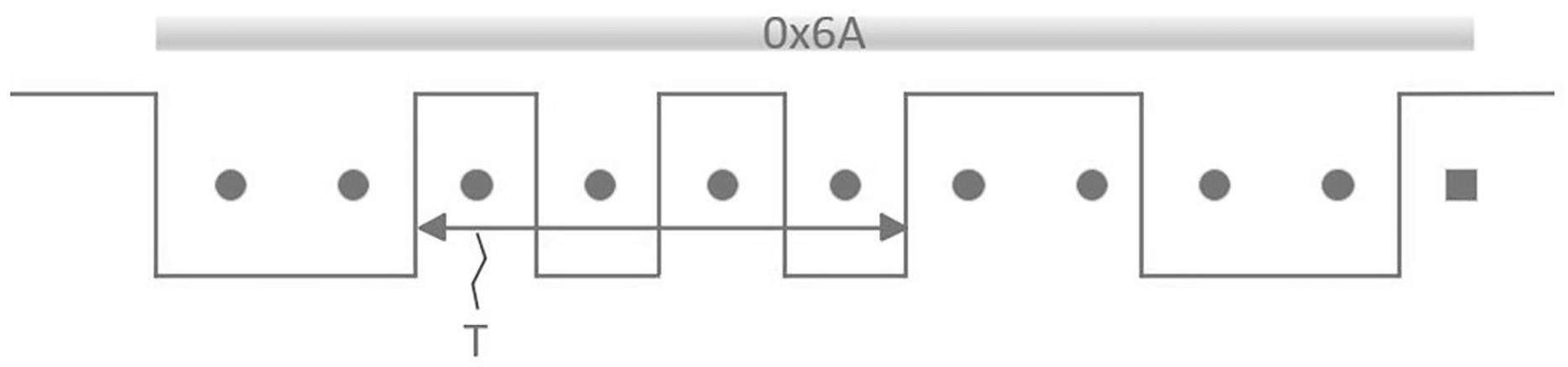

4、作为所述时钟校正方法的进一步改进:所述外设模块的txd引脚与mcu的定时器的捕获引脚相连接;mcu通过定时器根据接收固定数据时捕获到的指定的两个上升沿或下降沿之间的计时时差,得到内部rc的偏差值。

5、作为所述时钟校正方法的进一步改进:外设模块向mcu发送数据时,发送的数据的第一个字节为已知的固定数据。

6、作为所述时钟校正方法的进一步改进:设外设模块的波特率为bd,固定数据中指定的两个上升沿或下降沿之间间隔n个bit的时间,定时器捕获到的计时时差为t,则内部rc的偏差值为:offset=n/(bd*t)。

7、作为所述时钟校正方法的进一步改进:mcu得到内部rc的偏差值后,判断偏差值是否在预设的范围内:如果不在范围内且offset大于1,则降低内部rc的频率;如果不在范围内且offset小于1,则提高内部rc的频率。

8、作为所述时钟校正方法的进一步改进:所述mcu通过修改内部adj_reg寄存器的值来调整内部rc的频率,设adj_reg寄存器的当前值为old_adj,adj_reg寄存器的最低位对应的内部rc的频率的调校步长为lsb_adj,则将adj_reg寄存器的值设置为old_adj+(offset-1)/lsb_adj。

9、作为所述时钟校正方法的进一步改进,具体步骤为:

10、步骤1、将外设模块的txd引脚与mcu的定时器的捕获引脚相连接;

11、步骤2、开启mcu的外部晶体停振检测功能,检查外部晶体停振标志位;当mcu检测到外部晶体振荡器停振时,将mcu时钟切换到内部rc,然后执行步骤3;

12、步骤3、外设模块以异步通信方式向mcu发送数据,发送的数据的第一个字节为已知的固定数据;

13、步骤4、mcu通过定时器根据接收固定数据时捕获到的指定的两个上升沿或下降沿之间的计时时差,得到内部rc的偏差值;

14、步骤5、判断偏差值是否在预设的范围内:如果不在则调整内部rc的频率,然后返回步骤3,如果在预设范围内则等待一段时间后,返回步骤3。

15、作为所述时钟校正方法的进一步改进:步骤3至5中的任一步骤中,进一步判断外部晶体振荡器是否重新起振,如果重新起振,则停止当前步骤的执行,将外部晶体振荡器作为mcu的时钟源,并执行步骤2。

16、作为所述时钟校正方法的进一步改进:mcu与外设模块进行异步通信时,如果通信失败,则对mcu的波特率进行调整,直至通信正常。

17、本发明还提供了一种电能表,所述电能表包括mcu、外部晶体振荡器和计量芯片,所述mcu和外部晶体振荡器及计量芯片分别相连接,外部晶体振荡器作为mcu的时钟源,mcu通过计量芯片获取计量数据,当外部晶体振荡器停振时,mcu启动内部rc作为时钟源,然后采用上述时钟校正方法对内部rc进行校正,校正时,将计量芯片作为所述外设模块。

18、相对于现有技术,本发明具有以下积极效果:本发明在外部晶体振荡器停振后,以外设模块内部独立的时钟源作为基准,以异步通信时的数据为媒介,通过将数据传输时的高低电平变化特征的间隔时长与mcu内部定时器的计时时差相比较得到内部rc的偏差值,继而实现对内部rc的精准校正,不仅解决了内部rc无法校正的问题,而且具有占用资源少、校正效率高、无需额外能耗等优点。

技术特征:

1.一种基于异步通信的时钟校正方法,用于校正mcu内部rc的时钟误差,其特征在于:启用内部rc作为mcu的时钟源后,mcu接收外部模块通过异步通信方式发送的数据,所述外部模块内部带有独立的时钟源,所述mcu通过接收数据时高低电平变化特征之间的时长计算出内部rc的偏差值,然后基于该偏差值对内部rc进行校正。

2.如权利要求1所述的基于异步通信的时钟校正方法,其特征在于:所述外设模块的txd引脚与mcu的定时器的捕获引脚相连接;mcu通过定时器根据接收固定数据时捕获到的指定的两个上升沿或下降沿之间的计时时差,得到内部rc的偏差值。

3.如权利要求2所述的基于异步通信的时钟校正方法,其特征在于:外设模块向mcu发送数据时,发送的数据的第一个字节为已知的固定数据。

4.如权利要求3所述的基于异步通信的时钟校正方法,其特征在于:设外设模块的波特率为bd,固定数据中指定的两个上升沿或下降沿之间间隔n个bit的时间,定时器捕获到的计时时差为t,则内部rc的偏差值为:offset=n/(bd*t)。

5.如权利要求4所述的基于异步通信的时钟校正方法,其特征在于:mcu得到内部rc的偏差值后,判断偏差值是否在预设的范围内:如果不在范围内且offset大于1,则降低内部rc的频率;如果不在范围内且offset小于1,则提高内部rc的频率。

6.如权利要求5所述的基于异步通信的时钟校正方法,其特征在于:所述mcu通过修改内部adj_reg寄存器的值来调整内部rc的频率,设adj_reg寄存器的当前值为old_adj,adj_reg寄存器的最低位对应的内部rc的频率的调校步长为lsb_adj,则将adj_reg寄存器的值设置为old_adj+(offset-1)/lsb_adj。

7.如权利要求1所述的基于异步通信的时钟校正方法,其特征在于,具体步骤为:

8.如权利要求7所述的基于异步通信的时钟校正方法,其特征在于:步骤3至5中的任一步骤中,进一步判断外部晶体振荡器是否重新起振,如果重新起振,则停止当前步骤的执行,将外部晶体振荡器作为mcu的时钟源,并执行步骤2。

9.如权利要求1所述的基于异步通信的时钟校正方法,其特征在于:mcu与外设模块进行异步通信时,如果通信失败,则对mcu的波特率进行调整,直至通信正常。

10.一种电能表,所述电能表包括mcu、外部晶体振荡器和计量芯片,所述mcu和外部晶体振荡器及计量芯片分别相连接,外部晶体振荡器作为mcu的时钟源,mcu通过计量芯片获取计量数据,其特征在于:当外部晶体振荡器停振时,mcu启动内部rc作为时钟源,然后采用如权利要求1至9任一所述的时钟校正方法对内部rc进行校正,校正时,将计量芯片作为所述外设模块。

技术总结

本发明公开了一种基于异步通信的时钟校正方法及电能表。所述校正方法用于校正MCU内部RC的时钟误差,在启用内部RC作为MCU的时钟源后,MCU接收外部模块通过异步通信方式发送的数据,所述外部模块内部带有独立的时钟源,所述MCU通过接收数据时高低电平变化特征之间的时长计算出内部RC的偏差值,然后基于该偏差值对内部RC进行校正。本发明不仅解决了内部RC无法校正的问题,而且具有占用资源少、校正效率高、无需额外能耗等优点。

技术研发人员:尹西科,姜文浩,许芹,贺岩,贾斌,马金臣,秦宗亚,李海岩,刘军蕾

受保护的技术使用者:烟台东方威思顿电气有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!