环形振荡器结构TDC的校正方法及系统与流程

本发明属于时间数字转换,尤其涉及时间数字转换器的校正。

背景技术:

1、时间数字转换器(time-to-digital converter,tdc)是一种将时间量转化为数字量的器件,主要用于高精度时间测量,在许多领域都有广泛应用。其中,环形振荡器结构tdc应用较为广泛,其基本结构如图2所示,主要由环形振荡器、环振计数器和采样电路组成。环形振荡器由奇数个首尾相连的反相器组成,具有一定的振荡周期,而环振计数器对环振周期进行计数,得到粗略测量时间(粗计数值),同时扩大tdc的量程。采样电路在start和stop信号到来时分别对环振中每个反相器的输出进行采样,根据采样结果得到细计数值。其中,采样结果应为大部分0、1相间,有且只有两个0或者两个1相连。

2、设rst和rsp分别表示start和stop触发采样的延迟单元状态对应的细计数值,cnt为该时间间隔下的粗计数值,τ为基本延迟单元的延迟,t为环形振荡器周期,ε则是测量误差,那么待测时间间隔δt满足以下公式:

3、δt=cnt×t+(rst-rsp)×τ+ε。

4、采样电路在对输出正在变化的延迟单元进行采样时,例如在上升沿或者下降沿处,可能会出现错误,例如正确输出为10…10010,但是从低位向高位数第二个延迟单元采样出现错误,输出变成了10…10000,导致进行译码后造成rst和rsp错误,测得的δt不准确。

技术实现思路

1、本发明是为了解决现有环形振荡器结构tdc的采样电路在对输出正在变化的延迟单元进行采样时可能会出现错误,导致待测时间间隔不准确的问题,现提供环形振荡器结构tdc的校正方法及系统。

2、本发明提供两种校正方法以及两种校正系统方案:

3、第一种环形振荡器结构tdc的校正方法,包括以下步骤:

4、步骤一:将环振实际状态信号ring与环振初始状态信号ring_original逐位进行异或运算,获得状态对比结果ring_temp;

5、步骤二:对状态对比结果ring_temp中相邻的两位进行异或运算,获得临位对比结果,对状态对比结果ring_temp中最高位和最低位进行同或运算,获得首尾对比结果,并将首尾对比结果作为最低位与临位对比结果拼凑成flag信号;

6、步骤三:将flag信号的最高位移动至最低位,并将剩余位向高位移动一位,获得第一移位结果,对第一移位结果的每一位取反,并将取反之后的结果与flag信号进行与运算,获得flag_edge信号;

7、步骤四:将flag_edge信号中从低到高位第一个为1的位数记为num;

8、步骤五:根据校正规则遍历环振实际状态信号ring的每一位信号值,获得环形振荡器结构tdc的校正结果ring_check;

9、所述校正规则为:

10、当k>num时,若ring_temp[k]≠ring_temp[num],则ring[k]取反,否则ring[k]不变,

11、当k<num时,若ring_temp[k]=ring_temp[num],则ring[k]取反,否则ring[k]不变,

12、当k=num时,ring[k]不变,

13、ring_temp[k]和ring_temp[num]分别表示状态对比结果ring_temp中的第k位和第num位信号值,ring[k]表示环振实际状态信号ring中的第k位信号值。

14、进一步的,上述环形振荡器结构tdc包括环形振荡器、环振计数器和采样电路;

15、所述环形振荡器包括n个首尾相连的反相器,n为大于1的奇数;

16、所述环振计数器用于对环振周期进行计数;

17、所述采样电路用于在start和stop信号到来时对环形振荡器中每个反相器的输出以及环振计数器的输出进行采样。

18、进一步的,上述环振实际状态信号ring为采样电路在start和stop信号到来时采集的环形振荡器输出信号。

19、第二种环形振荡器结构tdc的校正方法,包括以下步骤:

20、步骤一:将采样电路在start和stop信号到来时采集的环振实际状态信号ring与环振初始状态信号ring_original逐位进行异或运算,获得状态对比结果ring_temp;

21、步骤二:对状态对比结果ring_temp中相邻的两位进行同或运算,获得临位对比结果,对状态对比结果ring_temp中最高位和最低位进行异或运算,获得首尾对比结果,并将首尾对比结果作为最高位与临位对比结果拼凑成flag信号;

22、步骤三:将flag信号的最高位移动至最低位,并将剩余位向高位移动一位,获得第一移位结果,将flag信号最高的两位移动至最低两位,并将剩余位向高位移动两位,获得第二移位结果,将所述第一移位结果与所述第二移位结果逐位进行与运算,获得flag_edge信号;

23、步骤四:将flag_edge信号中从低到高位第一个为1的位数记为num;

24、步骤五:根据校正规则遍历环振实际状态信号ring的每一位,获得环形振荡器结构tdc的校正结果ring_check;

25、所述校正规则为:

26、当k>num时,若ring_temp[k]≠ring_temp[num],则ring[k]取反,否则ring[k]不变,

27、当k<num时,若ring_temp[k]=ring_temp[num],则ring[k]取反,否则ring[k]不变,

28、当k=num时,ring[k]不变,

29、ring_temp[k]和ring_temp[num]分别表示状态对比结果ring_temp中的第k位和第num位信号值,ring[k]表示环振实际状态信号ring中的第k位信号值。

30、进一步的,上述环形振荡器结构tdc包括环形振荡器、环振计数器和采样电路;

31、所述环形振荡器包括n个首尾相连的反相器,n为大于1的奇数;

32、所述环振计数器用于对环振周期进行计数;

33、所述采样电路用于在start和stop信号到来时对环形振荡器中每个反相器的输出以及环振计数器的输出进行采样。

34、进一步的,上述环振实际状态信号ring为采样电路在start和stop信号到来时采集的环形振荡器输出信号。

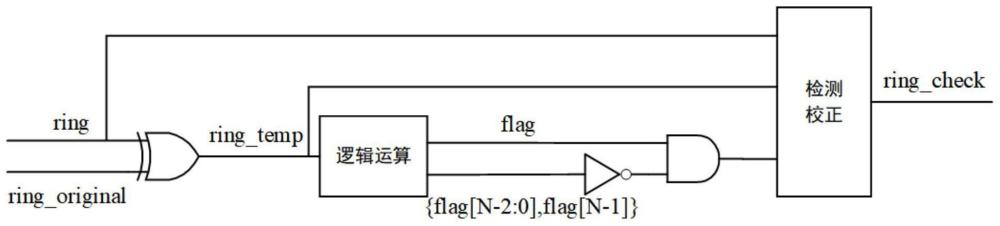

35、第一种环形振荡器结构tdc的校正系统,包括以下单元:

36、状态比较单元:用于将环振实际状态信号ring与环振初始状态信号ring_original逐位进行异或运算,获得状态对比结果ring_temp;对状态对比结果ring_temp中相邻的两位进行异或运算,获得临位对比结果,对状态对比结果ring_temp中最高位和最低位进行同或运算,获得首尾对比结果,并将首尾对比结果作为最低位与临位对比结果拼凑成flag信号;

37、边沿检测单元:用于将flag信号的最高位移动至最低位,并将剩余位向高位移动一位,获得第一移位结果,对第一移位结果的每一位取反,并将取反之后的结果与flag信号进行与运算,获得flag_edge信号;

38、误码校正单元:用于将flag_edge信号中从低到高位第一个为1的位数记为num,根据校正规则遍历环振实际状态信号ring的每一位信号值,获得环形振荡器结构tdc的校正结果ring_check;

39、所述校正规则为:

40、当k>num时,若ring_temp[k]≠ring_temp[num],则ring[k]取反,否则ring[k]不变,

41、当k<num时,若ring_temp[k]=ring_temp[num],则ring[k]取反,否则ring[k]不变,

42、当k=num时,ring[k]不变,

43、ring_temp[k]和ring_temp[num]分别表示状态对比结果ring_temp中的第k位和第num位信号值,ring[k]表示环振实际状态信号ring中的第k位信号值。

44、进一步的,上述环形振荡器结构tdc包括环形振荡器、环振计数器和采样电路;

45、所述环形振荡器包括n个首尾相连的反相器,n为大于1的奇数;

46、所述环振计数器用于对环振周期进行计数;

47、所述采样电路用于在start和stop信号到来时对环形振荡器中每个反相器的输出以及环振计数器的输出进行采样。

48、进一步的,上述环振实际状态信号ring为采样电路在start和stop信号到来时采集的环形振荡器输出信号。

49、第二种环形振荡器结构tdc的校正系统,包括以下单元:

50、状态比较单元:用于将采样电路在start和stop信号到来时采集的环振实际状态信号ring与环振初始状态信号ring_original逐位进行异或运算,获得状态对比结果ring_temp,对状态对比结果ring_temp中相邻的两位进行同或运算,获得临位对比结果,对状态对比结果ring_temp中最高位和最低位进行异或运算,获得首尾对比结果,并将首尾对比结果作为最高位与临位对比结果拼凑成flag信号;

51、边沿检测单元:用于将flag信号的最高位移动至最低位,并将剩余位向高位移动一位,获得第一移位结果,将flag信号最高的两位移动至最低两位,并将剩余位向高位移动两位,获得第二移位结果,将所述第一移位结果与所述第二移位结果逐位进行与运算,获得flag_edge信号;

52、误码校正单元:用于将flag_edge信号中从低到高位第一个为1的位数记为num,根据校正规则遍历环振实际状态信号ring的每一位,获得环形振荡器结构tdc的校正结果ring_check;

53、所述校正规则为:

54、当k>num时,若ring_temp[k]≠ring_temp[num],则ring[k]取反,否则ring[k]不变,

55、当k<num时,若ring_temp[k]=ring_temp[num],则ring[k]取反,否则ring[k]不变,

56、当k=num时,ring[k]不变,

57、ring_temp[k]和ring_temp[num]分别表示状态对比结果ring_temp中的第k位和第num位信号值,ring[k]表示环振实际状态信号ring中的第k位信号值。

58、进一步的,上述环形振荡器结构tdc包括环形振荡器、环振计数器和采样电路;

59、所述环形振荡器包括n个首尾相连的反相器,n为大于1的奇数;

60、所述环振计数器用于对环振周期进行计数;

61、所述采样电路用于在start和stop信号到来时对环形振荡器中每个反相器的输出以及环振计数器的输出进行采样。

62、进一步的,上述环振实际状态信号ring为采样电路在start和stop信号到来时采集的环形振荡器输出信号。

63、本发明提出了针对环形振荡器结构tdc的校正方法及系统,通过查找环形振荡器单元状态变化的边界即信号传递到的位置并通过逻辑判断对采样到的环振状态进行校正,能够消除对信号传递边沿附近的延迟单元采样造成的误差。

- 还没有人留言评论。精彩留言会获得点赞!