一种基于上下拉网络的双轨抗功耗攻击门电路设计方法

1.本发明属于电子电路领域,具体为一种抗功耗攻击的双轨门电路设计。

背景技术:

2.功耗分析攻击是威胁硬件安全的一种强有力的攻击手段,其利用硬件电路工作过程中必然产生的功耗与其所处理数据的相关性建立信息泄露模型,通过对示波器所采样的能量曲线进行统计学分析,从而提取出数字电路存储或计算的重要信息,如提取智能卡的密钥、破解密码芯片的s盒运算等。

3.基于paa的改进攻击方法层出不穷。因此,对paa的预防措施已成为工业界和学术界研究的重要方向。功耗攻击防护措施可以分为算法级、系统级和电路级三个方面,其中电路级防护措施旨在从底层逻辑电路上根本性地消除由功耗变化所带来的信息泄露。电路级抗paa方案一般是设计出功耗恒定的逻辑电路,已有学者研究出利用联合的门电路实现逻辑电路的功耗平衡,同时提出新型的门电路设计,但考虑到提前传播效应的影响以及优化芯片面积,更多的基于双轨预充电的门电路设计方案被提出。

技术实现要素:

4.为实现功耗平衡并优化芯片面积,本发明提供一种基于上下拉网络的双轨抗功耗攻击门电路设计方法,实现功耗恒定的同时具有晶体管数量少、能耗低的优点。本发明所采用的技术方案如下:所述的一种基于上下拉网络的双轨抗功耗攻击门电路设计方法,其特征在于:首先由基于上下拉网络的单轨“与门”和单轨“与非门”组成双轨“与门”;然后将时钟周期分为预充电阶段和求值阶段实现功耗恒定;所述预充电阶段采用行波流水预充电方法。

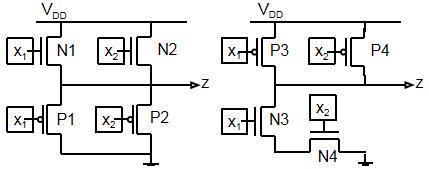

5.进一步的,所述的一种基于上下拉网络的双轨抗功耗攻击门电路设计方法,其特征在于:所述单轨“与门”为nmos管n1与n2并联,一端接电源vdd,另一端接输出端;pmos管p1与p2并联,一端接输出端,另一端接地,输入端x1接n1和p1的栅极;x2接n2与p2的栅极;单轨“与非门”为pmos管p3与p4并联,一端接电源vdd,另一端接输出端;nmos管n3与n4串联,一端接输出端,另一端接地;输入端x1接p3和n3的栅极;x2接p4与n4的栅极。

6.进一步的,所述的一种基于上下拉网络的双轨抗功耗攻击门电路设计方法,其特征在于:所述双轨“与门”具体为:nmos管n5与n8并联,一端接电源vdd,另一端接输出端ab;nmos管n9与n12并联,一端接输出端ab,另一端接地;nmos管n6与n7并联,一端接电源vdd,另一端接输出端 ;nmos管n10与n11串联,一端接输出端 ,另一端接地。

7.进一步的,所述的一种基于上下拉网络的双轨抗功耗攻击门电路设计方法,其特征在于:单个时钟周期的前半周期为预充电阶段,采用所述行波流水预充电方法,该阶段输入信号为全“0”,输出信号为全“0”,通过这样的逐级传递实现整个电路统一的预充电;时钟的后半周期为求值阶段,执行正常的逻辑运算,在该阶段输入信号为两对差分信号,输出信

号为一对差分信号,用双轨(0,1)代替传统的逻辑“0”,(1,0)代替传统的逻辑“1”。

8.与现有技术相比,本发明有以下优点:本发明实现了在每个时钟周期门电路的输出端在任何情况下只有一个“0

”‑“

1”信号的跳变,实现了电路功耗的恒定;同时具有晶体管数量少、单个双轨“与门”仅需8个晶体管,电路成本较低且功耗低的优点。

附图说明

9.图1是基于上下拉网络的单轨“与门”和“与非门”原理图;图2是本发明的双轨“与门”原理图;图3是行波流水预充电原理图。

具体实施方式

10.在本发明的描述中,需要理解的是,术语“一端”、

ꢀ“

另一端”、

ꢀ“

外侧”、

ꢀ“

上”、

ꢀ“

内侧”、

ꢀ“

水平”、

ꢀ“

同轴”、

ꢀ“

中央”、

ꢀ“

端部”、

ꢀ“

长度”、

ꢀ“

外端”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

11.下面结合附图对本发明作进一步说明。

12.一种基于上下拉网络的双轨抗功耗攻击门电路设计方法,包括以下步骤:首先由基于上下拉网络的单轨“与门”和单轨“与非门”组成双轨“与门”;然后将时钟周期分为预充电阶段和求值阶段实现功耗恒定;所述预充电阶段采用行波流水预充电方法。

13.如图1(左)所示,单轨“与门”:nmos管n1与n2并联,一端接电源vdd,另一端接输出端;pmos管p1与p2并联,一端接输出端,另一端接地。输入端x1接n1和p1的栅极;x2接n2与p2的栅极。

14.如图1(右)所示,单轨“与非门”:pmos管p3与p4并联,一端接电源vdd,另一端接输出端;nmos管n3与n4串联,一端接输出端,另一端接地。输入端x1接p3和n3的栅极;x2接p4与n4的栅极。

15.如图2所示,双轨“与门”具体为:nmos管n5与n8并联,一端接电源vdd,另一端接输出端ab;nmos管n9与n12并联,一端接输出端ab,另一端接地;nmos管n6与n7并联,一端接电源vdd,另一端接输出端;nmos管n10与n11串联,一端接输出端,另一端接地。输入端a接晶体管n5和n10的栅极,接n6和n9的栅极,b接n8和n11的栅极,接n7和n12的栅极。

16.进一步的,所述行波流水预充电实现功耗恒定具体为:单个时钟周期的前半周期为预充电阶段,采用行波流水预充电方法,该方法参考自加州理工大学克里斯等人在实现抗功耗攻击电路时提出的波动态差分逻辑。在预充电阶段,输入信号为全“0”,输出信号为全“0”,如图3所示,通过这样的逐级传递实现整个电路统一的预充电;时钟的后半周期为求值阶段,执行正常的逻辑运算,在该阶段输入信号为两对差分信号,输出信号为一对差分信号,用双轨(0,1)代替传统的逻辑“0”,(1,0)代替传统的逻辑“1”。

17.本发明采用的双轨上下拉网络实现了在每个时钟周期门电路的输出端在任何情

况下只有一个“0

”‑“

1”信号的跳变,实现了电路功耗的恒定;同时具有晶体管数量少、功耗低的优点。本电路的标准化能量偏差指数为8.24%。

18.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

技术特征:

1.一种基于上下拉网络的双轨抗功耗攻击门电路设计方法,其特征在于:首先由基于上下拉网络的单轨“与门”和单轨“与非门”组成双轨“与门”;然后将时钟周期分为预充电阶段和求值阶段实现功耗恒定;所述预充电阶段采用行波流水预充电方法。2.根据权利要求1所述的一种基于上下拉网络的双轨抗功耗攻击门电路设计方法,其特征在于:所述单轨“与门”为nmos管n1与n2并联,一端接电源vdd,另一端接输出端;pmos管p1与p2并联,一端接输出端,另一端接地,输入端x1接n1和p1的栅极;x2接n2与p2的栅极;单轨“与非门”为pmos管p3与p4并联,一端接电源vdd,另一端接输出端;nmos管n3与n4串联,一端接输出端,另一端接地;输入端x1接p3和n3的栅极;x2接p4与n4的栅极。3.根据权利要求1所述的一种基于上下拉网络的双轨抗功耗攻击门电路设计方法,其特征在于:所述双轨“与门”具体为:nmos管n5与n8并联,一端接电源vdd,另一端接输出端ab;nmos管n9与n12并联,一端接输出端ab,另一端接地;nmos管n6与n7并联,一端接电源vdd,另一端接输出端;nmos管n10与n11串联,一端接输出端,另一端接地。4.根据权利要求1所述的一种基于上下拉网络的双轨抗功耗攻击门电路设计方法,其特征在于:单个时钟周期的前半周期为预充电阶段,采用行波流水预充电方法,该方法参考自加州理工大学克里斯等人在实现抗功耗攻击电路时提出的波动态差分逻辑;在预充电阶段,输入信号为全“0”,输出信号为全“0”,通过这样的逐级传递实现整个电路统一的预充电;时钟的后半周期为求值阶段,执行正常的逻辑运算,在该阶段输入信号为两对差分信号,输出信号为一对差分信号,用双轨(0,1)代替传统的逻辑“0”,(1,0)代替传统的逻辑“1”。

技术总结

本发明提供一种基于上下拉网络的双轨抗功耗攻击门电路设计方法。本方案采用双轨预充电逻辑,结合两个基于上下拉网络的单轨“与门”和“与非门”实现双轨“与门”,用双轨信号代替传统的单轨信号。本设计的单轨门电路仅使用4个晶体管,在单个时钟周期中使用行波流水预充电方法实现功耗平恒。实现了在每个时钟周期门电路的输出端在任何情况下只有一个“0

技术研发人员:姚茂群 薛紫微

受保护的技术使用者:杭州师范大学

技术研发日:2021.08.10

技术公布日:2021/12/17

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1