一种应用于400GPAM4CDR的时钟相位编程技术的制作方法

本发明涉及光电集成电路设计,具体为一种应用于400g pam4cdr的时钟相位编程技术。

背景技术:

1、光通讯技术是一种高效的信号传输技术,是目前高速信号传输的主要技术;随着信息技术的发展,对数据传输速率要求也越来越高,特别是大数据,区块链,云计算,物联网,人工智能和5g的兴起,数据流量迅猛增长,对光通讯技术也提出了更高的要求;目前使用的nrz模式的数据率受限于现有集成电路工艺,传输数据速率很难有大的提高,而pam4技术是一种更高效的调制技术,能够很好的在现有工艺水平上,解决数据速率提高问题;pam4技术不同于nrz技术,它的每个ui可以表示2个数据信息,而nrz技术,每个ui仅可表示1个数据信息,因此,pam4技术可直接将速率翻倍。

2、目前市场上已经有的高速pam4技术的产品,大都使用dsp对接收的pam4信号进行处理,但方法需要一个大的dsp芯片对接收数据进行处理,导致芯片结构复杂,规模大,功耗大;为了解决这个问题,大家开始直接使用cdr直接处理pam4信号;接收的pam4信号由于受到pcb衰减的影响,信号信噪比严重下降,会降低cdr锁定能力,干扰cdr的采样点,导致接收到的pam4信号出现错误的信息,所以在cdr工作时,会采用监测cdr锁定和采样点位置的技术;为了实现采样点在输入数据中间,需要通过编程cdr的vco输出采样时钟的相位,来采集输入数据,然后根据连续采集的大量数据,来判断目前的采样点是否在数据的正中间。

3、目前的时钟相位编程技术,主要采用pi技术,该技术使用两个不同相位的时钟,拟合输出一个新的时钟;新时钟的相位受两个时钟权值来控制,通过编程两个时钟的权值,即可实现相位编程;但是该技术存在一个缺点是要求输入有两个时钟相位,且两个时钟相位差不能大于90度;高速集成电路的时钟都是有lc-vco产生,lc-vco很难产生两个相位差在90度或者90度以内的时钟;业界一般是通过复杂的电路,将lc-vco产生的时钟转换成相位差90度的时钟,比如2分频分频器,从而导致电路结构复杂,功耗大,难度系数增加。

技术实现思路

1、(一)解决的技术问题

2、针对现有技术的不足,本发明提供了一种应用于400g pam4 cdr的时钟相位编程技术,解决了从而导致电路结构复杂,功耗大,难度系数增加的问题。

3、(二)技术方案

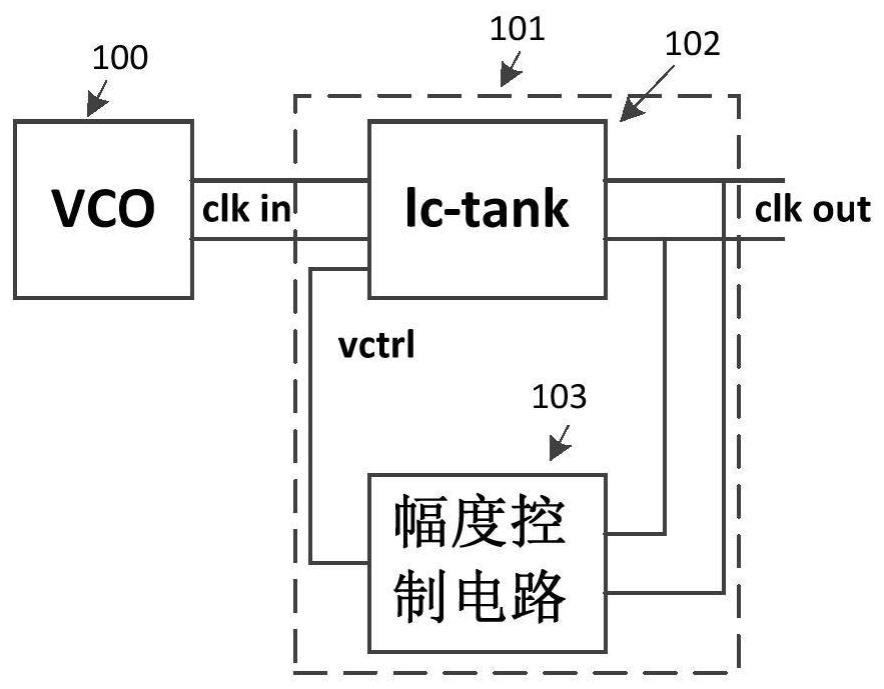

4、本发明提供了一种应用于400g pam4 cdr的时钟相位编程技术,所述相位编程技术包括lc-tank电路和幅度控制电路;lc-tank电路包括电感,可编程电容,差分输入对管和尾电流管;幅度控制电路包括幅度监测电路,幅度阈值设置电路,幅度比较器和限幅器;lc-tank电路用于产生与输入端同频的各种相位的时钟,幅度控制电路用于控制lc-tank电路的输出信号的幅度,确保在不同相位下,lc-tank电路的输出幅度都相同,以降低下一级电路的实现复杂度。

5、所述lc-tank电路,其相位编程采用电感与电容组成的谐振器,谐振器能够在高频处产生较大的有效负载,非常适合在超高速集成电路中使用。

6、所述lc-tank电路,其可编程电容的容值编程由查找表控制电容容值,电容容值是非线性且是单调的,在lc-tank电路谐振器的谐振频率靠近输入时钟频率时,每个code变化产生的电容变化小,而谐振器谐振频率远离输入时钟频率时,每个code变化产生的电容变化大;从而确保相位编程器输出相位的线性度。

7、所述幅度控制电路,确保了在时钟相位编程时,时钟输出幅度恒定;幅度控制电路为低带宽运算放大器,以保证幅度控制环路的稳定性和对系统高频噪声的抑制。

8、所述幅度控制电路,其幅度阈值设置具有可编程功能,可根据相位编程器下一级电路的特点,设置合适的输出幅度。

9、所述幅度控制电路,其输出端口采用限幅器,以确保在芯片启动或者相位编程器在无输入时钟时,lc-tank电路的工作电流不会过高而导致器件性能下降或者快速老化问题。

10、(三)有益效果

11、本发明所提出的技术,可以直接使用lc-vco输出时钟,并对时钟相位进行编程;该技术所需要的电路结构简单,功耗低,并且能够降低高频时钟相位编程技术对工艺的要求,非常适合在超高速集成电路中使用。

技术特征:

1.一种应用于400g pam4的cdr的时钟相位编程技术,其特征在于:包括lc-tank电路,幅度控制电路;lc-tank电路包括电感,可编程电容,差分输入对管和尾电流管;幅度控制电路包括幅度监测电路,幅度阈值设置电路,幅度比较器和限幅器;lc-tank电路用于产生与输入端同频的各种相位的时钟,幅度控制电路用于控制lc-tank电路的输出信号的幅度,确保在不同相位下,lc-tank电路的输出幅度都相同,以降低下一级电路的实现复杂度。

2.根据权利要求1所述的应用于400g pam4的cdr的时钟相位编程技术,其特征在于:相位编程采用电感与电容组成的谐振器,谐振器能够在高频处产生较大的有效负载,非常适合在超高速集成电路中使用。

3.根据权利要求1所述的应用于400g pam4的cdr的时钟相位编程技术,其特征在于:lc-tank电路的可编程电容的容值编程由查找表控制电容容值,电容容值是非线性且是单调的,在lc-tank电路谐振器的谐振频率靠近输入时钟频率时,每个code变化产生的电容变化小,而谐振器谐振频率远离输入时钟频率时,每个code变化产生的电容变化大;从而确保相位编程器输出相位的线性度。

4.根据权利要求1所述的应用于400g pam4的cdr的时钟相位编程技术,其特征在于:幅度控制电路,确保在时钟相位编程时,时钟输出幅度恒定;幅度控制电路为低带宽运算放大器,以保证幅度控制环路的稳定性和对系统高频噪声的抑制。

5.根据权利要求1所述的应用于400g pam4的cdr的时钟相位编程技术,其特征在于:幅度控制电路具有幅度阈值设置可编程功能,可根据相位编程器下一级电路的特点,设置合适的输出幅度。

6.根据权利要求1所述的应用于400g pam4的cdr的时钟相位编程技术,其特征在于:幅度控制电路输出端口采用限幅器,以确保在芯片启动或者相位编程器在无输入时钟时,lc-tank电路的工作电流不会过高而导致器件性能下降或者快速老化问题。

技术总结

本发明提供了一种应用于400G PAM4CDR的时钟相位编程技术,所述相位编程技术包括lc‑tank电路和幅度控制电路;lc‑tank电路包括电感,可编程电容,差分输入对管和尾电流管;幅度控制电路包括幅度监测电路,幅度阈值设置电路,幅度比较器和限幅器;lc‑tank电路用于产生与输入端同频的各种相位的时钟,幅度控制电路用于控制lc‑tank电路的输出信号的幅度,确保在不同相位下,lc‑tank电路的输出幅度都相同;本发明所提出的400G PAM4CDR时钟相位编程技术相比业界广泛采用的PI技术,仅需要一个时钟信号,可以直接使用lc‑vco输出时钟,降低了对lc‑vco的要求;该技术所需要的电路结构简单,功耗低,并能够降低高频时钟相位编程技术对工艺的要求,非常适合在超高速集成电路中使用。

技术研发人员:黄召军,王祚栋,毛蔚,白昀

受保护的技术使用者:飞昂通讯科技南通有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!