一种HOMEBUS总线信号串行接收方法及装置与流程

本发明属于总线通信信号处理,具体地说,是涉及一种homebus总线信号串行接收方法及装置。

背景技术:

1、homebus全称是日本家庭总线, 为两线载波通讯总线,它的优势有以下几点:(1)能实现两线无极通讯,工程安装方便;(2)总线可带载,总线能实现8-40v供电;在小型设施无法保证供电到设备端的情况下,可通过传输线供电;(3)抗噪声性能好,适于远距离通信;(4)指令对传输线的干扰影响小;转换芯片连接了耦合电容,提高了交流通信能力,抗干扰性好。

2、现有homebus串行接收技术及设备一般都是针对单一品牌信号。由于每个厂家生产的homebus总线设备都存在软件和硬件上的差异,兼容性较差,给应用及维保造成困难,限制了homebus的发展。

技术实现思路

1、本发明提供一种homebus总线信号串行接收方法及装置。使不同厂家及不同规格的总线信号可以准确及可靠接收,电路成本低,效率高,降低homebus的应用及维保难度。

2、为解决上述技术问题,本发明采用以下技术方案予以实现:

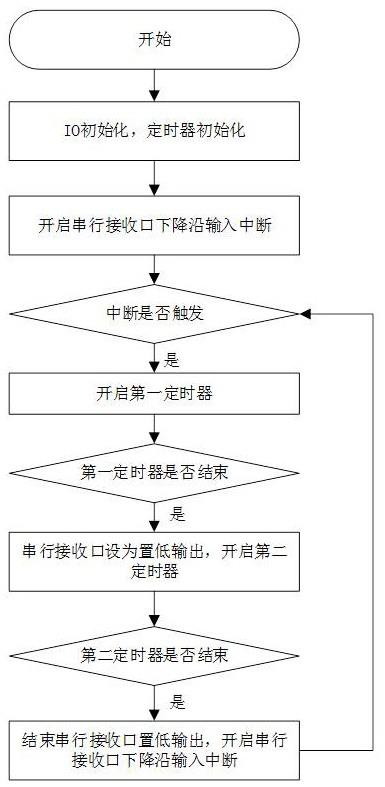

3、一种homebus总线信号串行接收方法,包括:

4、设置第一定时器、第二定时器,其定时时间均不大于且趋于等于一位串行信号时长的一半;

5、设置串行接收口同时为下降沿输入中断;

6、当所述串行接收口被下降沿触发时,启动所述第一定时器;

7、在所述第一定时器定时完成时,设置所述串行接收口置低输出,并启动所述第二定时器;

8、在所述第二定时器定时完成时,结束所述串行接收口置低输出并重新设置为下降沿输入中断。

9、在一实施例中,homebus总线信号串行接收方法还包括:

10、设置第三定时器,其定时时间等于所述第一定时器的定时时间;

11、在所述第二定时器定时完成时,启动所述第三定时器;

12、在所述第三定时器定时完成时,判断所述串行接收口的输入的电平是否为低;

13、当所述串行接收口的输入的电平为低时,设置所述串行接收口置低输出并开启所述第二定时器;

14、当所述第二定时器定时完成时,结束所述串行接收口置低输出,并重新设置为下降沿输入中断。

15、在一实施例中,homebus总线信号串行接收方法还包括:

16、配置所述第一定时器、所述第二定时器、所述第三定时器共用为定时器。

17、在一实施例中,homebus总线信号串行接收方法还包括:

18、设置所述定时器为自动重装定时器。

19、在一实施例中,homebus总线信号串行接收方法还包括:

20、设置所述串行接收口为uart接收口;一位所述串行信号的时长为波特率的倒数。

21、在一实施例中,homebus总线信号串行接收方法还包括:

22、所述波特率配置为9600bps或10000bps;

23、所述定时时间为50us。

24、一种homebus总线信号串行接收装置包括控制器、信号接收电路;

25、所述控制器包括串行通信模块,配置有homebus总线信号串行接收方法;所述串行通信模块包括串行接收口;

26、所述信号接收电路包括信号转换电路、信号处理电路;所述信号转换电路与总线连接,用于接收载波信号并输出数字信号;所述信号处理电路与所述信号转换电路连接,用于接收所述数字信号进行处理后输出总线信号;所述串行接收口与所述信号处理电路连接,用于接收所述总线信号。

27、在一实施例中,所述信号处理电路包括第一电阻、第二电阻、滤波电容;所述第一电阻与所述滤波电容并联形成并联电路;所述并联电路的一端与所述第二电阻的一端连接,另一端接地;所述第二电阻的另一端与所述信号转换电路连接。

28、在一实施例中,所述信号处理电路还包括二极管,其与所述第二电阻、所述并联电路串联。

29、在一实施例中,所述信号转换电路包括mm1192芯片。

30、与现有技术相比,本发明的优点和积极效果是:根据总线信号的编码方式,需将逻辑低的总线信号后半位时长的高电平转换为低电平用于接收为串行信号。本发明的homebus总线信号串行接收方法及homebus总线信号串行接收装置利用串行接收口的同时多功能性,设置串行接收口同时为下降沿输入中断,捕获逻辑低的总线信号的开始时序;设置第一定时器定时至总线信号的前半位结束时刻或即将结束时刻,设定串行接收口同时为置低输出,使串行接收口的低电平输出直接被串行接收口接收。即,串行接收口的低电平输出拉低总线信号的后半位的电平供串行接收口采样,不仅转换逻辑低的总线信号后半位时长或接近后半位时长的高电平为低电平,补足串行信号的低电平,使其低电平时长接近一位时长,保证逻辑低的串行信号的接收;且去除总线信号后半位时长期间周围电路造成的尖刺干扰及其他干扰,使串行接收口接收的逻辑低的总线信号始终为低,提高串行接收口接收串行信号的准确性及可靠性。

技术特征:

1.一种homebus总线信号串行接收方法,其特征在于,包括:

2.根据权利要求1所述的homebus总线信号串行接收方法,其特征在于,还包括:

3.根据权利要求2所述的homebus总线信号串行接收方法,其特征在于,配置所述第一定时器、所述第二定时器、所述第三定时器共用为定时器。

4.根据权利要求3所述的homebus总线信号串行接收方法,其特征在于,设置所述定时器为自动重装定时器。

5.根据权利要求1至4任一项所述的homebus总线信号串行接收方法,其特征在于,所述串行接收口为uart接收口;一位所述串行信号的时长为波特率的倒数。

6.根据权利要求5所述的homebus总线信号串行接收方法,其特征在于, 所述波特率配置为9600bps或10000bps;

7.一种homebus总线信号串行接收装置,其特征在于, 包括:

8.根据权利要求7所述的homebus总线信号串行接收装置,其特征在于,所述信号处理电路包括第一电阻、第二电阻、滤波电容;所述第一电阻与所述滤波电容并联形成并联电路;所述并联电路的一端与所述第二电阻的一端连接,另一端接地;所述第二电阻的另一端与所述信号转换电路连接。

9.根据权利要求8所述的homebus总线信号串行接收装置,其特征在于,所述信号处理电路还包括二极管,其与所述第二电阻、所述并联电路串联。

10.根据权利要求7至9任一项所述的homebus总线信号串行接收装置,其特征在于,所述信号转换电路包括mm1192芯片。

技术总结

本发明公开一种HOMEBUS总线信号串行接收方法及装置;串行接收方法包括设置第一定时器、第二定时器,其定时时间均不大于且趋于等于一位串行信号时长的一半;设置串行接收口为下降沿输入中断;当所述串行接收口下降沿输入中断触发时启动所述第一定时器;在所述第一定时器定时完成时,将所述串行接收口置低输出,并启动所述第二定时器;在所述第二定时器定时完成时,结束所述串行接收口置低输出并重新设置为下降沿输入中断。串行接收装置包括控制器、信号接收电路;控制器包括串行通信模块,配置有串行接收方法;所述串行通信模块包括串行接收口,其与所述信号接收电路连接。本发明提高串行接收HOMEBUS总线信号的准确性及可靠性。

技术研发人员:董志强,丁在泉

受保护的技术使用者:青岛中弘数字技术有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!