一种大规模量子芯片谐振腔的设计方法及量子处理器与流程

本发明属于量子芯片制造,特别涉及一种大规模量子芯片谐振腔的设计方法及量子处理器。

背景技术:

1、随着量子计算技术的普及,实施量子计算的量子芯片成为了科研的重点对象。量子芯片相比于传统的集成芯片,具有强大的并行计算能力,且并行计算能力随着量子芯片的位数(量子比特位数)呈指数式提升。

2、量子芯片上集成有多个一一对应且相互耦合的量子比特和谐振腔,谐振腔和量子比特耦合的系统形成了线路腔量子电动力学体系,可以作为量子计算的基本元件。其中,谐振腔可以作为量子比特的读出电路,反映量子比特的状态,作为设计量子芯片的重要一环,读出电路设计的好坏将直接影响整个量子芯片的工作性能,例如,当量子芯片上谐振腔的工作频率出现偏差导致两个及以上谐振腔的工作频率间隔过小时,会对对应量子比特的读取产生干扰,降低对应量子比特的读取保真度,影响量子芯片的工作性能,因此,谐振腔的设计显得尤为重要。

3、但是,现有技术中在对量子芯片进行设计时,要对其上的每个谐振腔的参数一一进行设计、修正、仿真测试,需要花费很长时间,对于具有多个量子比特的大规模量子芯片谐振腔的设计需要耗费大量时间、花费巨大设计成本且设计效率低。因此,如何减少大规模量子芯片谐振腔的设计耗时,提高设计效率及降低设计成本是目前亟需解决的问题。

技术实现思路

1、本发明的目的在于提供一种大规模量子芯片谐振腔的设计方法及量子处理器,以解决现有技术中的缺陷与不足,本发明可减少大规模量子芯片谐振腔的设计耗时,提高设计效率及降低设计成本。

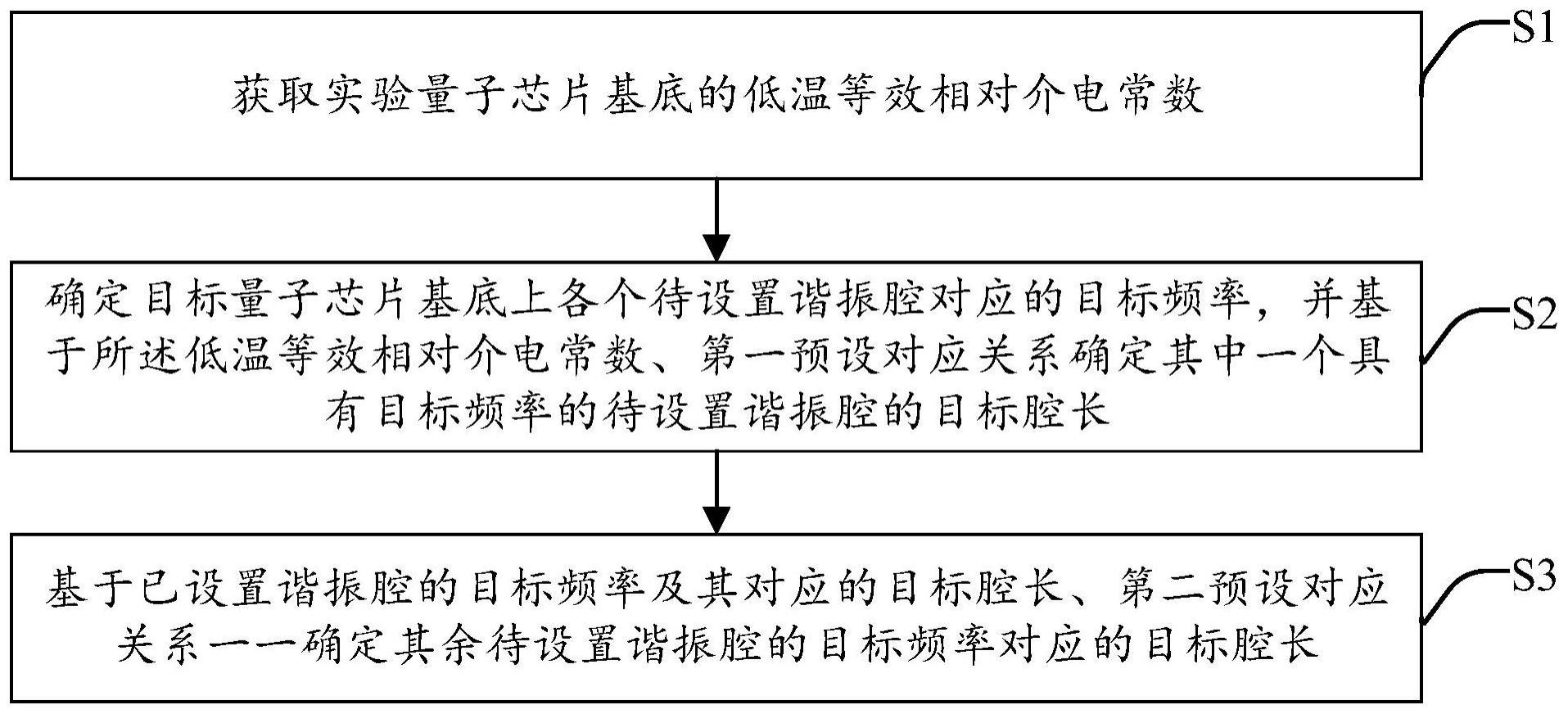

2、为实现上述目的,第一方面,本发明提供了一种大规模量子芯片谐振腔的设计方法,所述谐振腔由共面波导传输线组成,包括:

3、获取实验量子芯片基底的低温等效相对介电常数;其中,所述低温等效相对介电常数为所述实验量子芯片基底在低温环境下的固定参数,所述低温环境为所述量子芯片的工作环境;

4、确定目标量子芯片基底上各个待设置谐振腔对应的目标频率,并基于所述低温等效相对介电常数、第一预设对应关系确定其中一个具有目标频率的待设置谐振腔的目标腔长;其中,所述第一预设对应关系是所述谐振腔的频率及其对应的腔长、量子芯片基底的介电常数之间的关系;

5、基于已设置谐振腔的目标频率及其对应的目标腔长、第二预设对应关系一一确定其余待设置谐振腔的目标频率对应的目标腔长,其中,所述第二预设对应关系是两个不同所述谐振腔的频率及其对应的腔长之间关系。

6、可选的,所述获取实验量子芯片基底的低温等效相对介电常数,具体包括:

7、获取实验量子芯片的谐振腔的平均测量频率及其对应的平均测量腔长;

8、基于所述平均测量频率及其对应的平均测量腔长、第一预设对应关系获取所述实验量子芯片的低温等效相对介电常数。

9、可选的,所述基于已设置谐振腔的目标频率及其对应的目标腔长、第二预设对应关系一一确定其余待设置谐振腔的目标频率对应的目标腔长,具体包括:

10、基于已设置谐振腔的目标频率及其余待设置谐振腔的目标频率分别确定其余待设置谐振腔的目标频率与所述已设置谐振腔的目标频率的差值;

11、分别基于其余待设置谐振腔的目标频率与所述已设置谐振腔的目标频率的差值、第二预设对应关系一一确定其余待设置谐振腔的目标腔长与所述已设置谐振腔的目标腔长的差值;

12、基于已设置谐振腔的目标腔长、其余待设置谐振腔的目标腔长与所述已设置谐振腔的目标腔长的差值分别确定其余待设置谐振腔的目标腔长。

13、可选的,所述第一预设对应关系具体为:

14、

15、其中,f为量子芯片谐振腔的频率,λ为量子芯片谐振腔的腔长,εeff为量子芯片的介电常数,c为常数。

16、可选的,所述第二预设关系具体为:δf=k*δλ,其中,δf为两个目标频率的差值,δλ为两个目标频率对应的目标腔长的差值,k为常数。

17、可选的,所述目标量子芯片上设置有n个一一对应的且相互耦合的量子比特和谐振腔,n个所述谐振腔的目标频率均不相等,且任意相邻两个量子比特耦合连接的谐振腔的目标频率的差值大于预设阈值,其中,所述预设阈值根据所述谐振腔的加工精度设置。

18、可选的,n个顺次排列的谐振腔的目标频率等差设置。

19、可选的,相邻的耦合连接量子比特和谐振腔的耦合电容值不同,且间隔耦合连接量子比特和谐振腔的耦合电容值相同,所述第二预设关系与耦合连接量子比特和谐振腔的耦合电容相关。

20、第二方面,本发明提供了一种量子处理器,所述量子处理器上的谐振腔由如第一方面所述的大规模量子芯片谐振腔的设计方法设计。

21、与现有技术相比,本发明提供的一种大规模量子芯片谐振腔的设计方法及量子处理器,具有以下有益效果:在使用所述设计方法对大规模量子芯片谐振腔进行设置时,首先获取实验量子芯片基底的低温等效相对介电常数,然后确定所述目标量子芯片基底上各个待设置谐振腔对应的目标频率,并基于所述低温等效相对介电常数、第一预设对应关系确定其中一个具有目标频率的待设置谐振腔的目标腔长,最后基于已设置谐振腔的目标频率及其对应的目标腔长、第二预设对应关系一一确定其余待设置谐振腔的目标频率对应的目标腔长。本发明通过先修正目标量子芯片的基底参数,然后基于修正后的基底参数仿真出目标量子芯片上一个谐振腔的目标参数,再利于同一目标量子芯片上不同的谐振腔的目标参数满足特定的关系式计算出其他谐振腔的目标参数,大大缩短了设计时间、降低了设计成本且后续制造出的目标量子芯片谐振腔的实际参数与目标参数差值更小。

技术特征:

1.一种大规模量子芯片谐振腔的设计方法,所述谐振腔由共面波导传输线组成,其特征在于,包括:

2.如权利要求1所述的大规模量子芯片谐振腔的设计方法,其特征在于,所述获取实验量子芯片基底的低温等效相对介电常数,具体包括:

3.如权利要求1所述的大规模量子芯片谐振腔的设计方法,其特征在于,所述基于已设置谐振腔的目标频率及其对应的目标腔长、第二预设对应关系一一确定其余待设置谐振腔的目标频率对应的目标腔长,具体包括:

4.如权利要求1所述的大规模量子芯片谐振腔的设计方法,其特征在于,所述第一预设对应关系具体为:

5.如权利要求1所述的大规模量子芯片谐振腔的设计方法,其特征在于,所述第二预设关系具体为:δf=k*δλ,其中,δf为两个目标频率的差值,δλ为两个目标频率对应的目标腔长的差值,k为常数。

6.如权利要求5所述的大规模量子芯片谐振腔的设计方法,其特征在于,所述目标量子芯片上设置有n个一一对应的且相互耦合的量子比特和谐振腔,n个所述谐振腔的目标频率均不相等,且任意相邻两个量子比特耦合连接的谐振腔的目标频率的差值大于预设阈值,其中,所述预设阈值根据所述谐振腔的加工精度设置。

7.如权利要求6所述的大规模量子芯片谐振腔的设计方法,其特征在于,n个顺次排列的谐振腔的目标频率等差设置。

8.如权利要求5所述的大规模量子芯片谐振腔的设计方法,其特征在于,相邻的耦合连接量子比特和谐振腔的耦合电容值不同,且间隔耦合连接量子比特和谐振腔的耦合电容值相同,所述第二预设关系与耦合连接量子比特和谐振腔的耦合电容相关。

9.一种量子处理器,其特征在于,所述量子处理器上的谐振腔由如权利要求1-8任意一项所述的大规模量子芯片谐振腔的设计方法设计。

技术总结

本发明提供了一种大规模量子芯片谐振腔的设计方法及量子处理器,首先获取实验量子芯片基底的低温等效相对介电常数,然后确定目标量子芯片基底上各个待设置谐振腔对应的目标频率,并基于低温等效相对介电常数、第一预设对应关系确定其中一个待设置谐振腔的目标腔长,最后基于已设置谐振腔的目标频率及其对应的目标腔长、第二预设对应关系一一确定其余待设置谐振腔的目标频率对应的目标腔长。本发明通过先修正目标量子芯片的基底参数,然后仿真出一个谐振腔的目标参数,再利于不同谐振腔的目标参数满足特定的关系式计算出其他谐振腔的目标参数,大大缩短了设计时间、降低了设计成本且后续制造出的目标量子芯片谐振腔的实际参数与目标参数差值更小。

技术研发人员:李松,卜俊秀,李雪白,孔伟成

受保护的技术使用者:合肥本源量子计算科技有限责任公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!