具有多个命令子队列和对应的仲裁器的存储器控制器的制作方法

背景技术:

1、计算机系统通常使用廉价和高密度的动态随机存取存储器(dram)芯片作为主存储器。现今销售的大多数dram芯片与由联合电子设备工程委员会(jedec)发布的各种双倍数据速率(ddr)dram标准兼容。ddr dram通过提供各种低功率模式来提供高性能和低功率操作两者。

2、现代ddr存储器控制器维持队列以存储未决的存储器访问请求,从而允许这些控制器根据这些访问请求的生成或存储顺序来乱序地选取未决的存储器访问请求,以提高效率。例如,存储器控制器可从队列中检索对给定存储器存储列中的同一行的多个存储器访问请求,并基于检查页命中将这些访问请求连续地发出到存储器系统,以避免预充电当前行和激活另一行的开销。一些ddr存储器控制器采用单个命令队列(诸如64条目命令队列)和仲裁器,该仲裁器在所有64个命令队列条目中进行仲裁,每个条目都包含存储器访问请求。采用高密度动态随机存取存储器(诸如云计算服务器、台式计算机、膝上型计算机、移动设备、打印机和其他设备)的数据处理系统需要比以往任何时候都更高的性能能力。

技术实现思路

技术特征:

1.一种用于控制具有多个存储器通道的存储器系统的方法,包括:

2.根据权利要求1所述的方法,包括将存储器访问请求分类到不同的命令子队列中,使得所述第一命令子队列仅包括读请求,并且所述第二命令子队列仅包括写请求。

3.根据权利要求1所述的方法,包括:

4.根据权利要求1所述的方法,包括在所述第一命令子队列和所述第二命令子队列之间传送存储器访问请求,并且其中在所述第一命令子队列和所述第二命令子队列的每一者中选择所述存储器访问请求包括使用预定区段标准。

5.根据权利要求1所述的方法,其中选择优选存储器访问请求包括从所提供的来自所述第一命令子队列的第一存储器访问请求和来自所述第二命令子队列的第二存储器访问请求中选择最早的存储器访问请求。

6.一种具有存储器通道控制器的存储器控制器,所述存储器通道控制器包括:

7.根据权利要求6所述的存储器控制器,其中所述命令队列条目逻辑被配置为将存储器访问请求分类到不同的命令子队列中,使得所述第一命令子队列仅包括读请求,并且所述第二命令子队列仅包括写请求。

8.根据权利要求6所述的存储器控制器,其中所述命令队列条目逻辑被配置为将来自所述第一命令子队列的条目传送到所述第二命令子队列,并且其中所述命令队列条目逻辑操作地耦接到所述第一命令子队列和所述第二命令子队列,并且其中所述第一选择器操作地耦接到所述第一仲裁器和所述第二仲裁器两者。

9.根据权利要求6所述的存储器控制器,包括在所述第一仲裁器和所述第二仲裁器之间共享的共享时序逻辑和共享页表。

10.根据权利要求6所述的存储器控制逻辑,包括:

11.根据权利要求10所述的存储器控制器,包括命令队列条目逻辑,所述命令队列条目逻辑操作地耦接到所述第一命令子队列、所述第二命令子队列、所述第三命令子队列和所述第四命令子队列,并且操作以将存储器访问请求分类到不同的命令队列中,使得所述第一命令子队列和所述第二命令队列仅包括读请求,并且所述第三命令子队列和所述第四命令队列仅包括写请求。

12.根据权利要求6所述的存储器控制器,包括:

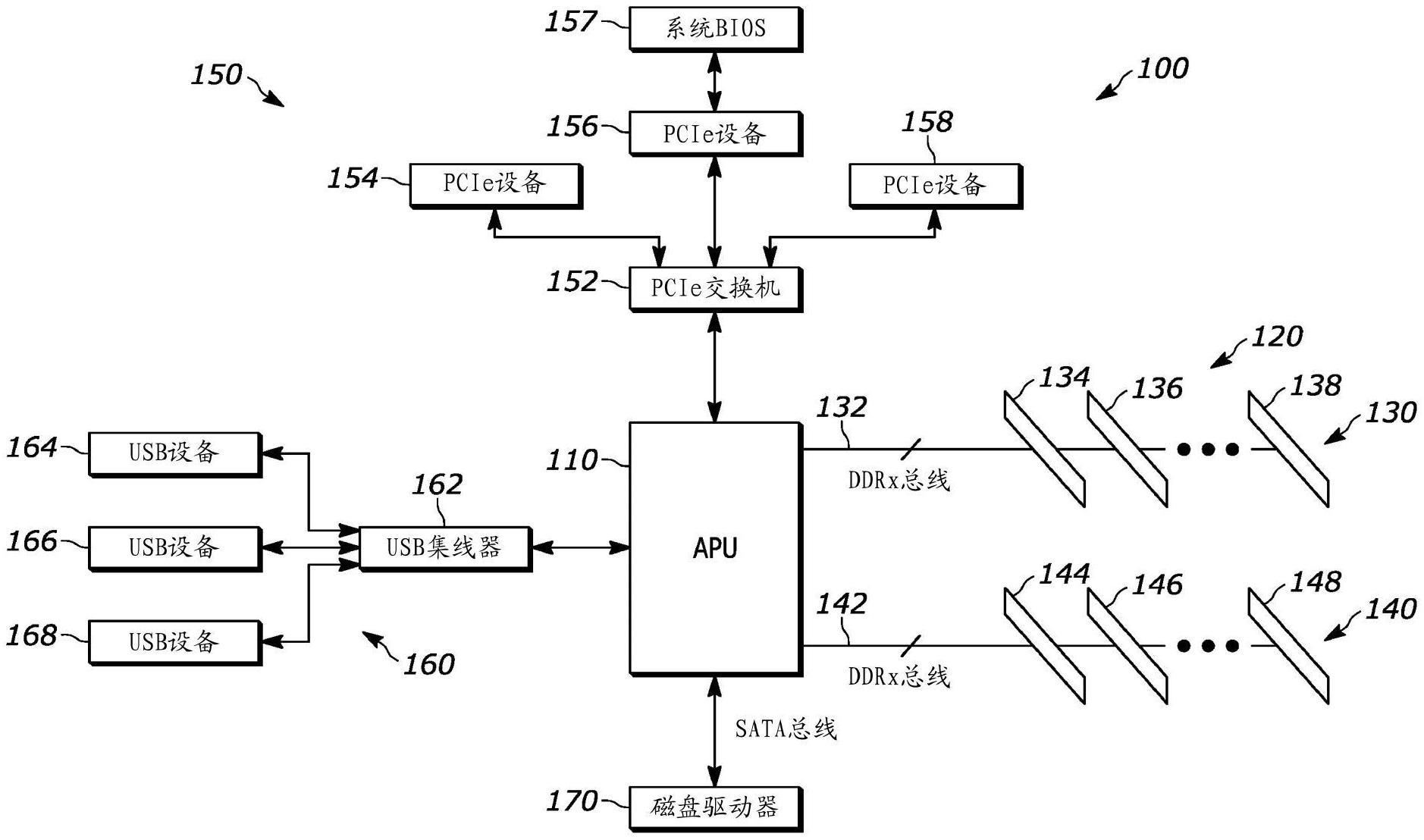

13.一种数据处理系统,包括:

14.根据权利要求13所述的数据处理系统,其中所述命令队列条目逻辑被配置为将存储器访问请求分类到不同的命令子队列中,使得所述第一命令子队列仅包括读请求,并且所述第二命令子队列仅包括写请求。

15.根据权利要求13所述的数据处理系统,其中所述命令队列条目逻辑被配置为将来自所述第一命令子队列的条目传送到所述第二命令子队列。

16.根据权利要求13所述的数据处理系统,包括在所述第一仲裁器和所述第二仲裁器之间共享的共享时序逻辑和共享页表。

17.根据权利要求13所述的数据处理系统,包括:

18.根据权利要求17所述的数据处理系统,包括命令队列条目逻辑,所述命令队列条目逻辑操作地耦接到所述第一命令子队列、所述第二命令子队列、所述第三命令子队列和所述第四命令子队列,并且操作以将存储器访问请求分类到不同的命令队列中,使得所述第一命令子队列和所述第二命令队列仅包括读请求,并且所述第三命令子队列和所述第四命令队列仅包括写请求。

19.根据权利要求13所述的数据处理系统,包括:

20.根据权利要求13所述的数据处理系统,包括地址生成器,所述地址生成器操作以将所接收的存储器访问请求中的每个存储器访问请求解码到所述存储器系统中的存储器设备的多个子通道的存储体、存储列和子通道中;并且

技术总结

本公开提供了一种存储器控制器,该存储器控制器包括存储器通道控制器,该存储器通道控制器使用命令队列和仲裁器对的多个组。每个仲裁器耦接到相应的命令队列,以根据预定标准从每个命令队列选择存储器访问命令。每个仲裁器基于该预定标准从每个命令队列中的存储器访问请求中独立地进行选择,并将所选择的存储器访问请求发送到用作第二级仲裁器的选择器,该第二级仲裁器将该请求发送到存储器子通道。

技术研发人员:詹姆斯·R·马格罗,凯达尔纳特·巴拉里斯南,布兰登·T·曼根

受保护的技术使用者:超威半导体公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!