具有多个op高速缓存管线的处理器的制作方法

背景技术:

1、为了提高效率和指令吞吐量,现代处理器通常支持指令处理并行性,其中在给定处理器周期期间,针对所接收的指令流的不同指令,处理器同时执行指定处理任务。例如,许多处理器采用同时执行针对不同指令的操作的多个执行单元,从而减少执行不同指令所需的总时间。然而,在处理器的执行阶段之前实现并行性会带来额外的挑战。一些处理器采用同时解码多个指令的解码单元,但电路面积和功耗注意事项限制了这些解码单元的大小和效率。

技术实现思路

技术特征:

1.一种方法,包括:

2.根据权利要求1所述的方法,其中选择所述第一op高速缓存管线还包括:基于与所述多个op高速缓存管线相关联的操作流标准来选择所述第一op高速缓存管线。

3.根据权利要求2所述的方法,其中所述操作流标准包括与在所述处理器处执行的至少一个线程相关联的服务质量。

4.根据权利要求2所述的方法,其中所述操作流标准指示:针对多个时间片中的每个时间片,将多个执行线程中的哪一线程分配给所述多个op高速缓存管线。

5.根据权利要求2所述的方法,其中所述操作流标准包括在所述选择之前提供给所述第一op高速缓存管线的预测窗口的数目。

6.根据权利要求5所述的方法,其中所述操作流标准包括预期待提供给所述多个op高速缓存管线中的每个管线的预测窗口的最小数目。

7.根据权利要求5所述的方法,其中所述操作流标准包括预期待提供给所述多个op高速缓存管线中的每个管线的预测窗口的最大数目。

8.根据任一前述权利要求所述的方法,其中所述多个op高速缓存管线中的每个管线包括所述处理器的op高速缓存的不同读取端口。

9.根据任一前述权利要求所述的方法,还包括:

10.根据任一前述权利要求所述的方法,其中选择所述第一op高速缓存管线还包括:基于所述第一分支预测来选择所述第一op高速缓存管线。

11.一种方法,包括:

12.一种处理器,包括:

13.根据权利要求12所述的处理器,其中所述控制模块用以基于与所述多个op高速缓存管线相关联的操作流标准来选择所述第一op高速缓存管线。

14.根据权利要求13所述的处理器,其中所述操作流标准包括分配给所述第一op高速缓存管线的第一操作量。

15.根据权利要求14所述的处理器,其中所述操作流标准包括分配给所述多个op高速缓存管线中的第二op高速缓存管线的第二操作量。

16.根据权利要求15所述的处理器,其中所述操作流标准包括在所述选择之前提供给所述第一op高速缓存管线的预测窗口的数目。

17.根据权利要求16所述的处理器,其中所述操作流标准包括预期待提供给所述多个op高速缓存管线中的每个管线的预测窗口的最小数目。

18.根据权利要求16所述的处理器,其中所述操作流标准包括预期待提供给所述多个op高速缓存管线中的每个管线的预测窗口的最大数目。

19.根据权利要求17所述的处理器,其中所述多个op高速缓存管线中的每个管线包括所述op高速缓存的不同读取端口。

20.根据任一前述权利要求所述的处理器,还包括:

技术总结

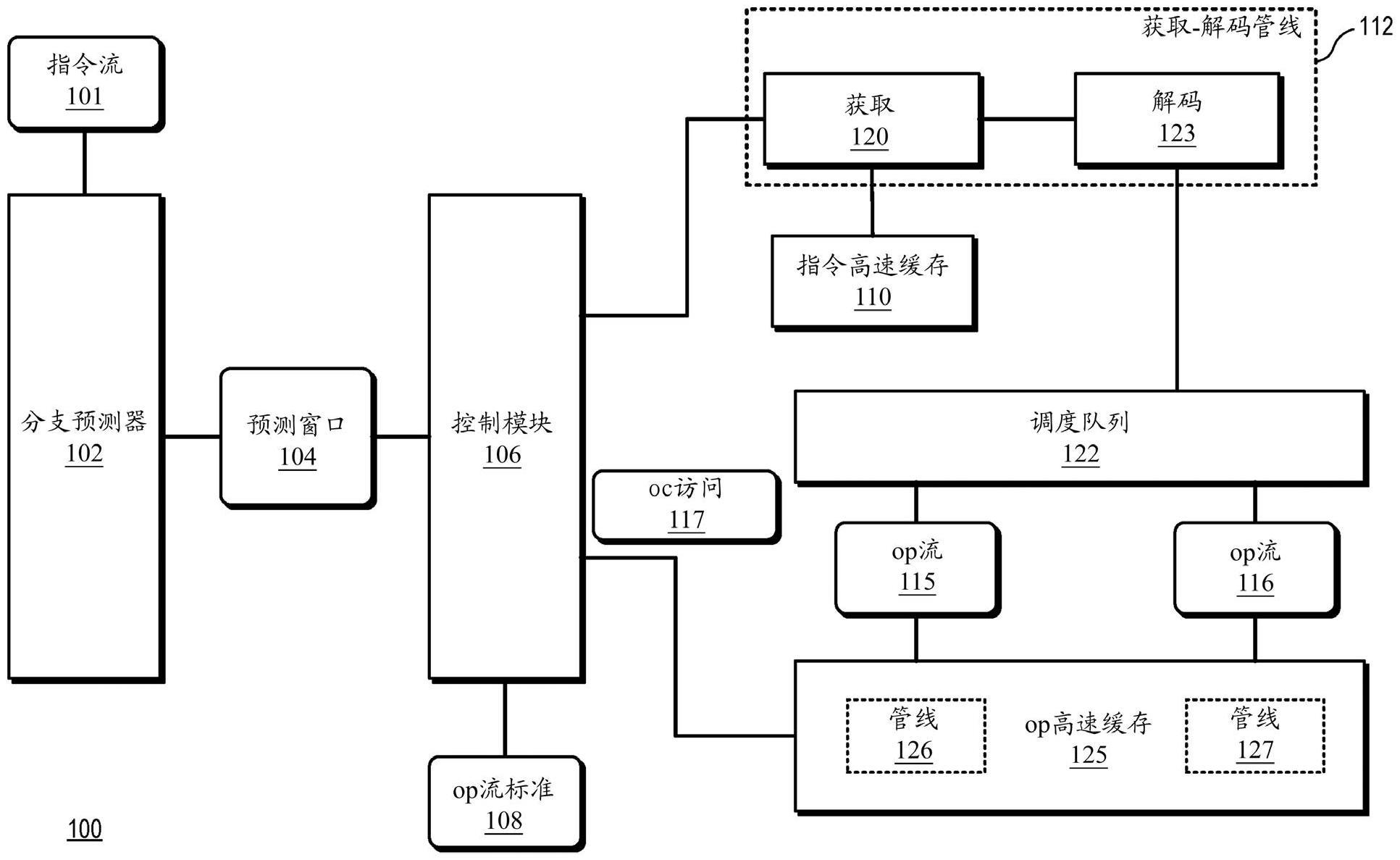

本发明提供了一种处理器,该处理器采用多个op高速缓存管线以同时将先前解码的操作提供给指令管线的调度级。响应于在处理器处接收到第一分支预测,该处理器基于该第一分支预测来选择该处理器的该多个op高速缓存管线中的第一op高速缓存管线;以及经由所选的第一op高速缓存管线,将与该第一分支预测相关联的第一组操作提供给调度队列。

技术研发人员:罗伯特·B·科恩,林子伟,安东尼·J·比贝尔,苏德赫森·卡莱瑟万,詹姆斯·莫斯曼

受保护的技术使用者:超威半导体公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!