具有低延迟安全HMB的无DRAMSSD的制作方法

本公开的各方面整体涉及使用安全主机存储器缓冲区(hmb)和低延迟操作的数据存储设备和相关方法。在一个方面,数据存储设备使用同时的存储器感测操作和有效性检查操作来促进低延迟。相关领域的描述主机设备的主机存储器缓冲区(hmb)与数据存储设备诸如固态驱动器(ssd)结合使用。hmb是主机设备内的专用存储位置。主机设备为数据存储设备提供hmb以根据需要使用。主机设备不控制数据存储设备对hmb的操作。主机设备仅控制对hmb的访问。因此,主机设备有时可阻止对hmb的访问。hmb可以用作数据存储设备的除位于控制器内的dram以外的附加存储装置。hmb可经受安全攻击,诸如网络攻击,包括重放攻击和/或回放攻击。此类攻击可暴露主机设备并影响性能。然而,保护主机设备的hmb免受此类攻击的努力可导致延迟,诸如4μsec(微秒)或更多的延迟。因此,本领域需要在促进延迟降低和性能增强的同时实用且简单地保护hmb的数据存储设备。

背景技术:

技术实现思路

1、本公开的各方面整体涉及使用安全主机存储器缓冲区和低延迟操作的数据存储设备和相关方法。在一个方面,数据存储设备的耦接到一个或多个存储器设备的控制器被配置为从主机设备获取命令,以及响应于来自主机设备的命令而从主机设备的主机存储器缓冲区(hmb)获取入口数据。hmb用于取代控制器中的dram,使得数据存储设备无dram。在一个实施方案中,入口数据包括逻辑到物理(l2p)地址。控制器还被配置为使用入口数据从一个或多个存储器设备获取读取数据,在从一个或多个存储器设备获取读取数据的同时对从hmb获取的入口数据进行有效性检查,以及将有效性结果数据传输到主机设备。

2、在一个实施方案中,数据存储设备包括一个或多个存储器设备和耦接到该一个或多个存储器设备的控制器,其中控制器无dram。控制器被配置为从主机设备获取命令,并且主机设备包括主机存储器缓冲区(hmb)。控制器被配置为响应于来自主机设备的命令而从hmb获取入口数据。控制器被配置为使用入口数据从一个或多个存储器设备获取读取数据。控制器被配置为在从一个或多个存储器设备获取读取数据的同时对从hmb获取的入口数据进行有效性检查,以及将有效性结果数据传输到主机设备。

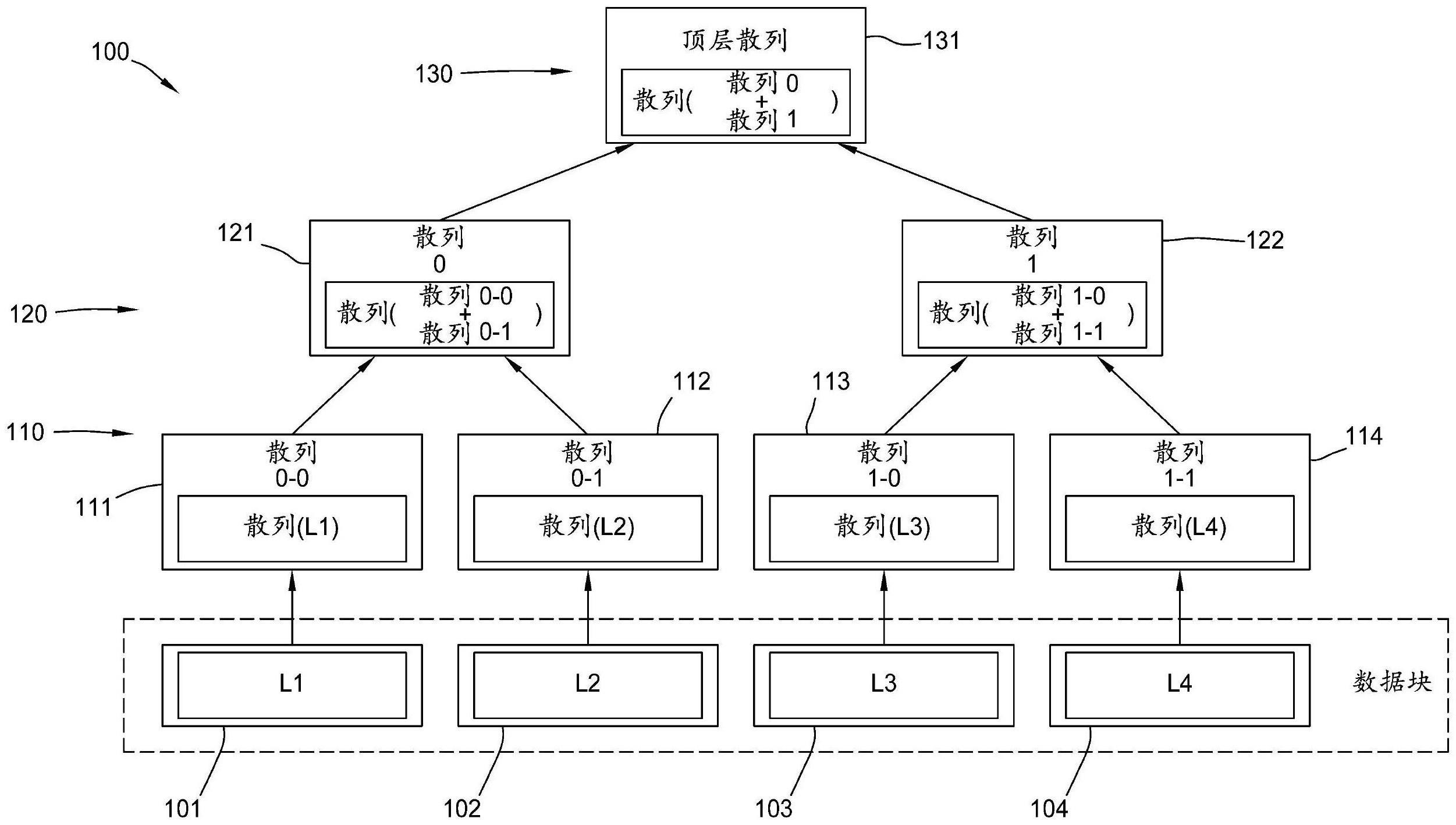

3、在一个实施方案中,数据存储设备包括一个或多个存储器设备和耦接到该一个或多个存储器设备的控制器,其中控制器无dram。控制器被配置为从主机设备获取命令。主机设备包括主机存储器缓冲区(hmb),并且hmb包括具有多个散列的默克尔树。控制器被配置为响应于来自主机设备的命令而从hmb获取入口数据。控制器被配置为使用入口数据从一个或多个存储器设备获取读取数据。控制器被配置为在从一个或多个存储器设备获取读取数据的同时对从hmb获取的入口数据进行有效性检查。有效性检查包括将多个散列中的顶层散列的签名与存储在控制器内的存储签名进行比较,以及确定签名与存储签名相同还是不同。

4、在一个实施方案中,数据存储设备包括存储器装置和控制器,其中控制器无dram,并且其中控制器被配置为从主机设备获取命令,并且主机设备包括主机存储器缓冲区(hmb);响应于来自主机设备的命令而从hmb获取入口数据;使用入口数据从一个或多个存储器设备获取读取数据;在从一个或多个存储器设备获取读取数据的同时对从hmb获取的入口数据进行有效性检查;以及将有效性结果数据传输到主机设备。

技术特征:

1.一种数据存储设备,所述数据存储设备包括:

2.根据权利要求1所述的数据存储设备,其中所述hmb包括具有多个散列的默克尔树,并且所述有效性检查包括:

3.根据权利要求2所述的数据存储设备,其中如果所述签名与所述存储签名相同,则传输到所述主机设备的所述有效性结果数据包括所述读取数据。

4.根据权利要求2所述的数据存储设备,其中如果所述签名与所述存储签名不同,则传输到所述主机设备的所述有效性结果数据包括垃圾数据。

5.根据权利要求2所述的数据存储设备,其中所述控制器被进一步配置为向所述主机设备发布完成消息。

6.根据权利要求5所述的数据存储设备,其中如果所述签名与所述存储签名相同,则所述完成消息包括有效通知。

7.根据权利要求5所述的数据存储设备,其中如果所述签名与所述存储签名不同,则所述完成消息包括错误通知。

8.根据权利要求2所述的数据存储设备,其中从所述一个或多个存储器设备获取所述读取数据包括在确定所述签名与所述存储签名相同还是不同之前,将感测请求发送到所述一个或多个存储器设备。

9.根据权利要求1所述的数据存储设备,其中所述一个或多个存储器设备是一个或多个nand设备。

10.一种数据存储设备,所述数据存储设备包括:

11.根据权利要求10所述的数据存储设备,其中所述控制器包括:

12.根据权利要求11所述的数据存储设备,其中从所述一个或多个存储器设备获取所述读取数据包括所述控制路径将感测请求发送到所述一个或多个存储器设备。

13.根据权利要求11所述的数据存储设备,其中所述主机接口模块执行所述有效性检查。

14.根据权利要求11所述的数据存储设备,其中所述dma被配置为将向所述主机设备传输有效性结果数据的指令发送到所述主机接口模块。

15.根据权利要求14所述的数据存储设备,其中所述dma被进一步配置为将向所述主机设备发布完成消息的指令发送到所述主机接口模块。

16.一种数据存储设备,所述数据存储设备包括:

17.根据权利要求16所述的数据存储设备,其中进行所述入口数据的所述有效性检查包括:

18.根据权利要求16所述的数据存储设备,其中所述控制器包括耦接到直接存储器访问(dma)的主机接口模块。

19.根据权利要求18所述的数据存储设备,其中所述dma耦接到纠错模块和闪存接口模块(fim)。

20.根据权利要求18所述的数据存储设备,其中进行所述有效性检查与获取读取数据同时执行。

技术总结

本公开的各方面整体涉及使用安全主机存储器缓冲区和低延迟操作的数据存储设备和相关方法。在一个方面,控制器被配置为从主机设备获取命令,以及响应于来自主机设备的命令而从主机设备的主机存储器缓冲区(HMB)获取入口数据。HMB用于取代控制器中的DRAM,使得数据存储设备无DRAM。在一个实施方案中,入口数据包括逻辑到物理(L2P)地址。控制器还被配置为使用入口数据从一个或多个存储器设备获取读取数据,在从一个或多个存储器设备获取读取数据的同时对从HMB获取的入口数据进行有效性检查,以及将有效性结果数据传输到主机设备。

技术研发人员:S·班尼斯提

受保护的技术使用者:西部数据技术公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!