一种融合通讯接口的芯片复位设计方法与流程

1.本发明涉及一种融合通讯接口的芯片复位设计方法,用于指导芯片复位系统设计。

背景技术:

2.随着物联网的发展,芯片业务的逐渐扩大,芯片已经运用在各个行业,需求量也十分巨大。由于芯片应用广阔,因此工作场景越来越复杂。芯片在实际应用时容易受到外界的干扰而导致芯片死机,程序无法运行,无法给主机响应,此时需要进行重启才能运行否则便引起功能瘫痪,有时甚至会造成严重事故。即使在正常应用中芯片也有定期复位需求,而采用软件方式效率低下。

3.目前主流芯片存在四种复位方式:第一种通过外部引脚拉低复位芯片,第二种芯片通过断电方式进行上电和下电复位,第三种通过协议发送软指令进行芯片复位,第四种,在硬件通讯协议层进行复位,但是无法复用其他接口。

4.上述的方法,属于传统方法,存在以下缺点:

5.1)、需要占用额外主机引脚复位芯片,并且pcb设计复杂度;

6.2)、需要使用额外电源芯片以及主机控制引脚,增加pcb设计成本;

7.3)、需要和协议配合使用,增加软件设计难度;

8.4)单一接口的复位,当前接口的复位不能应用于其他接口,例如usb接口复位无法应到串口通讯过程中。

9.从上述问题可以看出,需要设计一种方法既能灵活有效复位芯片且同时降低pcb设计成本。

10.根据上述问题,本文提出一种融合通讯接口的芯片复位设计方法。该方法主要以下三方面:首先,独立复位模块可以监听任意接口信号时序;其次,独立复位模块功能可通过配置方式打开和关闭;第三,独立复位模块可支持多种形式的时序判断(具体由设计者选择方案并设计实现)

技术实现要素:

11.本发明的方法解决问题是:改善现有芯片应用上的不足,提供了一种融合通讯接口的芯片复位设计方法,可简化芯片应用环境,降低pcb设计成本。

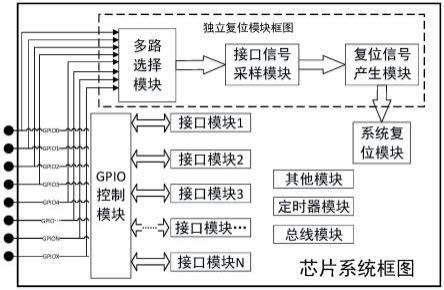

12.本发明的方法解决方案(如图1所示):

13.首先:通过芯片对多路选择模块进行配置,多路选择模块选择需要监听的接口信号并将信号传递给接口信号采样模块;

14.其次:接口信号采样模块主要分为信号处理模块和信号采样模块两部分,信号处理模块对传递过来的信号进行滤波处理,处理完成后再交给信号采样模块进行采样,采样后进行初步筛选判断并传递给复位信号产生模块;

15.再次:复位信号产生模块主要分为信号时序判断模块、复位信号配置模块,复位信

号输出模块。首先对复位信号时序模块对传递过来的信号进行时序判断,若符合特殊时序则产生有效信号给复位信号配置模块,复位信号根据系统的配置信息产生符合芯片系统能识别的信号(上升沿、下降沿、高电平,低电平等)传递给复位信号输出模块,由复位信号输出模块决定是否传递给系统复位模块;

16.最后:系统复位模块对芯片进行复位。

17.本发明与现有技术相比的优点在于:

18.(1)简化芯片外围的电路设计,降低pcb设计成本。

19.(2)软件无需复杂设计,对当前无影响。

20.(3)对芯片硬件接口通讯功能无影响。

21.(4)芯片所支持的gpio端口均可作为复位信号,保证通讯接口复用多个gpio的情况下均能产生有效复位。

附图说明

22.图1为本发明的整体设计框图;

23.图2为本发明的多路选择模块示意框图;

24.图3为本发明的接口信号采样模块示意框图;

25.图4为本发明的复位信号产生模块示意框图;

具体实施方式

26.下面以一个示例来说明具体实施方式(整体框图如图1所示),以某国外芯片的spi通讯接口作为说明,其主要由cs、clk、miso、mosi四根信号线组成,示例:正常工作clk=1mhz,空闲状态下clk停留在高电平状态,cs低电平有效,mosi由matser传送给slave的信号,miso为slave传送给master的信号,接口复用关系为cs复用gpio0,clk复用gpio1,miso复用gpio2,mosi复用gpio3。

27.由于clk工作频率为1mhz,且空闲状态时为高电平,理论上分析clk长期处于低电平状态不会超过1ms。此时可以监听clk上的信号,如果超过1ms以上则认为主机对芯片发出了复位需求,芯片启动复位。

28.芯片配置多路选择模块,如图2所示,将gpio1管脚上的信号选通,通过选择器输出到接口信号采样模块,其他管脚信号不选通。接口信号采样模块示意框图如图3所示,信号处理模块对采集到的gpio1管脚的信号进行滤波,如果滤波信号判断是毛刺,则滤除不传递有效信号给信号采样模块,否则滤波后的信号传递给信号采样模块进行采样。信号采样模块将采样后的信号传递给复位信号产生模块,复位信号产生模块示意框图如图4所示,信号时序判断模块判断接收到超过1ms的低电平,根据复位信号配置模块已配置的低电平超过1ms且产生过上升沿和下降沿变化则为有效复位,复位信号输出模块输出有效复位信号,启动芯片系统复位。

29.做好上述设计工作,使用流程如下:

30.第一步,芯片上电,芯片配置多路选择模块,选择监听gpio1信号;

31.第二步,芯片配置接口信号处理模块,配置信号滤波处理方式和采样频率;

32.第三步,芯片配置复位信号产生模块,配置复位信号为上升沿触发,并使能复位信

号输出;

33.第四步,芯片启动独立复位模块;

34.第五步,芯片开始工作和主机进行通讯,工作过程中,由于clk空闲状态处于高电平,通讯状态下1mhz的时钟产生的低电平时间仅有1us,达不到触发条件,因此独立复位模块不会产生复位信号。

35.第六步,当主机发现芯片功能异常或者无响应时,主机在clk引脚上先拉低输出1.5ms的低电平再拉高,然后等待芯片重启。

36.第七步,此时独立复位模块监测到clk上的异常电平,并产生有效复位信号,芯片产生系统复位。

37.第八步,主机和芯片正常通讯。

38.本发明说明书中未作详细描述的内容属本领域技术人员的公知技术。

技术特征:

1.一种融合通讯接口的芯片复位设计方法,其特征在于,主要包括:1)接口信号采样模块独立设计与通讯接口分开避免信号耦合,接口信号采样模块监听期间不对通讯接口工作产生影响;2)多路选择模块保证使用一个独立的接口信号采样模块可以覆盖芯片所支持的所有gpio端口,通过多路选择方式将任意一个接口信号传递给接口信号采样模块;3)复位信号产生模块对接口信号采样模块传送过来的信号进行时序判断,产生有效的复位信号传递给芯片的系统复位模块用于复位芯片;4)通讯接口和外部复位融合,减少外围电路设计和降低芯片开发成本。2.根据权利要求1所述的一种融合通讯接口的芯片复位设计方法,其特征在于,所述步骤1中的接口信号采样模块独立设计,保证不影响通讯接口的工作且采样信号经过滤波处理,不会导致复位信号产生模块出现误判。3.根据权利要求1所述的一种融合通讯接口的芯片复位设计方法,其特征在于,所述步骤2多路选择模块覆盖芯片所支持的gpio端口,并且可以任选其一,保证通讯接口复用多个gpio的情况下均可以被采集信号。4.根据权利要求1所述的一种融合通讯接口的芯片复位设计方法,其特征在于,复位信号产生模块的时序判断可以采用多种方式,由用户结合应用场景自定义。5.根据权利要求1所述的一种融合通讯接口的芯片复位设计方法,其特征在于,通讯接口和外部复位融合,简化芯片外围电路设计。

技术总结

一种融合通讯接口的芯片复位方法,采用接口信号采样模块为独立模块设计,使用多路选择方式覆盖芯片的所有GPIO端口,通过可配置方式监听任意接口信号的时序信息并对其进行采样判断,输出有效复位信号给芯片产生系统复位。通过该方法将外部复位和通讯接口统一,且任意GPIO端口信号可配置为复位信号,有效简化外围电路设计和降低板级成本。本专利仅提供一种原型设计方法,并不局限于开发者使用何种具体方式和工具实现,也不局限于芯片以何种接口运行。行。行。

技术研发人员:董攀 王哲 王西国

受保护的技术使用者:北京中电华大电子设计有限责任公司

技术研发日:2022.08.15

技术公布日:2022/11/25

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1