处理器和算术处理方法与流程

本发明涉及处理器和处理方法。处理器有时也可以称为算术处理单元、处理单元等。算术处理方法有时也可以简单地称为处理方法。

背景技术:

1、安装在诸如中央处理单元(cpu)等的处理器中的缓存保存存储在外部存储器中的数据的一部分。当缓存保存从cpu发出的读取访问请求的目标数据并且发生缓存命中时,缓存将保存在缓存中的数据传输至cpu核等,而不向外部存储器发出读取访问请求。因此,提高了数据访问效率,并且提高了cpu的处理性能。

2、例如,与cpu一起设置在半导体设备中并且控制外部存储器的存储器控制器包括分别与设置在外部存储器中的多个存储体中的每一个对应的存储体缓存,例如如在日本公开特许公报第2005-339348号所提出的。处理器中设置的2级缓存包括多个可独立访问的存储块,例如如在日本公开特许公报第2006-507602号所提出的。当针对普通存储体进行连续访问时,包括多个普通存储体和多个缓存存储体的存储器将从选定的普通存储体输出的数据移动至缓存存储体,例如如在日本公开特许公报第2004-55112号所提出的。

3、近来,已经提出了能够执行单指令多数据(simd)算术指令的处理器来并行执行向量运算等。这种类型的处理器可以执行具有各种数据尺寸的simd算数指令。例如,当使用具有连续地址和作为缓存存储体的数据宽度的一半的数据尺寸的多个数据进行simd操作时,可能发生针对单个存储体的多个读取访问请求的冲突。在这种情况下,读取访问请求被连续地供应至存储体,并且访问目标数据被连续地从存储体读取。由于在读取所有访问目标数据之后执行simd操作,因此simd操作的执行时间被延迟,从而降低了计算效率。

技术实现思路

1、根据一个方面,本发明的一个目的是:即使当多个读取访问请求的读取目标数据分别是保存在存储体中的第一数据中包括的多个第二数据时,也减少读取多个第二数据的延迟。

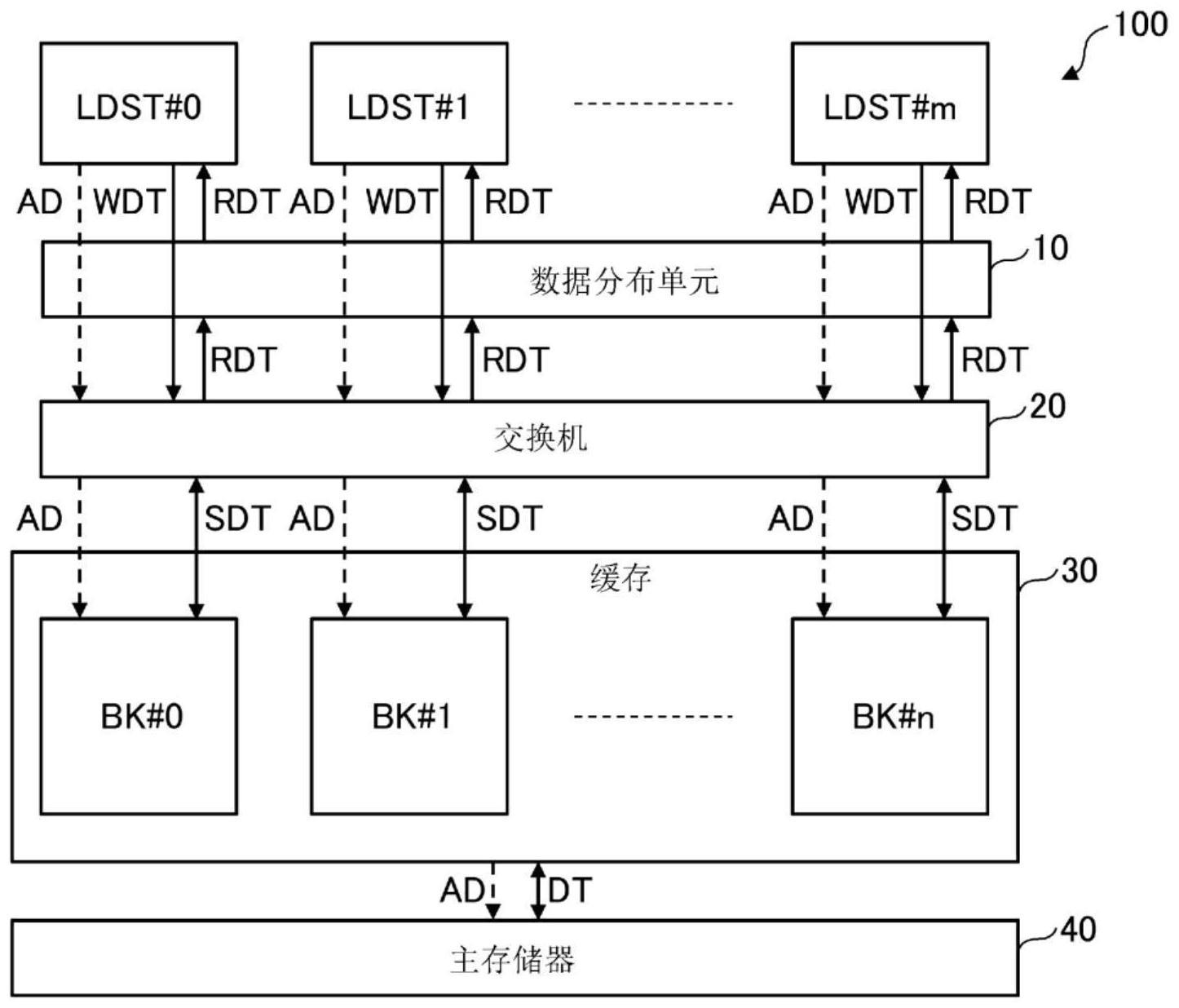

2、根据实施方式的一个方面,一种处理器包括:多个请求发出单元,所述多个请求发出单元分别被配置成发出针对存储装置的读取访问请求;缓存,该缓存包括多个存储体,所述多个存储体分别能够保存从读取自存储装置的数据划分的第一数据;交换机,该交换机被配置成将多个请求发出单元和多个存储体互连;以及数据分布单元,该数据分布单元设置在多个请求发出单元与交换机之间,其中,在从多个请求发出单元发出的多个读取访问请求的读取目标数据中的每一个是包括在第一数据中的多个第二数据中的一个第二数据的情况下,交换机将多个读取访问请求中的一个读取访问请求输出至作为读取目标的存储体,从存储体读取的包括多个第二数据的第一数据被输出至数据分布单元,并且数据分布单元将从接收自交换机的第一数据划分的多个第二数据中的每个第二数据并行输出至作为读取访问请求的发起者的请求发出单元。

3、本发明的目的和优点将借助于权利要求中特别指出的元素和组合来实现和获得。

4、应当理解,前述一般描述和以下详细描述两者是示例性的和说明性的,而非是对所要求保护的本发明的限制。

技术特征:

1.一种处理器,包括:

2.根据权利要求1所述的处理器,其中,在符号扩展型读取访问请求的读取目标数据中的每一个是包括在所述第一数据中的所述多个第二数据中的一个第二数据的情况下,所述数据分布单元经由低位数据线将所述多个第二数据中的每个第二数据输出至作为所述读取访问请求的发起者的请求发出单元。

3.根据权利要求2所述的处理器,其中,在所述多个第二数据具有负值的情况下,所述数据分布单元将“1”输出至除输出具有所述负值的所述第二数据的低位数据线之外的高位数据线。

4.根据权利要求2所述的处理器,其中,所述数据分布单元将与非符号扩展型读取访问请求对应地从所述多个存储体中的一个存储体读取的所述第一数据输出至作为所述读取访问请求的发起者的请求发出单元,而不划分所述第一数据。

5.根据权利要求1至4中任一项所述的处理器,其中,

6.根据权利要求5所述的处理器,其中,

7.根据权利要求6所述的处理器,其中,在符号扩展型读取访问请求的读取目标数据是包括在所述第一数据中的所述多个第二数据的情况下,所述选择器将经由所述数据输入端口从所述交换机接收的所述第一数据中包括的所述低位数据和所述高位数据输出至与作为所述读取访问请求的发起者的请求发出单元对应的所述数据输出端口的低位侧。

8.根据权利要求1至4中任一项所述的处理器,还包括:

9.一种在处理器中实现的算术处理方法,所述处理器包括:多个请求发出单元,所述多个请求发出单元分别用于发出针对存储装置的读取访问请求;缓存,所述缓存包括多个存储体,所述多个存储体分别能够保存从读取自所述存储装置的数据划分的第一数据;交换机,所述交换机用于将所述多个请求发出单元和所述多个存储体互连;以及数据分布单元,所述数据分布单元设置在所述多个请求发出单元与所述交换机之间,所述算术处理方法包括:

10.根据权利要求9所述的算术处理方法,其中,在符号扩展型读取访问请求的读取目标数据中的每一个是包括在所述第一数据中的所述多个第二数据中的一个第二数据的情况下,由所述数据分布单元进行的输出经由低位数据线将所述多个第二数据中的每个第二数据输出至作为所述读取访问请求的发起者的请求发出单元。

11.根据权利要求10所述的算术处理方法,其中,在所述多个第二数据具有负值的情况下,由所述数据分布单元进行的输出将“1”输出至除输出具有所述负值的所述第二数据的低位数据线之外的高位数据线。

12.根据权利要求10所述的算术处理方法,其中,由所述数据分布单元进行的输出将与非符号扩展型读取访问请求对应地从所述多个存储体中的一个存储体读取的所述第一数据输出至作为所述读取访问请求的发起者的请求发出单元,而不划分所述第一数据。

技术总结

一种处理器包括:发出单元,该发出单元用于向存储装置发出读取访问请求;缓存,该缓存包括存储体,该存储体能够保存从读取自存储装置的数据划分的第一数据;交换机,该交换机将发出单元和存储体互连;以及数据分布单元,该数据分布单元设置在发出单元与交换机之间。在从发出单元发出的读取访问请求的读取目标数据中的每一个是包括在第一数据中的第二数据之一的情况下,交换机将读取访问请求之一输出至作为读取目标的存储体,并且从存储体读取的第一数据被输出至数据分布单元。数据分布单元将从接收自交换机的第一数据划分的第二数据中的每一个并行输出至作为读取访问请求的发起者的发出单元。

技术研发人员:一场利幸,五岛正裕

受保护的技术使用者:富士通株式会社

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!